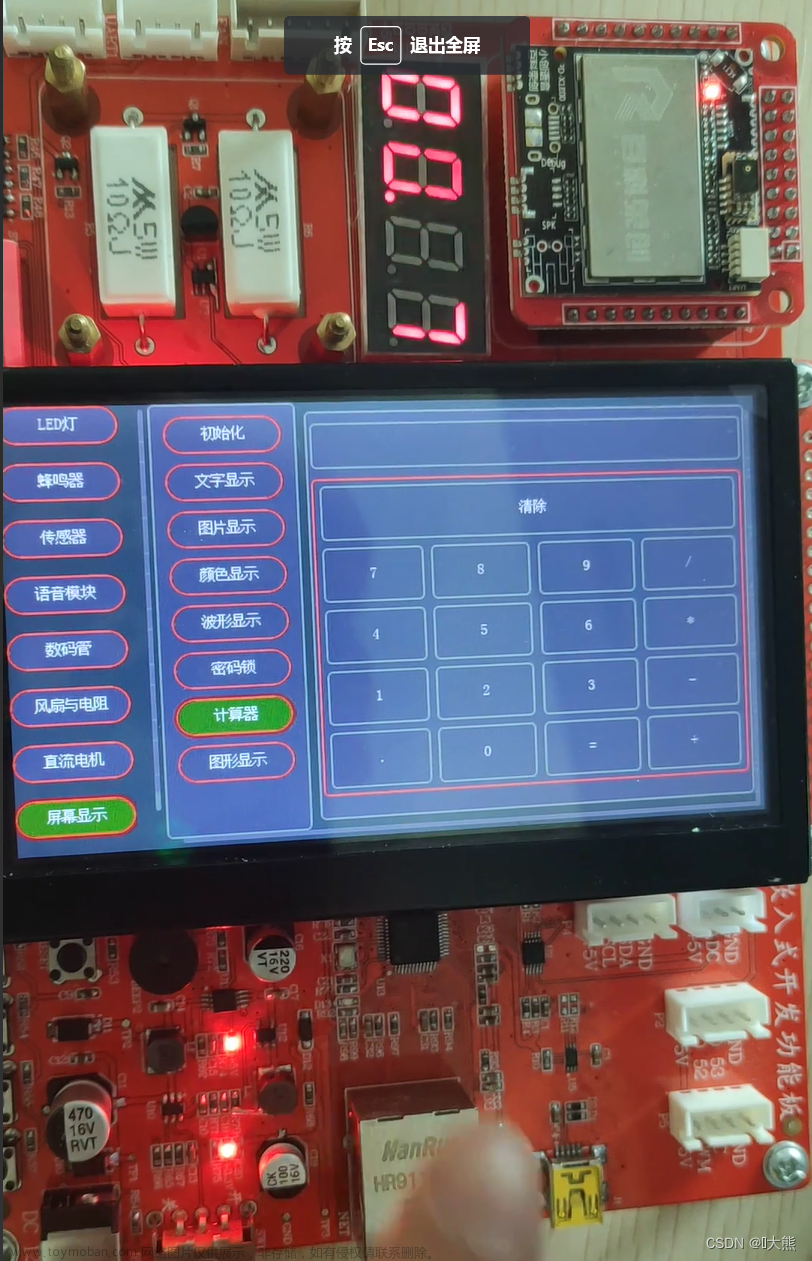

该实验为用verilog编写的一个运算系统,其功能是实现4位整数的加、减、乘、除运算。运算时通过矩阵键盘输入运算类型和运算所需要的数据,然后通过内部电路处理,将计算的结果送于数码管或LCD1602显示。

工程截图如下:

本设计分为两个子模块,按键输入和数码管输出。

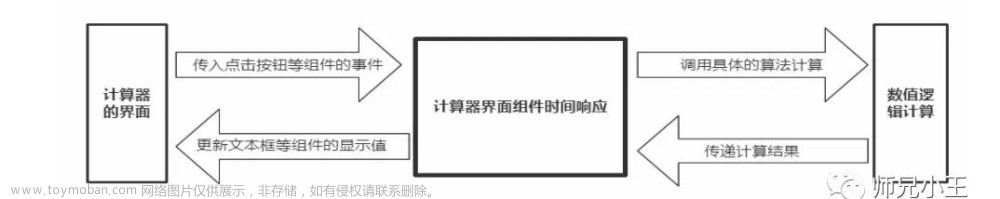

还有LCD1602控制器设计

LCD控制器代码:

module LCD_Controller ( // Host Side

iDATA,iRS,

iStart,oDone,

iCLK,iRST_N,

// LCD Interface

LCD_DATA,

LCD_RW,

LCD_EN,

LCD_RS );

// CLK

parameter CLK_Divide = 16;文章来源:https://www.toymoban.com/news/detail-792348.html

// Host Side

input [7:0] iDATA;

input iRS,iStart;

input iCLK,iRST_N;

output reg oDone;

// LCD Interface

output [7:0] LCD_DATA;

output reg LCD_EN;

output LCD_RW;

output LCD_RS;

// Internal Register

reg [4:0] Cont;

reg [1:0] ST;

reg preStart,mStart;文章来源地址https://www.toymoban.com/news/detail-792348.html

到了这里,关于verilog实现计算器设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!