本文是根据参考了网上多篇帖子和书籍,对于有关建立时间和保持时间知识点讲解的基础上进行归纳总结,如有错误敬请批评指正!

一、概念

建立时间和保持时间都是基于触发器而言,所以在了解建立时间和保持时间之前,需要对触发器进行分析,本文从D触发器(D-FF)结构原理上进行简述建立时间和保持时间,因为FPGA内部常用D触发器作为时序逻辑电路的记忆元件。

D触发器(D-FF):一种在时钟的上升沿(或下降沿)将输入信号的变化传送至输出的边沿触发器,如图1-1所示。x为不定态,即任何值。

| D | CLK | Q | QN |

|---|---|---|---|

| 0 | 时钟上升沿 | 0 | 1 |

| 1 | 时钟上升沿 | 1 | 0 |

| × | 0 | last Q | last QN |

| × | 1 | last Q | last QN |

图1-1 D触发器

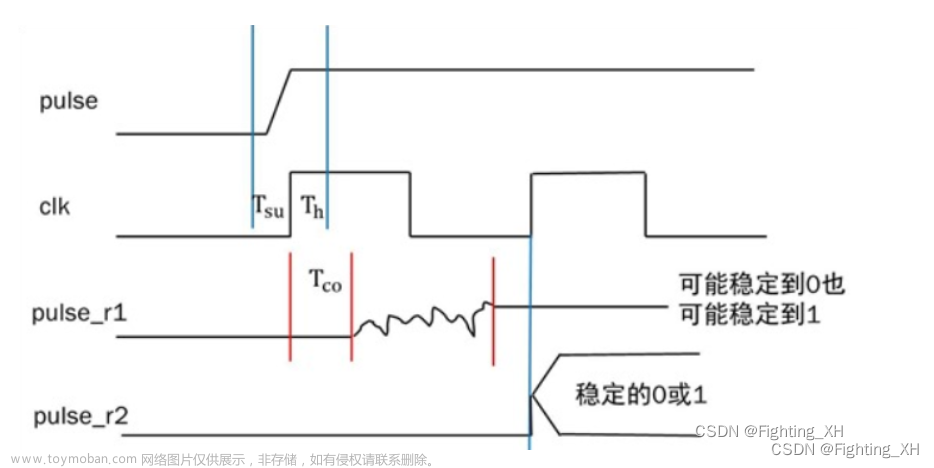

建立时间(Tsu:setup time):是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被稳定的打入触发器,Tsu就是指这个最小的稳定时间。

保持时间(Td:hold time):是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被稳定的打入触发器,Th就是指这个最小的保持时间。

二、D-FF的原理

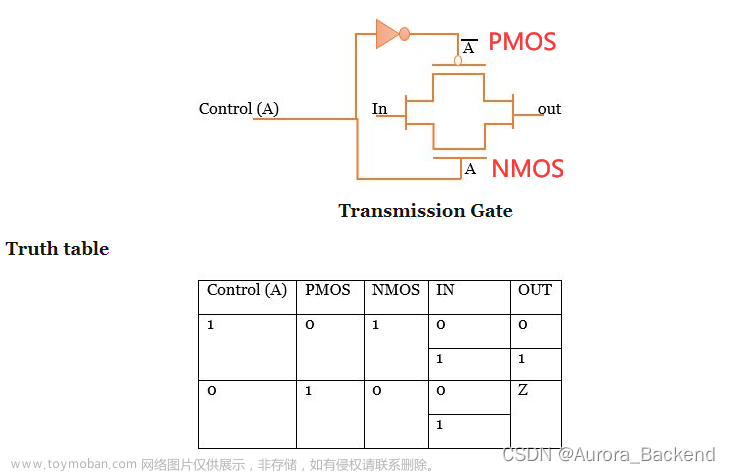

CMOS工艺下的D-FF结构如图1-2所示,先由两个传输门和两个反相器组成一个循环电路( 锁存器),再由前后两级锁存器按主从结构连接而成。这里的传输门起开关的作用,随着CLK的状态变化切换开关。只看输出的话,前级锁存器的值会将时钟输入的变化井然有序地传入后级锁存器。为了防止时钟信号变化时输入信号发生冒险,从而使稳定的输入信号进入前级锁存器,前级锁存器的时钟相位应该与产生输入信号的电路时钟反向。图1-3为D-FF的原理图。

图1-2 D-FF的电路结构图

图1-3 D-FF的原理

当CLK=0(主锁存器工作)时,位于前级的主锁存器将输人D的值保存进来,后级的从锁存器则维持上一时钟周期的数据。由于此时前级和后级反相器环路之间的传输门是关闭状态,所以前级的信号不会传到后级。当CLK=1 (从锁存器工作)时,前级反相器环路中保存的数报会传输到后级,同时输人D的信号会被隔离在外。此时如果前级反相器环路中的信号没有循环一圈以上,就会出现如图1-4所示的在0和1之间摇摆的中间电位,这就是所谓的亚稳态( metastable ) 。由于亚稳态时间比延迟时间长,在该阶段读取数据可能会引人错误,所以我们引入建立时间( setup time)来约束在时钟上升沿到来前,输入D保持稳定的时间。

当CLK=1时,如果输人D在传输门关闭前就发生变化,那么本该在下一周期读取的数据就会提前进入锁存器,从而引起反相器环路振荡或产生亚稳态。因此在CLK=1之后也需要输入D维持一定的时间,我们称之为保持时间( hold time )约束。

为了正确地从输人读取数据,并正确地将数据输出,FPGA 内所有的FF都要遵守建立时间和保持时间等时序上的约束。

图1-4 建立时间和保持时间

参考资料文章来源:https://www.toymoban.com/news/detail-792412.html

[1] FPGA原理和结构-天野英晴主编-赵谦译文章来源地址https://www.toymoban.com/news/detail-792412.html

到了这里,关于简述建立时间(setup time) 和 保持时间(hold time)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[静态时序分析简明教程(二)] 基础知识:建立时间、保持时间、违例修复及时序分析路径](https://imgs.yssmx.com/Uploads/2024/02/421728-1.png)