一、基本概述

TX-P01I83 是以 EPROM 作为存储器的 8 位单片机,专为多 IO 产品的应用而设计,例如遥控器、风扇/灯光控制或是 玩具周边等等。采用 CMOS 制程并同时提供客户低成本、高性能等显着优势。TX-P01I83 核心建立在 RISC 精简指 令集架构可以很容易地做编程和控制,共有 55 条指令。除了少数指令需要两个指令时钟,大多数指令都是一个指令时钟能完成,可以让用户轻松地以程序控制完成不同的应用。因此非常适合各种中低记忆容量但又复杂的应用。

在 I/O 的资源方面,TX-P01I83 有 6 根弹性的双向 I/O 脚,每个 I/O 脚都有单独的寄存器控制为输入或输出脚。而且 每一个 I/O 脚位都能相关的寄存器达成如上拉或下拉电阻或开漏(Open-Drain)输出。此外针对红外线摇控的产品方 面,TX-P01I83 内置了可选择频率的红外载波发射口。

在省电的模式下,如待机模式(Standby mode)与睡眠模式(Halt mode)中,有多个中断源可以触发来唤醒 TX-P01I83 进入正常操作模式(Normal mode)或慢速模式(Slow mode)来处理突发事件。

二、应用领域

在智能仪器仪表,智能照明,家电家居,玩具类应用于各个行业.单片机具有体积小、功耗低、控制功能强、扩展灵活、微型化和使用方便等优点,结合不同的电子产品功能,控制IO的输入输出,电平的高低,定时,中断,来实现产品的不同功能,自带C语言编译器,仿真器等开发工具。

TX-P01I83 有两组定时器,可用系统时钟当作一般的计时应用或者从外部讯号触发来计数。另外 TX-P01I83 提供一 组 8 位的 PWM 输出或者蜂鸣器输出,可用来驱动马达、LED、或蜂鸣器等等。

TX-P01I83 采用双时钟机制,高速振荡时钟或者低速振荡时钟都由内部 RC 振荡输入。在双时钟机制下,TX-P01I83 可选择多种工作模式如正常模式(Normal)、慢速模式(Slow mode)、待机模式(Standby mode)与睡眠模 式(Halt mode),可节省电力消耗,延长电池寿命。

三、产品特征

-

一个蜂鸣器输出(BZ1)。

-

38/57KHz红外线载波(IR)频率可供选择,同时载波之极性也可以通过寄存器选择。

-

内置上电复位电路(POR)。

-

内置低压复位功能(LVR)。

-

内置看门狗计时(WDT),可由配置字节(Configuration Word)控制开关。

-

双时钟机制,系统时钟可以随时切换高速振荡或者低速振荡。

-

高速振荡时钟:I_HRC (内部 1~20MHz高速RC振荡)

-

低速振荡时钟:I_LRC (内部 32KHz低速RC振荡)

-

四种工作模式可随系统需求调整电流消耗:正常模式(Normal mode)、慢速模式(Slow mode)、待机模式 (Standby mode)与睡眠模式(Halt mode)。

-

五种硬件中断:

-

Timer0 上溢中断。

-

宽广的工作电压:(指令时钟为 4 个CPU时钟,亦即 4T模式)

-

2.0V ~ 5.5V @系统时钟≦8MHz。

-

2.2V ~ 5.5V @系统时钟>8MHz。

-

宽广的工作温度:-40°C ~ 85°C。

-

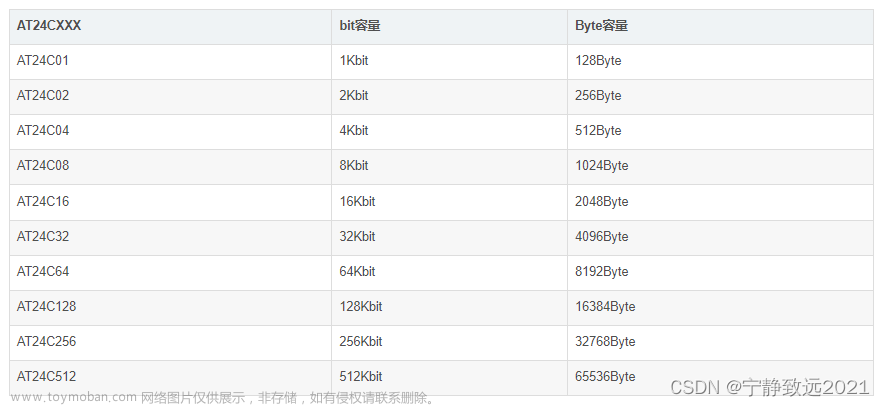

1Kx14 位的程序存储器空间。

-

48 字节的通用数据寄存器空间。

-

6 根可分别单独控制输入输出方向的I/O脚(GPIO)、PB[5:0]。

-

PB[3:0]可选择输入时使用内部下拉电阻。

-

PB[5:4]及PB[2:0]可选择内部上拉电阻或开漏输出(Open-Drain)。 PB[3]可选择当作输入或开漏输出(Open-Drain)。

-

8 级深度硬件堆栈(Stack)。

-

存取数据有直接或间接寻址模式。

-

一组 8 位上数定时器(Timer0)包含可编程的预分频器。

-

一组 8 位下数定时器(Timer1)可选自动重载与连续下数计时。

-

一个 8 位的脉冲宽度调变输出(PWM1)。

-

Timer1 下溢中断。

-

WDT中断。

-

PB输入状态改变中断。

-

外部中断。

-

TX-P01I83在待机模式(Standby mode)下的五种唤醒中断:Timer0 上溢中断。 Timer1 下溢中断。 WDT中断。PB输入状态改变中断。外部中断。

-

TX-P01I83在睡眠模式(Halt mode)下的三种唤醒中断:WDT中断。PB输入状态改变中断。外部中断。

四、寄存器

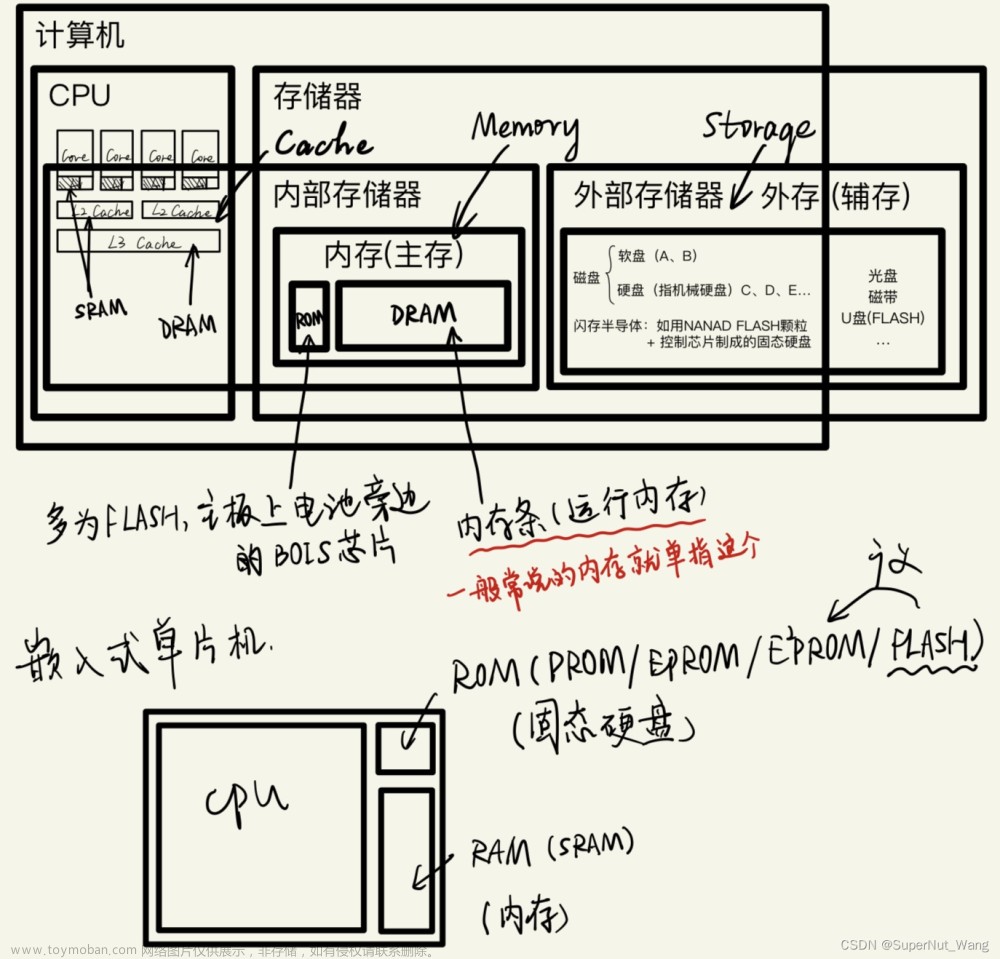

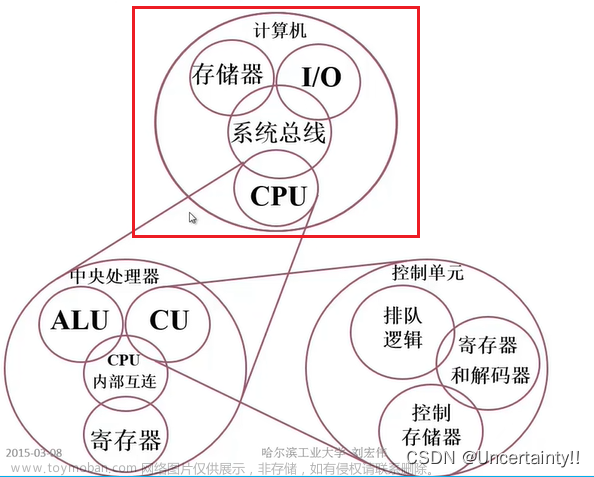

TX-P01I83存储器分为两类:分别是程序存储器和数据存储器。

程序存储器

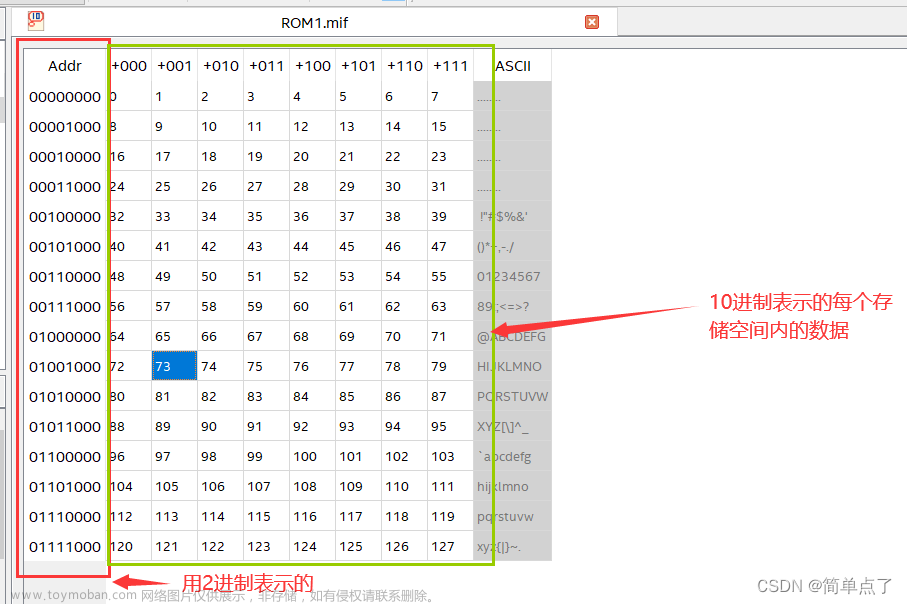

TX-P01I83程序存储器空间是 1Kx14 位。因此,10 位宽的程序计数器(PC)可以访问程序存储器的任何地址。

复位地址位于 0x000,软件中断地址位于 0x001,内部和外部硬件中断地址位于 0x008。TX-P01I83提供CALL、GOTOA和CALLA等指令去访问程序空间的 256 个地址。还提供GOTO指令去访问程序空间 512 个地址,LCALL和LGOTO指令访问程序空间的任何地址。

当发生子程序调用或中断情况时,下一个ROM地址写入堆栈的顶部。而当执行RET、RETIA或RETIE指令,堆栈顶部的数据会被读取并加载到程序计数器。

TX-P01I83程序存储器地址 0x00E~0x00F和 0x3FE~0x3FF是保留地址。如果用户在这些地址写入程序可能会发生无法预期的程序执行错误。

数据存储器

根据用于存取数据存储器的指令,数据存储器可分为三类:R-page特殊功能寄存器(SFR)和通用寄存器(GPR)、F-page特殊功能寄存器、S-page特殊功能寄存器。GPR是由SRAM组成,用户可以使用它们来存储变量或计算结果。

TX-P01I83_xx www.xdssemi.com /009TX-P01I83_xx

R-page特殊功能寄存器和数据存储器分为四组Bank,可透过数据指针寄存器(FSR)来切换Bank。寄存器BK[1:0]为FSR[7:6] ,可从四个Bank中选择其中一个。

R-page特殊功能寄存器和数据存储器可用直接寻址方式和间接寻址方式来进行存取。

数据存储器使用间接寻址方式如下图所描述,这种间接寻址方式包含使用INDF寄存器。Bank选择是由FSR[7:6]决定,地址选择则是由FSR[5:0]而定。

R-page特殊功能寄存器可以通过一般的指令存取,如算术指令和数据搬移指令。R-page特殊功能寄存器占用了从Bank 0 的 0x0 到 0xF。然而,Bank 1、Bank 2 和Bank 3 的相同地址会映像到Bank 0。换句话说,R-page特殊功能寄存器只存在于Bank 0。GPR占用了数据存储器的 0x10 到 0x3F地址。其它Bank地址 0x10 到 0x3F亦映射到Bank 0,如表 1 所示。

文章来源:https://www.toymoban.com/news/detail-793002.html

文章来源:https://www.toymoban.com/news/detail-793002.html

文章来源地址https://www.toymoban.com/news/detail-793002.html

文章来源地址https://www.toymoban.com/news/detail-793002.html

到了这里,关于EPROM 作为存储器的 8 位单片机的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[深入理解NAND Flash (原理篇)] Flash(闪存)存储器底层原理 | 闪存存储器重要参数](https://imgs.yssmx.com/Uploads/2024/02/735174-1.png)