一、 任务介绍

数字上变频器(DUC)和数字下变频器(DDC)广泛应用于通信系统,用于信号采样速率的转换。当信号从基带转换至中频( IF )带,需要使用数字上变频器。而数字下变频器是用于将信号从中频( IF )带转换为基带。DUC和DDC通常包括使用混频器进行频率转换,此外还有采样率转换。DUC或DDC的结构主要取决于所需要的转换率。例如,WiMAX (全球互通微波接入)系统典型的转换率为8—10阶。对于如此低的转换率,DUC和DDC只需采用FIR滤波器架构。如果需要更高的转换率,DDC / DUC结构中需要使用级联积分梳状(CIC)滤波器。

二、基本原理

2.1 数字上变频和数字下变频的基本原理

2.2 数字上变频(Digital Up Conversion,DUC)

以余弦信号的上下变频为例,余弦信号经过正交变频后,将信号调制到一个高频部分:

第二部分图片来源:(https://blog.csdn.net/qq_41332806/article/details/108457397)

2.3 数字下变频(Direct Digital Controller,DDC)

DDC即在数字系统中对信号进行下变频,实现从射频(中频)信号到基带信号的转变。用一个严格同频同相的载波,得到一个高频分量和低频分量,用一个低通滤波器对信号进行滤波即可将信号解调出来。

DUC & DDC:

三、基于FPGA实现DUC&DDC

3.1数字上下变频部分

FPGA实现过程基于实数形式的信号流图,主要涉及到DDS产生两路正交本振,ROM存储待下变频信号,乘法模块,FIR滤波,时域抽取等,大部分有现成IP核可供调用。

本次Output Frequency使用 1MHz 与 5MHz。

3.1.1相关IP核配置(未出现的页面使用默认设置)

1.DDS Compiler(6.0)

2.Multiplier(12.0)

根据输入进来的A & B 调整 Input Option,不同的输入调整不同的值。

3.Adder/Subtracter(12.0)

在Control 页面 将 Clock Enable(CE) 取消勾选。

4.slice(1.0)

---------------截频

5.FIR Compiler(7.2)

滤波部分

选择 COE File,配置Coefficient File,其中.coe文件在代码区;打开Channels Specification 配置Input Sampling Frequency 和Clock Frequency 分别为 100 和 100,其他设置默认。

veirilog HDL 代码:

//Copyright 1986-2020 Xilinx, Inc. All Rights Reserved.

//--------------------------------------------------------------------------------

//Tool Version: Vivado v.2020.2 (win64) Build 3064766 Wed Nov 18 09:12:45 MST 2020

//Date : Tue Mar 1 14:42:00 2022

//Host : DESKTOP-CGJL7H3 running 64-bit major release (build 9200)

//Command : generate_target DDC_DUC_wrapper.bd

//Design : DDC_DUC_wrapper

//Purpose : IP block netlist

//--------------------------------------------------------------------------------

`timescale 1 ps / 1 ps

module DDC_DUC_wrapper

(P_0,

P_1,

P_2,

P_3,

S_cos6MHz,

aclk_0,

cos_1MHz,

cos_5MHz,

fir_out_data,

fir_out_data_1,

s_axis_data_tvalid_0,

s_axis_data_tvalid_1,

sin_1MHz,

sin_5MHz);

output [31:0]P_0;

output [31:0]P_1;

output [47:0]P_2;

output [47:0]P_3;

output [31:0]S_cos6MHz;

input aclk_0;

output [15:0]cos_1MHz;

output [15:0]cos_5MHz;

output [39:0]fir_out_data;

output [39:0]fir_out_data_1;

input s_axis_data_tvalid_0;

input s_axis_data_tvalid_1;

output [15:0]sin_1MHz;

output [15:0]sin_5MHz;

wire [31:0]P_0;

wire [31:0]P_1;

wire [47:0]P_2;

wire [47:0]P_3;

wire [31:0]S_cos6MHz;

wire aclk_0;

wire [15:0]cos_1MHz;

wire [15:0]cos_5MHz;

wire [39:0]fir_out_data;

wire [39:0]fir_out_data_1;

wire s_axis_data_tvalid_0;

wire s_axis_data_tvalid_1;

wire [15:0]sin_1MHz;

wire [15:0]sin_5MHz;

DDC_DUC DDC_DUC_i

(.P_0(P_0),

.P_1(P_1),

.P_2(P_2),

.P_3(P_3),

.S_cos6MHz(S_cos6MHz),

.aclk_0(aclk_0),

.cos_1MHz(cos_1MHz),

.cos_5MHz(cos_5MHz),

.fir_out_data(fir_out_data),

.fir_out_data_1(fir_out_data_1),

.s_axis_data_tvalid_0(s_axis_data_tvalid_0),

.s_axis_data_tvalid_1(s_axis_data_tvalid_1),

.sin_1MHz(sin_1MHz),

.sin_5MHz(sin_5MHz));

endmodule

仿真:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/03/01 14:37:41

// Design Name:Born_toward

// Module Name: dds2_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module dds_duc_2_tb();

reg aclk_0;

reg s_axis_data_tvalid_0;

reg s_axis_data_tvalid_1;

wire [15:0]cos_1MHz;

wire [15:0]sin_1MHz;

wire [15:0]cos_5MHz;

wire [15:0]sin_5MHz;

wire [31:0]P_0; //cos1MHz*cos5MHz

wire [31:0]P_1; //sin1MHz*sin5MHz

wire [31:0]S_cos6MHz; //cos(1+5) MHz

wire [47:0]P_2; //cos(1+5)MHz * cos5MHz

wire [47:0]P_3; //sin(1+5)MHz * sin5MHz

wire [39:0]fir_out_data; //滤波后的I路 -> cos(1+5)MHz * cos5MHz

wire [39:0]fir_out_data_1; //滤波后的Q路 -> sin(1+5)MHz * sin5MHz

initial begin

aclk_0 = 0;

s_axis_data_tvalid_0 = 1'b1; // 此外为了方便接受数据,此处将准备接受数据标志位s_axis_data_tvalid一直置为1

s_axis_data_tvalid_1 = 1'b1; // 此外为了方便接受数据,此处将准备接受数据标志位s_axis_data_tvalid_1一直置为1

#500000;

$stop;

end

always #5 aclk_0 = ~aclk_0; //10ns 周期 100MHz

DDC_DUC_wrapper DDC_DUC_wrapper_A

(.P_0(P_0),

.P_1(P_1),

.P_2(P_2),

.P_3(P_3),

.S_cos6MHz(S_cos6MHz),

.aclk_0(aclk_0),

.cos_1MHz(cos_1MHz),

.cos_5MHz(cos_5MHz),

.fir_out_data(fir_out_data),

.fir_out_data_1(fir_out_data_1),

.s_axis_data_tvalid_0(s_axis_data_tvalid_0),

.s_axis_data_tvalid_1(s_axis_data_tvalid_1),

.sin_1MHz(sin_1MHz),

.sin_5MHz(sin_5MHz));

endmodule

FIR_BPF_99_1_5M.coe 文件:

Radix=16;

Coefficient_Width=16;

CoefData=0000 0001 0003 0005 0008 0009 0006 fffe ffef ffd8 ffba ff98 ff76 ff5b ff4e ff57 ff7f ffcb 003e 00d5 0187 0244 02f7 0385 03cf 03b8 0325 0206 0056 fe21 fb87 f8ba f601 f3b0 f225 f1be f2d5 f5af fa7b 0144 09f2 1442 1fcc 2c06 384e 43f4 4e49 56aa 5c92 5f9f 5f9f 5c92 56aa 4e49 43f4 384e 2c06 1fcc 1442 09f2 0144 fa7b f5af f2d5 f1be f225 f3b0 f601 f8ba fb87 fe21 0056 0206 0325 03b8 03cf 0385 02f7 0244 0187 00d5 003e ffcb ff7f ff57 ff4e ff5b ff76 ff98 ffba ffd8 ffef fffe 0006 0009 0008 0005 0003 0001 0000;

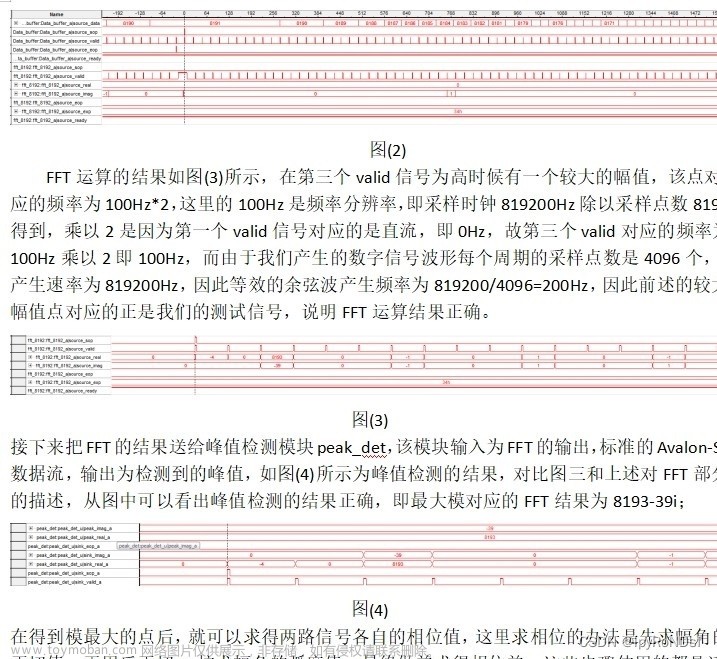

3.2 FPGA仿真波形

基于vivado run simulation 仿真实现:

Block Design: 文章来源:https://www.toymoban.com/news/detail-793790.html

文章来源:https://www.toymoban.com/news/detail-793790.html

四、参考文献

[1] 无线通信的MATLAB和FPGA实现 / 西瑞克斯(北京)通信设备有限公司编著.——北京:人民邮电出版社,2009.6

源工程文件已上传至

https://download.csdn.net/download/Born_toward/86512126?spm=1001.2014.3001.5501文章来源地址https://www.toymoban.com/news/detail-793790.html

到了这里,关于数字信号处理----数字上变频和下变频都FPGA实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!