本章将介绍时序信息在单元库(library cell)中是如何描述的。这个单元可以是1个标准单元(standard cell)、1个IO缓存器( IO buffer),或者复杂的IP(ItellectualProperty,知识产权)核,比如USB核( USB core)。

除了时序信息,单元库还包括了其他一些属性 attributes,比如单元的面积和功能(cell area and functionality),虽然这些属性和时序没关系,但是它们在RTL综合时是需要考虑的。在本章,我们只需要关注和时序以及功耗计算相关的属性。

1个库单元可以用多种标准格式来描述。这些格式在本质上是很相似的,这里我们采用Liberty格式来描述库单元。

在本章开始的部分会介绍线性以及非线性(linear and the non-linear)时序模型,接着在3.7节会介绍专门为纳米工艺准备的先进时序模型。

3.1 引脚电容(Pin Capacitance)

单元的每个输入和输出都可以在引脚上指定引脚电容(Pin Capacitance)。在大多数情况下,只会指定输入的电容而不会指定输出的,在大多数单元库中,输出引脚的电容是0。

上面的例子展示了输入INP1的引脚电容值的常见规范。在它最基本的格式中,引脚电容被指定为单一值(在上面的例子中是0.5个单位(units)。电容的单位通常在库文件的开头被指定为皮法(Picofarad)。单元描述中也可以为rise-capacitance(0.5个单位)和fall_capacitance(0.45个单位)分别指定值,它们分别对应引脚INP1的上升和下降转换时间,rise_capacitance和fall_capacitance也可以被指定为范围,在描述中指定上下限的值。

3.2 时序建模(Timing Modeling)

单元时序模型(Cell Timing Model)可以为设计环境中各种单元的实例(Instance)提供精准时序信息。时序模型通常是从单元的详细电路仿真中得到的,用来给单元的实际运行场景建模。

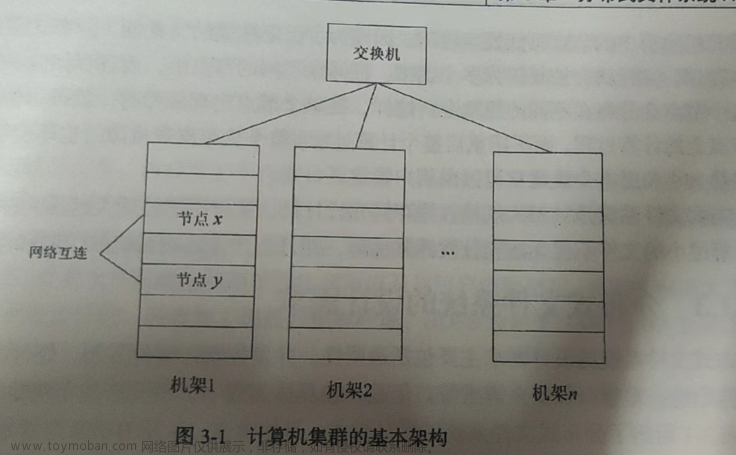

让我们研究图3-1所示的1个简单反相器(inverter)逻辑单元的时序弧。因为它是个反相器,输入的上升(下降)转换会导致输出的下降(上升)转换。表征反相器的是这两类延迟:

Tr:输出上升延迟Tf:输出下降延迟

注意,延迟是基于库文件中定义的阈值点来计算的(见2.4节),通常是50%的Vdd。所以,延迟是计算从输入跨过阈值点到输出跨过阈值点的时间。

通过反相器单元的时序弧的延迟是基于以下2个因素:

- 1)输出负载,也就是反相器

输出引脚的电容负载: - 2)信号在

输入的转换时间(Transition Time)。

延迟的值和负载电容有直接关系:负载电容越大,延迟越大。在大多数情况下,延迟随着输入转换时间增加而增加。在少数情况下,输入阈值(用来计算延迟)和单元内部转换点(Internal Switching Point)有显著的不同。在这种情况下,单元的延迟可能和输入的转换时间呈现非单调性——更大的输入转换时间可能产生更小的延迟,尤其是输出负载较小时。

单元输出转换率(Slew)主要取决于输出电容——输出转换时间随输出电容增大而增大。所以,输入的较大转换率(较长的转换时间) 可能在输出得到改善,这取决于单元类型和输出负载。图3-2展示了单元输出的转换时间是如何根据输出负载改善或恶化的。

3.2.1 线性时序模型(Linear Timing Model)

一种简单的时序模型是线性延迟模型(Linear Delay Model,.LDM),单元的延迟和输出转换时间由2个参数的线性方程来表示:输入转换时间(Input Transition Time)和输出负载电容(Output Load Capacitance)。通过单元的延迟D用线性模型的一般形式表示如下:

式中,D0、D1、D2都是常数,S是输入转换时间,C是输出负载电容。对于亚微米工艺,线性延迟模型对于一定范围内的输入转换时间和输出电容并不精确,所以现在大部分单元库采用了更复杂的模型,比如非线性延迟模型(Non--linear Delay Model,NLDM)。

3.2.2 非线性延迟模型(Non-Linear Delay Model)

大部分单元库包括表模型(Table Model)来为单元的各种时序弧指定延迟和时序检查。一些用于纳米技术的较新的时序库还提供了基于电流源(Current Source)的高级时序模型(比如CCS、ECSM等),这将在本章后文中描述。这些表模型(Table Model)被称为NLDM,它被用来计算延迟,输出转换率,或者其他时序检查。这个表模型通过单元输入引脚的输入转换时间(Input Transition Time)和单元输出引脚的总输出电容(Total Output Capacitance)这两者的各种组合,来查表得到通过单元的延迟。

延迟的NLDM通过二维表格来表示,2个独立变量是输入转换时间和输出负载电容,表中的数值表示延迟。这里有1个典型的反相器单元的表格例子:

在上面的例子中描述了输出接口OUT的延迟信息。这段节选的单元描述包括了从引脚INP1到引脚OUT时序弧的上升和下降延迟模型,以及引脚OUT所能允许的max_transition。对上升延迟和下降延迟(对于输出引脚)有单独的模型,它们被分别标记为cell_rise和cell_fall。索引(Index)的类型以及查表时素引的顺序在查表模板delay_template_3x3中有描述。

这个查询表(Lookup Table)模板定义表中第1个变量是输入转换时间,第2个变量是输出电容。表的值类似于嵌套循环,第1个索引(index_1)是外圈循环变量(或者变化较少的变量),第2个索引(index2)是内圈循环变量(或者变化较多的变量) 。每个变量有3个条目,所以这对应1个3×3的表。在大多数情况下,条目也被按照表来格式化,第1个索引(index1)可以认为是行索引,第2个索引(index2)相当于列索引。索引值(比如1000)是虚拟占位符(Dummy Placeholder),可以被cell_fall和cell_rise延迟表中的真实索引值覆盖。

另一个指定索引值的方法是在模板定义时指定索引值,而不是在cell_rise和cell_fall表中指定它们。这样的模板看起来像这样:

基于上面的延迟表,输入下降转换时间 为 0.3s ,输出负载为 0.16pF ,相应的反相器的上升延迟为 0.1018s 。因为输入下降转换导致反相器的输出上升,应该用反相器输入的下降转换去查表得到上升延迟。

这种用表格来表示延迟的方法就是NLDM,该表格是转换时间和负载的函数,因为表中的延迟是随着输入转换时间和输出负载电容非线性变化的。

该表模型也可以是三维的——比如拥有互补输出Q和QN的触发器,在3.8节对此有描述。

NLDM不仅可以用来描述延迟,也可以用来描述单元输出的转换时间,该时间也是由输入转换时间和输出负载来表征。所以,也有单独的二维表来计算单元输出的上升和下降转换时间。

有两种转换时间的表格:rise_transition和fall_transition。如第2章中描述的,转换时间是基于转换率阈值来计算的,通常是供电电压的10%~90%。

如上面说明的,1个具有NLDM的反相器单元有以下表格:

上升延迟(Rise delay)下降延迟Fall delay)上升转换时间(Rise transition)下降转换时间(Fall transition)

如图3-3所示,基于该单元的输入转换时间和输出负载,上升延迟由cell_rise表格中15ps输入转换时间(下降) 和10fF负载查表得到,下降延迟由cell_fall表格中20ps输入转换时间(上升)和10fF负载查表得到。

是哪里的信息表明这个单元是反相器呢?这一信息属于时序弧timing sense字段。某些情况下,并没有指定这一字段,但是可以从接口功能能字段推算出来。

对于例子中的反相器单元,时序弧属性timing_sense的值是negative_unate,这表明输出接口的转换方向是和输入接口的转换方向相反的(负相关)。所以,要用输入接口的下降转换时间去查找cell_rise(输出上升延迟)表格。

非线性延迟模型的查表示例(Example of Non-Linear Delay Model Lookup)

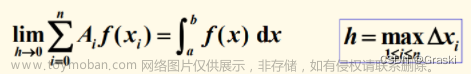

本节通过1个例子说明了如何查找表模型(Table Model)。如果输入转换时间和输出电容在表中都有对应的值,那么查表就很简单,因为时序值直接对应表中的索引值。下面的例子是一种常见的情况,表中没有要找的值。在这种情况下,二维插值法(Two-dimensional interpolation)被用来得到时序的计算值。假设我们用输入转换时间0.15ns和输出电容1.16pF来查找下降转换时间(之前指定的示例表)。下降转换时间表中相应的部分被摘抄如下,用二维插值法计算:

在下面的公式中,2个index_1值用x1和x2表示,2个index_2值用y1和y2表示,相应的表中的查找值用T11、T12、T21和T22分别表示。

如果需要在表中查找(x0,y0)对应的值,那查找值T00通过插值法得到:

3.2.3 阈值规范和转换率减免( Threshold Specifications and Slew Derating)

转换率(Slew is same as transition time(转换时间))的值是基于库文件中设定的测量阈值。大部分旧工艺的库(0.25μm或者更旧)用10%和90%作为转换率或者转换时间的测量阈值。

转换率阀值的选择是和波形的线性部分是对应的(The slew thresholds are chosen to correspond to the linear portion of thewaveform)。随着工艺的进步,真实波形的线性部分通常是30%-70%。所以,大部分较新工艺的时序库函数都设定Vdd的30%-70%作为转换率的测量点。但是, 因为之前的转换时间是用10%和90%测量的,在移植(Populate)库时,用30%-70%测量的转换时间被翻倍了。这个问题用 转换率减免系数(Slew Derate Factor) 来解决,它的值通常是0.5。转换率阈值为30%-70%,且转换率减免系数为0.5,就等效于用10%~90%测量的结果。下面阈值设定的例子可以进一步说明。

**上面的设置表明,库函数表格中的转换时间必须乘以0.5来得到转换率國值(30-70)对应的转换时间。**这意味着转换时间表格中的值(以及相应的索引值)是在10-90的阈值下测量的。在建库时(Characterization),转换时间在30-70阈值下测量,然后把测量数据外推到10%~90%阈值的情况[(70-30)/(90-10)=0.5]。

另一个例子,不同的转换率阈值(slew threshold)可能包括:

例子中的转换率阈值是20-80,并且没有指定slew_derate_from_library(默认为1),意味着库文件中的转换时间不会减免(Derate)。转换时间表中的值就是直接由20-80阈值得到的,如图3-4所示。

本例中,slew_derate_from_library为0.6,建库时转换率阈值是20%-80%。这表明库文件中的转换时间表是阈值为0%~100%扩展得到的值[(80-20)/(100-0)=0.6],如图3-5所示。

库文件中的转换时间表*slew_derate=建库时转换率阈值

当指定了转换率减免(Slew Derating),转换率的值会在计算延迟时内部转换:

这就是在计算延迟时工具使用的转换率,对应建库时的转换率阈值测量点。

3.3 时序模型——组合逻辑单元(Timing Models - Combinational Cells)

让我们考虑一个双输入的与门单元的时序弧( timing arcs for a two-input and cell)。这个单元的2个时序弧都是positive-unate,所以,输入的上升对应着输出的上升,反之亦然,如图3-6所示。

对于双输人与门单元,有4种延迟:

A→Z:输出上升 Output riseA→Z:输出下降 Output fallB→Z:输出上升Output rise-

B→Z:输出下降Output fall

这意味着对于NLDM,为了表示延迟会有4个表模型(Table Model)。类似地,也会有4个表模型来表示输出转换时间output transition times。

3.3.1 延迟和转换率模型

下面的例子是3输入与非门的输入INP1和输出OUT的时序模型。

在这个例子中,用了2个单元延迟表(cell_rise和cell_fall),以及2个转换时间表(rise_transition和fall_transition)来表示从INP1到OUT的时序弧。输出max_transition的值也包括在上面的例子中。

正单调性(Positive Unate)或负单调性(Negative Unate)

正如2.7节中的描述,与非门单元例子中的时序弧是负单调性,也就是说输出引脚的转换方向和输人引脚的转换方向是相反的(负相关)。所以,cell_rise查表是对应输入引脚的下降转换时间。另一方面,与门或者或门单元的时序弧就是正单调性,因为输出转换和输入转换是同方向的。

3.3.2 常用组合逻辑块( General Combinational Block)

考虑以下有3个输入、2个输出的组合逻辑块(CombinationalBlock),如图3-7所示。

像这样的逻辑块具有多个时序弧。通常,逻辑块的每个输人到输出都有时序弧。如果从输入到输出的逻辑路径是非反相(Non-inverting)或者正单调性,那么输出和输人具有相同的极性。如果逻辑路径是反相路径或者负单调性,则输出和输入具有相反的极性,所以,当输入上升时,输出下降。这些时序弧表示了经过这个逻辑块的传播延迟propagation delays。

有时,穿过组合逻辑单元的时序弧可以是正单调的,也可以是负单调的,比如,穿过双输入异或门单元的时序弧。在双输入异或门单元的某1个输入上的转换,可以造成输出转换是同相或者反相,这取决该单元另1个输入的逻辑状态。这些时序弧可以被描述成非单调性(Non-unate),或者两组不同的正单调性和负单调性时序模型,这取决于输入的状态。这种状态依赖的表会在3.5节中有更详细的描述。

3.4 时序模型——时序单元

考虑图3-8所示的时序单元的时序弧。

For synchronous inputs(同步输入), such as pin D (or SI, SE), there are the following timing arcs:

Setup check arc (rising and falling),建立时间检查时序弧(上升和下降)Hold check arc (rising and falling)

For asynchronous inputs(异步输入), such as pin CDN, there are the following timing arcs:

- Recovery check arc,恢复时间

- Removal check arc,移除时间

For synchronous outputs of a flip-flop(触发器同步输出), such as pins Q or QN, there is the following timing arc:

CK-to-output propagation delay arc (rising and falling),CK到输出的传播延迟时序弧(上升和下降)。

所有的同步时序弧都和时钟有效沿(active edge of the clock)相关,有效沿就是引起时序单元捕获数据的时钟沿。另外,时钟引脚和**非同步引脚[比如清除引脚(Clear Pin)]**之间会有脉冲宽度时序检查(Pulse Width Timing Check)。图3-9展示了用不同信号波形进行时序检查。

3.4.1 同步检查:建立时间和保持时间( Synchronous Checks: Setup and Hold)

建立(Setup)和保持(Hold)同步时序检查 是为了保证数据正确的通过时序单元sequential cells传播。这些检查保证了数据输入在时钟的有效沿是清晰唯一的,并且数据输入在有效沿被正确地锁存(Latched)。这些时序检查确保了在有效时钟沿附近数据输入是稳定的。在有效时钟前数据输入必须保持稳定的最小时间叫作建立时间(Setup Time)。 建立时间是测量最近的数据信号(Latest Data Signal)跨过它的阈值(通常是50%Vdd)和有效时钟沿跨过它的阈值(通常是50%Vdd)两者之间的时间间隔。类似地,保持时间(Hold Time)就是在有效时钟之后,数据输入必须保持稳定的最小时间。 保持时间是测量有效时钟沿跨过它的國值和最早的数据信号(Earliest Data Signal)跨过它的阈值两者之间的时间间隔。之前提到过,对于时序单元,时钟的有效沿就是引起时序单元捕捉数据的上升或下降沿。

Example of Setup and Hold Checks(建立时间检查和保持时间检查的例子)

一个时序单元的同步引脚的建立时间约束和保持时间约束通常用二维表来描述,如下面的例子所示。下面的例子展示了触发器数据引脚的建立时间和保持时间信息。

上面的例子显示了相对于时钟CK的上升沿,1个时序单元输入引脚D上的建立时间和保持时间约束。这个二维模型的索引是constrained_pin(D)和related_pin(CK)上的转换时间。查找这个二维表是根据库文件中的模板setuphold_template_3x3。对于上面的例子,查表模型setuphold_template_3x3可以描述为:

像上面的例子,表中建立时间的值类似于嵌套循环,第1个索引(index_1)是外圈循环变量(或者变化较少的变量),第2个索引(Index_2)是内圈循环变量(或者变化较多的变量),诸如此类。所以,当D引脚的转换时间是0.4ns,CK引脚的转换时间是0.84ns,对于D引脚的上升沿建立时间约束值就是0.112ns,这个值是从rise_constraint表中查到的 。对于D引脚的下降沿,建立时间约束要查找建立时间表中的fall_constraint表。 当查找建立时间和保持时间表时,索引值里找不到转换时间,要采用3.2节中描述的非线性模型查表常用方法。

注意,建立时间约束的rise_constraint表和fall_constraint表是指constrained_pin。查表使用的时钟转换时间是由timing_type决定的,它指定了单元是上升沿触发还是下降沿触发。

建立时间检查和保持时间检查里的负值(Negative Values in Setup and Hold Checks)

注意,例子里的一些保持时间值是负值。这是可接受的,这通常发生在当数据路径从触发器的引脚到内部的锁存点(Latch Point)比对应的时钟路径长。所以,保持时间为负值意味着触发器的数据引脚可以先于时钟引脚变化,并且依然满足保持时间检查。

触发器的建立时间也可以是负值。这代表在触发器的引脚上,数据可以在时钟引脚后变化,且依然满足建立时间检查。

建立和保持时间可以都是负值吗?不行。为了让建立和保持时间检查一致,建立时间和保持时间的和必须为正。所以,如果建立时间(或者保持时间)检查包含负值,那相应保持时间(或者建立时间)必须是足够大的正值,以保证建立时间加上保持时间的和是正值。下面来看图3-10所示的例子,它有负保持时间。因为建立时间必须发生在保持时间之前,建立时间加上保持时间是正值。建立时间加保持时间的时间宽度就是信号必须保持稳定的区间。

对于触发器,在扫描数据输入(Scan Data Input)引脚有负的保持时间是很有帮助的。这给了时钟偏移(Clock Skew)一定灵活性,在扫描模式(Scan Mode)下就不需要为了修复保持时间违例而插入大量的缓冲器(Buffer)(扫描模式是指在该模式下,触发器被串联在一起形成扫描链,1个触发器的输出通常被连接到下1个触发器的扫描数据输入引脚,这种连接发生是为了可测试性)。

和在同步数据输入端的建立保持时间检查类似,异步引脚上也有约束。接下来将进一步的介绍。

3.4.2 异步检查(Asynchronous Checks)

恢复时间和移除时间检查(Recovery and Removal Check)

异步引脚,比如异步清除(Clear)引脚或者异步置位(Set)引脚可以覆盖单元的任何同步行为。当1个异步引脚处于有效状态(Active),输出是由异步引脚控制而不是由数据输入端的时钟锁存控制。但是,当异步引脚变为无效状态(Inactive),时钟的有效沿开始在数据输入端锁存。异步的恢复和移除约束检查确保异步引脚在下1个有效时钟沿之前确定恢复到1个无效状态。

恢复时间是异步引脚被设置为无效(De-asserted)后,在下1个有效时钟沿之前需要保持稳定的最短时间。

类似地,移除时间是在异步引脚可以被设置为无效(De-asserted),前,在1个有效时钟沿之后需要保持有效的时间。

异步移除和恢复时间检查在8.6节和8.7节中有介绍。

脉冲宽度检查(Pulse Width Checks)

除了同步和异步时序检查,还有一个检查来确保单元输入引脚的脉冲宽度满足最小要求。比如,如果时钟引脚上的脉冲宽度小于指定的最小值,时钟可能没有正确的锁存数据。可以给相关的同步和异步引脚指定脉冲宽度检查。最小脉冲宽度检查可以指定高脉冲和低脉冲。

恢复时间、移除时间以及脉冲宽度检查的例子

下面的例子是触发器的异步清除引脚CDN的恢复时间、移除时间以及脉冲宽度检查。恢复时间和移除时间检查与时钟引脚CK有关。因为恢复时间和移除时间是为处于无效状态的异步引脚定义的,所以下面的例子中只有上升约束。引脚CDN的最小宽度检查是针对低脉冲的。因为引脚CDN是低电平有效,对于该引脚的高脉冲宽度没有约束。

3.4.3 传播延迟

时序单元的传播延迟(The propagation delay of a sequential cell)是从时钟的有效沿到输出的上升或下降沿。下面的例子是1个下降沿触发的触发器,从时钟引脚CKN到输出Q的传播延迟弧。这是非单调(Non-unate)时序弧,**因为时钟的有效沿可以导致输出Q的上升或者下降沿。**下面是延迟表(DelayTable):

像之前的例子一样,到输出的延迟用二维表来表示,二维表的索引是输入的转换时间和输出引脚的电容。但是在这个例子里,因为这是下降沿触发的触发器,要使用的输入转换时间是CKN引脚的下降转换时间。这一点在上面例子中的字段(Construct) timing-type里共表明了。上升沿触发的触发器会指定rising_edge作为timing_type

3.5 状态相关的时序模型(State-Dependent Models)

在很多组合逻辑块(Block)中,输入和输出之间的时序弧取决于该逻辑块的其他引脚。这些输入输出之间的时序弧可以是正单调,负单调,或者既是正单调也是负单调。举个例子,异或门(XOR)或者异或非门(XNOR),到输出的时序弧可以是正单调或者负单调的。在这些例子里,时序行为根据逻辑块其他输入的状态会有所不同。通常来讲,需要根据引脚的状态描述多个时序模型。这些模型被称作状态相关的时序模型(State-Dependent Model)

异或门、异或非门和时序单元

考虑1个有两输入的异或门单元。当输人A2是逻辑0时,从输入A1到输出Z的时序路径是正单调的。当输人A2是逻辑1时,从A1到Z的路径就是负单调的。这:个时序模型用状态相关模型来指定。当A2是逻辑0时,从A1到Z的时序模型指定如下:

用when条件来指定状态相关条件。以上的单元模型摘录只说明了cell_rise延迟,其他时序模型(cell_fall、rise_transition以及fall_transition表)也用同样的when条件来指定。另1个when条件——当A2是逻辑1时,时序模型如下:

当生成SDF时,sdf_cond是用来指定时序弧的条件的,见3.9节的例子,以及在附录B

中COND字段。

状态相关模型被用来描述各种类型的时序弧。很多时序单元用状态相关模型指定建立或保持时间的约束。下面的例子中用状态相关模型指定了1个扫描触发器的保持时间约束。在这个例子中,使用了两组模型,一组是当扫描使能引脚(Scan Enable Pin)SE是有效的(Active),另一组是当扫描使能引脚是无效的(Inactive)。

上面的模型是当SE引脚在逻辑0,类似的模型是当when条件的SE在逻辑1。

一些时序关系要同时使用状态相关模型和非状态相关模型(Non-state--dependeModl)来指定。在这样的情况下,如果单元的状态是已知的且这个状态属于状态相关模型,那么时序分析就要用到状态相关模型。如果状态相关模型不包括单元的状态,那么就要用到非状态相关模型。比如,考虑一种情况,保持时间约束只有一种when条件:SE在逻辑0,没有状态相关模型对应SE在逻辑1。在这种情况下,如果SE被设置为逻辑1就要用到非状态相关模型。如果保持时间约束没有非状态相关模型,就没有任何有效保持时间约束。

状态相关模型可以用来指定时序库中任何属性(Attribute)。所以,状态相关的规范可以是功耗(Power)、漏电功耗(Leakage Power)、转换时间(Transition Time)、上升和下延迟、时序约束等。下面的例子是状态相关漏电功耗的规范:

3.6黑箱(Black Box)的接口时序模型( Interface Timing Model for a Black Box)

本节描述黑箱(任意模块和块)的I0接口上的时序弧。时序模型捕获黑箱IO接口时序。这个黑箱接口模型可能有组合逻辑弧,也可能有时序逻辑弧(Sequential Timing Arc)。通常,这些弧也是状态相关的。

对于图3-11所示的例子,这些时序弧可以被归类为以下几种:

-

输入到输出组合逻辑弧(Input to output combinational arc):这对应着直接从输入到输出的组合逻辑路径,比如从输入端口FIN到输出端口FOUT。 -

输入时序弧(Input sequential arc):这被描述为输入的建立或保持时间,该输入连接到触发器的D引脚。通常,在将块的输入和触发器的D引脚连接之前,存在着组合逻辑。这类例子是在端口DIN相对于时钟ACLK的建立时间检查。 -

异步输入弧(Asynchronous input arc):这类似于触发器的异步输人引脚上的恢复时间和移除时间约束。例如输入ARST到触发器UFF0的异步清除引脚。 -

输出时序弧(Output sequential arc):这类似于时钟到输出端的传播时间,该输出端连接到触发器的Q端。通常,它们是位于触发器输出端到模块(Module)输出端的组合逻辑。例如,从时钟BCLK到触发器UFF1的输出端,再到输出端口DOUT。

除了上面提到的时序弧,还会在黑箱外部时钟引脚上有脉冲宽度检查(Pulse Width Check)。也可以定义内部节点,并且在这些内部节点上定义生成时钟(Generated Clock),进而指定到达或来自这些节点的时序弧。总的来说,一个黑箱模型可能有以下时序弧:

- 1)对于组合逻辑路径的输入到输出时序弧。

- 2)从同步输人到相应的时钟引脚的建立和保持时间时序弧。

- 3)从异步输入到相应的时钟引脚的恢复和移除时间时序弧。

- 4)从时钟引脚到输出引脚的传播时间延迟。

上面描述的接口时序模型并没有包括黑箱的内部时序,只包括了接口的时序。

3.7 先进时序建模(Advanced Timing Modeling)

时序模型,比如NLDM,代表了基于输出负载电容和输入转换时间的,经过时序弧的延迟。实际上,单元输出看到的负载包括了电容和互连电阻。因为NLDM这种方法假设输出负载是纯电容性的,所以互连线电阻就成了问题。即使互连电阻不为0,当互连电阻很小的情况下,NLDM还是可以使用的。由于互连电阻的存在,延迟计算算法改进了NLDM,它在单元的输出端创造了1个等效的有效电容(Effective Capacitance)。这个“有效”电容的算法被用在了计算延迟的工具里,它在单元的输出端创造了1个等效的电容,该电容和具有RC互连线的单元有相同的延迟。该有效电容方法在5.2节中作为延迟计算的一部分有进一步描述。

随着特征尺寸的缩小,波形变得很不线性,互连线电阻可能会导致精度很差。各种建模方法为单元输出驱动提供了更好的精度。广义上讲,这些方法用等效电流源(Equivalent CurrentSource)对驱动的输出级建模来获得更高的精度。常见的方法有CCS(Composite CurrentSource,复合电流源模型、ECSM(Effective Current Source Model,有效电流源模型)。比如,CCS时序模型使用随时间变化,且依赖电压的电流源给单元输出驱动建模,以得到更好精度。通过在不同场景(Scenario)下为接收引脚电容(Receiver Pin Capacitance,即输入引脚电容一相当于NDLM中的引脚电容)和输出充电电流,指定更精细的模型来提供时序信息。接下来要详细介绍CCS模型。

3.7.1 接收引脚电容(Receiver Pin Capacitance)

接收引脚电容对应着NLDM中定义的输入引脚电容(Input Pin Capacitance)。和NLDM中的引脚电容不同,CCS模型允许对接收电容在转换波形的不同部分分别定义。由于互连线RC和单元内输入器件的密勒效应(Miller Effeet)所带来的等效输入非线性电容,接收电容在传输波形的不同点上具有不同的值。所以,这个电容在波形的初始段或者前段(Initial or Leading portion)建模与后段(Trailing portion)建模是不同的。

接收引脚电容可以在引脚级(Pin Level)指定(如NLDM),所有经过这个引脚的时序弧都使用该电容值。或者,接收引脚电容可以在时序弧级(Timing Arc Level)指定,对于不同的时序弧指定不同的电容模型。这两种指定接收引脚电容的模型如下所示。

1.在引脚级指定电容,Specifying Capacitance at the Pin Level

当在引脚级指定电容,下面给出的例子就是接收引脚电容的一维规范表。

index_1指定的目录是这个引脚的输入传输时间。这个一维表中的values为输入引脚上升波形的前段(Leading portion) 指定了接收电容。

类似于上面的receiver_capacitancel_rise, receiver_capacitance2_rise为输入上升波形的后段(Trailing portion)指定了上升电容。下降电容(下降输入波形的引脚电容)是用属性receiver_capacitancel_fall和receiver_capacitance2_fall分别指定的。

2.在时序弧级指定电容(在时序弧级指定电容)

接收引脚电容也可以在时序弧级用二维表指定,索引为输入转换时间和输出负载。下面给出的例子就是在时序弧级的规范。该例子指定了引脚IN的波形前段(LeadingPortion)的接收引脚上升电容,该电容是输人引脚IN上的转换时间和输出引脚OUT上的负载的函数。

上面的例子指定了receiver_capacitancel_rise的模型。这个库包括相似的receiver_capacitance2_rise、receiver_capacitancel_fall,以及receiver_capacitance2_fall规范的定义。

这4种不同的接收电容类型总结在表3-1中。综上所述,这些电容可以用一维表指定在引脚级,也可以用二维表指定在时序弧级。

3.7.2 输出电流(Output Current)

在CCS模型里,非线性时序用输出电流来代表。输出电流的信息用查询表(Lookup Table)来指定,该表依赖于输人转换时间和输出负载。

输出电流根据输入转换时间和输出电容的不同组合被指定为不同的值。对任意一个组合,输出电流波形是确定的。本质上,这里的波形指的是随时间变化的输出电流值。如下面的例子所示,用output_current_fall指定了下降输出波形的输出电流。

属性reference_time是指当输入波形跨过延迟阈值的时间。Index_I和index_2是指输入转换时间和用到的输出负载,index_3是时间。Index_1和index_2(输入转换时间和输出电容)可以每个只有1个值。Index_3指的是时间值,而values指的是相应的输出电流。所以

对于给定的输入转换时间和输出负载,输出电流波形是时间的函数。同样地,也指定了输入转换时间和输出电容的其他组合的查找表。

类似地,用output_current_rise指定上升输出波形的输出电流。

3.7.3 串扰噪声分析模型(Models for Crosstalk Noise Analysis)

本章介绍的是用于串扰噪声(或毛刺)crosstalk noise (or glitch), 分析的CCS模型。该模型被称为CCSN(CCS噪声)模型。该CCS噪声模型是结构化模型(Structural Model),并表示为单元内的不同CCB(Channel Connected Blocks,沟道连接块)。

什么是CCB? CCB是指单元的源-漏沟道(Source--Drain Channel)的连接部分。例如单级(Single Stage)单元,比如反相器、与非门和或非门,都只包含1个CCB, 即整个单元通过唯一的沟道连接区域连接。多级(Multi-Stage)单元,比如与门和或门,包含多个CCB.

CCSN模型通常指定单元输入驱动的第1个CCB和驱动单元输出的最后1个CCB。该模型通常会用稳态电流(Steady State Current)、输出电压以及传播噪声模型(Propagated Noise Model)来指定。

对单级组合逻辑单元,比如与非门和或非门,要为每个时序弧指定CCS噪声模型。这些单元只有1个CCB, 因此模型是从单元的输入引脚到输出引脚的。

下面的例子是与非门:

现在我们来介绍下CCS噪声模型的属性。属性ccsn_first_stage表明这个模型是属于与非门单元的第一级CCB。如前所述,与非门只有I个CCB。属性is_needed几乎永远都为真,除了非功能性单元,比如负载单元和天线单元。属性stage_type的值both,表示该CCB级同吋具有上拉和下拉结构。属性miller_cap_rise和miller_cap_fall分别表示上升和下降输出转换时间的密勒电容。(密勒电容指的是反相阶段的等效输入电容,由于输入端和输出端之间电容放大作用,所增长出的电容)

1.直流电流(DC Current)

dc_current表示了输入和输出引脚电压的不同组合的直流电流。Index_I指定了输入电压,index2指定了输出电压。二维表的values指定了CCB输出的直流电流。输入电压和输出电流都使用库中指定的单位(通常是V和mA)。例如,与非门的输入IN1到输出OUT的CCS噪声模型,当输入电压是-0.9V,输出电压是0V,则输出的直流电流是0.42mA。

2.输出电压(Output Voltage)

属性output_voltage_rise和output_voltage_fall分别包括了CCB输出端上升和下降的时序信息。这些属性是CCB输出节点的多维表。这些多维表由多个表组成,为不同的输入转换时间和输出线电容指定了上升和下降输出电压。每个表的index_1指定了轨到轨的输入转换时间,index2指定了输出线电容,index_3指定了输出电压跨过指定的阈值点的时间(本例中是0.9V Vdd电压的30%、70%和90%)。在每个多维表中,电压跨越点(Voltage CrossinPoint)是固定的,CCB输出节点跨过这个电压的时间在index_3中指定。

3.传播噪声(Propagated Noise)

propagated_noise_high和propagated_noise_low模型指定的多维表,提供了穿过CCB的噪声传播信息。这些模型表征了串扰毛刺(或噪声)从CCB的输入到输出的传播。表征时在输入端使用了对称三角波。propagated_noise的多维表由多个表组成,指定了在CCB输出的毛刺波形。这些多维表包括:

1)输入毛刺大小量级(index_1);

2)输入毛刺宽度(index_2);3)

3)CCB输出线电容(index_3)

4)时间(index_4)

CCB输出电压(或者通过CCB传播的噪声)用表中的值指定。

4.两级单元的噪声模型

像单级单元一样,两级单元比如“与门单元”或者“或门单元”,通常被描述为时序孤的一部分。因为这些单元包含2个独立的CCB,分别为ccsn_first_stage和ccsn_last_stage指定噪声模型。例如,对于两输入与门单元,CCS噪声模型包含单独的第一级模型和最后一级模型,如下所示:

在ccsn_last_stage中为IN2指定的模型,和ccsn_last_stage中为IN1指定的模型是一样的。

5.多级单元和时序单元的噪声模型(Noise Models for Multi-stage and Sequential Cells)

复杂的组合逻辑单元以及时序单元的CCS噪声模型通常被描述为引脚规范(Pin Specificatio)的一部分。这和单级或两级单元是不同的,如与非门、或非门、与门、或门。单级或两级单元的噪声模型通常是以引脚对(Pin-pair)为基础,指定为时序弧的一部分。复杂的多级单元和时序单元通常是用ccsn_first_stage模型来描述所有的输人引脚,用ccsn_last_stge模型来描述所有的输出引脚。这类单元的CCS噪声模型不是时序弧的一部分,但是通常指定在引脚上。

如果在输入和输出之间的内部路径有两级及以上CCB, 那噪声模型也可以表示为引脚对(Pin-pair)时序弧的一部分。通常来说,1个多级单元的描述,可以一部分噪声模型用引脚对时序弧指定,另一部分用引脚描述指定。

下面例子中的CCS噪声模型就是部分用引脚描述指定,部分用时序弧指定。

注意,上面触发器的一些CCS模型是用引脚规范来定义的。使用引脚规范的CCS模型在输入引脚上指定为ccsn_first_stage,在输出引脚QN上指定为ccsn_last_stage。另外,CDN到Q的两级CCS噪声模型被描述为时序弧的一部分。这个例子展示了,1个单元的CCS模型可以既包含部分引脚规范,也包含部分时序弧。

3.7.4其他噪声模型( Other Noise Models)

除了上面提到的CCS噪声模型,一些单元库提供了其他模型来表征噪声。有些模型在CCS噪声模型出现前用来表征噪声。如果CCS噪声模型存在,就不需要这些额外的模型。为了更全面地了解,我们下面介绍一些早期的噪声模型。

直流余量模型(Models for DC Margin):直流余量指的是在单元的输入端可以允许的最大的直流变化量,这个变化量使单元处于稳定状态,也就是说,不会引起输出端的毛刺。比如,对低电平输入,直流余量指的是输入引脚上不会引起输出任何电平转换的最大直流电压值。

抗噪声模型(Models for Noise Immunity):抗噪声模型指的是在输入引脚可以允许的毛刺量级。该模型通常用二维表来描述,表的2个索引是毛刺宽度和输出电容。表中的值就是输入引脚可以允许的毛刺量级。这意味着,任何毛刺只要小于指定的量级和宽度,就不会通过该单元传播。抗噪声模型的不同衍生模型如下所示:

3.8 功耗建模(Power Dissipation Modeling)

单元库包含了单元功耗相关的信息。这包括了动态功耗(Active Power)和待机功耗(Standby Power)或者漏电功耗(Leakage Power)。顾名思义,动态功耗就是芯片活跃时的功耗,待机功耗就是在待机模式下产生的功耗,主要是漏电造成的。

3.8.1 动态功耗(Active Power)

动态功耗和单元输入输出引脚上的活动相关。单元的动态功耗是由输出负载的充电和内部开关(Internal Switching)组成的。这两者分别指的是输出开关功耗(Output SwitchingPower)和内部开关功耗(Internal Switching Power)。

输出开关功耗和单元的类型无关,只和输出电容负载、开关的频率,以及单元的供电电压相关。内部开关功耗和单元类型相关,所以内部开关功耗是包括在单元库中的。下面将描述库中内部开关功耗的规范。

内部开关功耗是指单元库中的内部功耗(Internal Power)。这种功率消耗是当单元的输入或输出有活动时,发生在单元内部的。对于1个组合逻辑单元,输入引脚的转换可以引起输出的翻转(Switch),进而导致内部的开关功耗(Switching Power)。比如,1个反相器,当输入翻转(在输入端有上升或下降的转换)就会消耗功率。库文件中的内部功耗如下所示:

上面的例子展示了从单元输入引脚A到输出引脚Z1的功率消耗。例子中的2×2表的索引是引脚A的输入转换时间和引脚Z1的输出电容。注意,虽然表包括了输出电容,但是表中的值只表示内部开关功耗,并不包括输出电容的功耗。这些值代表了单元对应于每个开关转换时间(上升或下降)的内部能量消耗。功耗的单位是从库文件中其他单位推导出来的(通常电压的单位是V,电容的单位是pF,这对应的能量单位是pJ)。所以,库文件中的部功耗实际上是每个电压转换对应的能量消耗。

上面例子中除了功耗表,还描述了电源引脚(Power Pin)、接地引脚(Ground Pin),以及电源中断的功能,该功能指定了关断单元电源的条件。这些功能允许芯片有多个供电电源,并且在不同场景下关断不同的电源。下面的例子介绍了每个单元的电源引脚规范。

电源规范的语法允许对上升和下降(指输出端状态)电源分别构造。就像时序弧一样,电源规范也可以是状态相关的(State-dependent)。比如,1个异或门状态相关的功率损耗可以指定为各种输入状态相关的。

对于组合逻辑单元,开关功耗是以输入-输出引脚对(Pin Pair)为基础指定的。但是对1个时序单元,比如触发器,它具有互补性的输出Q和QN,CLK->Q的转换也会导致CLK->QN的转换。因此,该库文件可以用三维表指定内部开关功耗,如下所示。下面例子中的三维是指CLK上的转换时间,Q和QN上各自的输出电容。

即使是输出或者内部状态没有转换,开关功率也可能被消耗。1个常见的例子是在触发时钟引脚上翻转(Toggle)的时钟。这个触发器在每次时钟翻转的时候都消耗功率,通常是由于触发器内部的反相器在翻转。即使是触发器的输出端没有切换,也会由于时钟引脚的翻转产生功耗。所以对于时序单元,输入引脚的功耗指的是单元内部的功耗,也就是当输出没有变化时的功耗。下面的例子说明了输入引脚功耗规范。

这个例子说明了在时钟引脚翻转时的功耗规范。这表示了当输出没有变化时,由时钟翻转所带来的功耗。

时钟引脚的功耗是否被重复计算了(Double Counting Clock Pin Power?)

注意,触发器依然包括了CLK->Q转换所带来的功耗。所以,很重要的一点是,CLK、Q功耗表的值并没有包括当输出Q不产生变化时CLK内部的功耗。

上面的说明指的是工具使用功耗表的一致性,并且确保由于时钟输入造成的内部功耗没有在功耗计算中被重复计算。

3.8.2 漏电功耗(Leakage Power)

大部分单元被设计成只有当输出或者状态改变时才会产生功耗。当单元接通电源但没活动时产生的任何功耗都是由于非零的漏电流(Non-zero Leakage Current)。这些漏电流可能是由MOS器件的亚阈值电流(Subthreshold Current)引起的,或者是栅极氧化物(Gate Oxide)的隧穿电流(Tunneling Current)引起的。在早期的CMOS工艺技术中,漏电功耗可以忽略不计,也不是芯片设计中需要主要考虑的问题。但是,随着工艺尺寸的缩小,漏电功率变得越来越显著,和动态功耗相比不再是可以忽略的了。

如上所述,漏电功耗主要由两种现象构成:MOS器件的亚阈值电流和栅极氧化物隧穿效应。通过使用高阈值电压(HighVt、高阈值电压单元指的是单元比该工艺技术下的标准单元具有更高的阈值电压) 单元,可以减少亚阈值电流;但是这里要权衡阈值电压单元的速度损失。高阈值电压单元拥有更小的漏电流,但是速度也更慢。类似地低阈值电压单元拥有更大的漏电流但是也有更快的速度。通过更换高(或者低)阈值电压单元,栅极氧化物隧穿电流变化不明显。所以,使用高阈值电压单元是一种可行的控制漏电流的方法。和选择高低阈值电压单元类似,选择单元驱动能力也是在漏电流和速度之间做平衡。更高的驱动能力有更高的漏电流但是提供更高的速度。关于功耗管理的取舍在10.6节中有更详细的描述。

MOS器件的亚阈值漏电流和温度有很强的非线性关系。在大多数工艺条件下,随着器件结温(Junction Temperature)从25℃升高到125℃,亚阈值漏电流可以增长10-20倍。栅极氧化物隧穿电流相对来说是不随温度或者器件的阈值电压变化而变化的。栅极氧化物隧穿电流在100nm工艺及以上是可忽略的,而在低温65nm或更先进的工艺时,它成为漏电流的重要贡献者。例如,在室温下的65nm或更先进工艺下,栅极氧化物隧穿电流可能等同于亚阈值漏电流。在高温时,亚阈值漏电流占据漏电流的主导地位。

在库函数中指定了每个单元的漏电流。例如,一个反相器单元可能包含下面的描述:

这是单元的漏电功耗,漏电功耗的单位在库的头文件中有指定,通常是纳瓦(Nanowatt)。通常情况下,漏电功耗依赖于单元的状态,而状态可以用when条件指定。

例如,一个INV1单元可以有如下描述:

I是INV1单元的输入引脚。需要注意的是,描述包含1个默认值(在when条件之外),这个默认值通常是通过when条件指定的漏电流值的平均值。

3.9 单元库中的其他属性(Other Attributes in Cell Library)

除了时序信息,库文件中的单元描述指定了面积、功能以及时序弧的SDF条件。这些信息在本章有简要描述,更详细的信息请参考Liberty手册。

3.9.1 面积规范(Area Specification)

面积规范提供了单元或者单元组的面积。

上面的例子指定了单元的面积是2.35个面积单位。这可以是该单元占据的真实的硅上面积,也可以是面积的相对测量值。

3.9.2 功能规范(Function Specification)

功能规范中指定了引脚(或者引脚组)的功能。

上面的例子指定了两输入与门单元的Z引脚的功能。

3.9.3 SDF条件

SDF条件属性支持标准延迟格式(Standard Delay Format,SDF)文件的生成,以及反标(Backannotation)时的条件匹配。就像时序分析时,when关键词指定了状态相关模型的条件,相应的状态相关时序分析的SDF标注条件由关键词sdf_cond指定。

下面的例子可以说明:

3.10 特征化和工作条件( Characterization and Operating Conditions)

一个单元库会指定产生该库的特征化(Characterization)条件和工作条件(Operatin Condition)。比如,库文件的头部可能包含以下信息:

标称环境条件(通过nom_process、nom_temperature和nom_voltage来指定)指定了库在特征化时的工艺、电压和温度。工作条件指定了该库中的单元在何种条件下可以使用。如果特征化条件和工作条件不符,通过计算得到的时序值就需要进行减免(Derate);这通过库文件中指定的减免系数(k-factor,k系数)来实现。

通过减免来得到与库特征化时条件不一致的其他条件下的时序值,会在时序计算时引入误差。这种减免的方法只有实在无法特征化库时才考虑使用。

什么是工艺变量(What is the Process Variable?)

和温度、电压这些物理量不同,工艺不是一个可以计量的变量。它可以是缓慢(Slow)、典型(Typical)或者快速(Fast)工艺之一,它的存在是为了数字化表征或验证。所以,工艺值为1.0(或者其他值)代表什么?答案如下:

库文件的特征化是非常耗时的,对各种工艺角进行特征化可能需要数周的时间。这个工艺变量的设置允许在特定工艺角下特征化的库文件,可以在不同的工艺角下计算时序。工艺的k系数可以从特征化的工艺到目标工艺进行延迟减免。像之前提到的,减免系数会在时序计算中引入误差。跨工艺的减免尤其不准确,所以很少使用。总结一下,指定不同的工艺值(比如1.0或者其他)的唯一功能是为了允许跨工艺条件的减免,但是很少使用。

3.10.1用k系数来减免(Derating using K-factors)

如上所述,当工作条件和特征条件不一致时,减免系数(也就是k系数)是用来得到延迟的。这个k系数是近似系数。下面的例子就是库文件中的k系数。

在计算延迟时,当工作条件的工艺、电压以及温度和库文件中标称的条件不一致时,这些系数是用来得到时序的。注意k_volt系数是负值,表明延迟随着供电电压增加而减少,k_ temp系数是正值,表明通常延迟随着温度增加而增加(除非单元产生了温度反转效应2.10节有描述)。这个k系数使用如下:

比如,假设库文件在1.08V、125℃和slow工艺下特征化。如果要在1.14V和100℃情况下得到延迟,slow工艺下,单元的上升延迟如下所示:

假设使用上面列出的k系数,上面的等式可以转换为:

在减免条件下,延迟约为原有延迟的94.48%。文章来源:https://www.toymoban.com/news/detail-794015.html

3.10.2库单位(Library Units)

1个单元描述中的值都使用库的单位。这些单位用Liberty命令集在库文件中声明。下面的例子表明了电压、时间、电容和电阻的单位是如何声明的。

在本书中,我们假设所有的库时间单位是ns,电压单位是V,每次转换的内部功耗单位是pJ,漏电功耗是nW,电容单位是pF,电阻单位是千欧,面积单位是um2,那些为了帮助理解明确指定的单位除外。 文章来源地址https://www.toymoban.com/news/detail-794015.html

文章来源地址https://www.toymoban.com/news/detail-794015.html

到了这里,关于静态时序分析 第三章 标准单元库的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!