参考资料

【明德扬_verilog零基础入门语法HDL仿真快速掌握-手把手教你写FPGA/ASIC代码设计流程中的应用】

2 模块例化、运算符

2.1 模块例化

2.1.1 什么是模块例化

例化,即将项目不断拆分成次级功能模块,然后从最简单的模块开始实现,进而完成整个复杂项目

2.1.2 模块例化的方法

针对已经抽象好的模块,需要进行语义化命名,以便后续的调试。

2.1.3 参数例化

在不改变原来模块大体内容的情况下,改变一个变量的位宽

参数例化的好处:在仿真测试时便于调整基准数据,例如仿真时钟时可以将基准时间从1秒改成0.001秒。

通过此方式,可以将原来模块中8位的DATA_W,在例化时改为16位

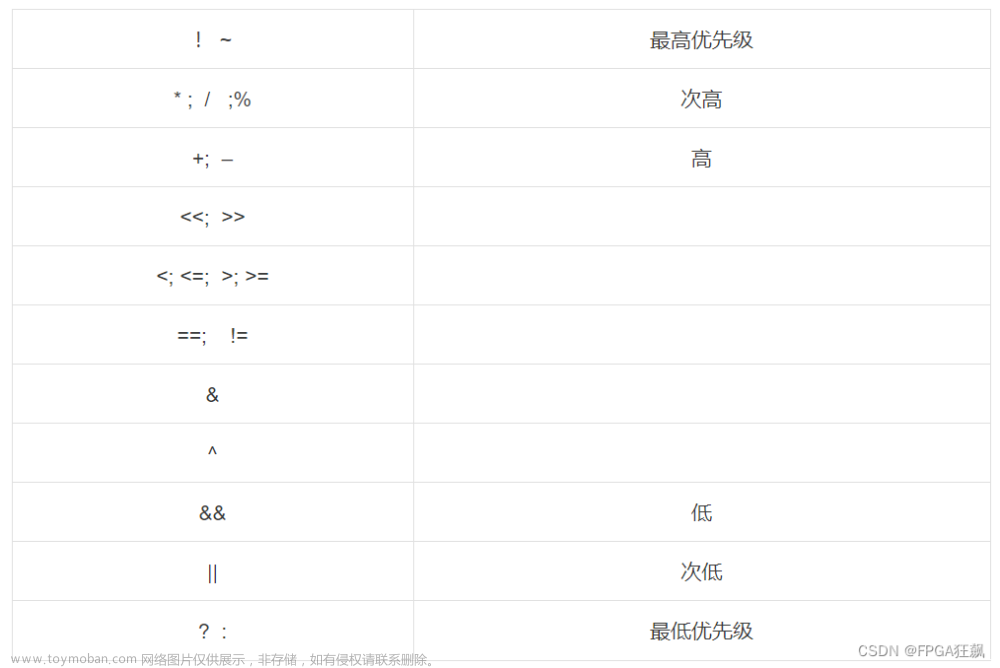

2.2 运算符

2.2.0 总览

2.2.1 信号类型reg/wire

EXAMPLES

- 本模块always产生的信号,用reg eoc_cnt

2. 本模块产生,非always,用wire row1,row2

3. 本模块产生,是always,用reg rdreq

4. 肯定不是always产生的,使用wire sdata

2.2.2 参数parameter(相当于c语言的宏定义)

2.2.3 算术运算符

FPGA中,除法和求余需要大量的逻辑块,耗费资源多,因此需要尽量少用

2.2.4 关系运算符

2.2.5 赋值运算符

不要搞复杂了

- 时序逻辑用: <=

- 组合逻辑用: =

2.2.6 逻辑运算符

2.2.7 位运算符

2.2.8 移位运算符

文章来源:https://www.toymoban.com/news/detail-794085.html

文章来源:https://www.toymoban.com/news/detail-794085.html

2.2.9 拼接运算符

多个相同的位数,可以用:{个数{a[n]}}实现重复拼接 文章来源地址https://www.toymoban.com/news/detail-794085.html

文章来源地址https://www.toymoban.com/news/detail-794085.html

到了这里,关于Verilog语法——2.模块例化、运算符的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!