module flag(clk,rst_n,cnt);

input clk;

input rst_n;

output [2:0]cnt ;

reg[31:0]count ;

reg [2:0]cnt;

always@(posedge clk or negedge rst_n)

begin

if(~rst_n)begin

count<=0 ;

cnt<=3'd0 ;end

else if (count>= 32'd24 999) begin

cnt<=cnt+1'b1 ;count<=32'd0 ;

end

else if (cnt>=3'd6) begin

cnt<=0;end

else

count<=count+1'b1 ;

end

endmodule

'timescale 1 ns/ 1ps

/

module seg (

clk, rst_ n,data,dig,led

);

input clk;

input rst_n;

input [23:0] data;

output [5:0] dig; //六位控制六个数码管

output [7:0] led;

reg [5:0] dig;

reg [7:0] led;

reg [3:0] d;

always@ (posedge clk or negedge rst_ n ) begin

if(~rst n) led<= 8'b0;/ /low active

else begin

case (d)

4'h0:led<= 8 'b00111111 ;//0

4'h1 :led<= 8 'b00000110;//1

4'h2:led<= 8'b01011011 ;//2

4'h3:led<= 8'b01001111 ;//3

4'h4:led<=8'b01100110;//4

4'h5:led<= 8'b01101101 ;//5

4'h6:led<= 8'b01111101 ;//6

4'h7:led <= 8 'b00000111;//7

4'h8:led<= 8'b01111111 ;//8

4'h9:led<= 8'b01101111 ;//9

4'ha:led<= 8 'b01110111 ;//a

4'hb:led<= 8'b01111100;//b

4'hc:led<= 8'b00111001 ;//c

4'hd:led<= 8'b01011110;//d

4'he:led<= 8'b01111001 ;//e

4'hf:led<= 8'b01110001 ;//f

default: led<=8'b0 ;

endcase

end

end

wire [2:0]cnt2 ;

flag flag_ _m0 (

.clk(clk),// INPUT

. rst_n(rst_n) ,// INPUT

, cnt (cnt2) / / OUTPU

);

always@ (posedge clk or negedge rst_ n ) begin

if(~rst_n)begin dig<= 6"b0;

end

else begin

case (cnt2)

3'd0 :begin dig<= 6'b000001; d<=data[3:0] ;end

3'd1 :begin dig<= 6'b000010; d<=data[7:4] ;end .

3'd2 :begin dig<= 6'b000100; d <=data[11:8] ;end

3'd3 :begin dig<= 6'b001000; d<=data[15:12] ;end

3'd4 :begin dig<= 6'b010000; d<=data[19:16] ;end

3'd5 :begin dig<= 6'b100000; d<=daLa[23:20] ;end

default :begin dig <= 6'b0 ;end

endcase

end

end

///

module count (

clk,

rst_n,

bin,

clk_in

);

input clk;

input rst_n;

input clk_in;

output [23:0] bin;

reg [1:0]clk_1hz ;

reg[31:0] countl ;

reg[23:0] count2 ;

reg[23:0] bin;

always @ (posedge clk or negedge rst_ n )

begin

if (~rst_n) begin

count1<=0;clk_1hz<=0;

end

else begin

if (count1 == 32'd49 999 999) begin

count1<= =0 ;

clk 1hz<=clk 1hz+1;end

else if(clk 1hz== 0)

clk 1hz <= 2'd1 ;

else countl <= count1+1'b1 ;

end

end

wire clk_in pos;

reg clk_in0,clk_inl ;

always @ (posedge clk or negedge rst_n)

begin

if(~rst n) begin .

clk_in0<=0 ;

clk_in1 <=0 ;end

else begin

clk_in0 <=clk_in;

clk_in1 <=clk_in0 ;end

end

assign clk_in pos=~clk_in1 & clk_in0;

always@(posedge clk or negedge rst_n)

begin

if (~rst n) begin

count2 <=0;bin<=0 ;end

else if (clk_1hz==1 &&clk_in_pos)

count2 <= count2 + 1'b1 ;

else if(clk_1hz==2)

bin<=count2;

else if(clk_1hz==3)

count2<=0 ;

else begin count2 <= count2 ;bin<=bin ;end

end

//

module hex tobcd (

input clk_in ,

input rst,

input [23:0]bin ,

output [23:0]bcd ,

output [1 :0] bcd_ valid .

);

reg [1:0] bcd valid;

//提取显示数值所对应的十进制数的各个位

assign bcd[3:0] =bin%4'd10;

assign bcd[7:4] =bin/4'd10%4'd10 ; //十位数

assign bcd[11:8] =bin/7'd100%4'd10 ; //百位数

assign bcd[15:12] =bin/10'd1000%4'd10 ; //千位数

assign bcd[19:16] =bin/14'd10000%4'd10; //万位数

assign bcd[23:20] =bin/17'd100000;

//十万位数

always@(posedge c1k_in)

begin

if (bin[23:20]>= =1 'b1) begin

bcd_valid= 2'b01 ;

end

else begin

bcd_valid= 2'b11 ;

end

end

endmodule

///

module clk_test #(parameter DIV N= 'd100) // 分频系数

(

//源时钟

input clk;

input rst_n;

//复位信号

//分频后的时钟

output reg clk_in;

//输出时钟

);

reg [25:0] ct ;

//时钟分频计数

//时钟分频,生成500KHz的测试时钟

always @ (posedge clk or negedge rst_n) begin

if(rst_n== 1 'b0) begin

ct<= 0;

clk_in<= 0 ;

end

else begin

if(ct== DIV_ N/2-1'b1) begin

ct <= 26'd0;

clk_in<=~clk_in;

end

else

ct <=ct + 1'b1 ;

end

end

endmodule

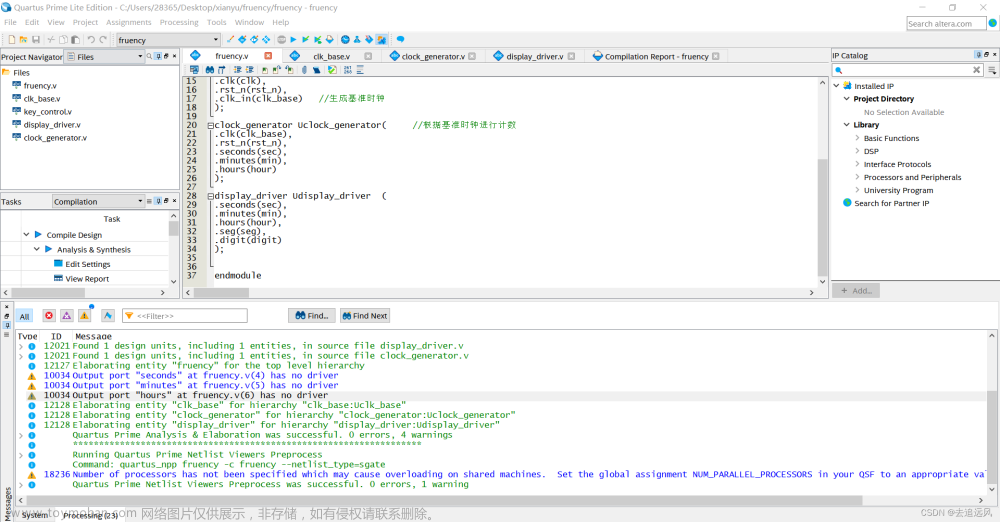

/

、timescale 1ns/1ps

module fre_test (

clk,

rst_n,

clk_in,

sel_0,

dig_0,

feq_valid

);

input clk;

inout clk_ in;//外接信号输入

input rst_n;

output [5:0] sel_0; //六位码表示六个数码管

output [7:0] dig_0;

output [1:0] feq_valid;

wire locked;

wire [23:0] data;

wire [23:0] bin;

reg [23:0] count2;

count count0 (

.clk(clk) ,

.clk in(clk_in) ,

. rst n(rst_n) ,

.bin (bin)

);

hex tobcd hextobcd m0 (

.clk in(clk), / / INPUT

.rst(~rst n), / / INPUT

.bcd valid(feq valid),/ / OUTPUT

. .bin (bin),

/ / INPUT [23:0]

. bcd (data)

/ / OUTPUT [23:0]

);

lseg seg0 (

.clk(clk),// INPUT

.rst n(rst_ n),// INPUT

.data(data),/ / INPUT [23:0]

.dig(sel_ 0),

// OUTPUT[5:0]

led(dig_ 0) / / OUTPUT[7:0]

);

lclk test u_ clktest (

clk(clk) ,

.clk_ in(clk in) ,

.rst n(rst n)

);

//

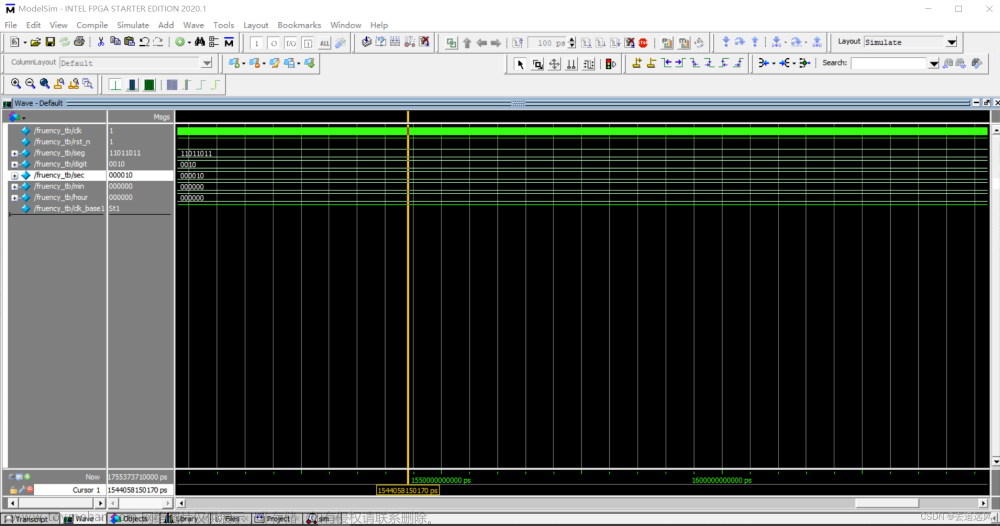

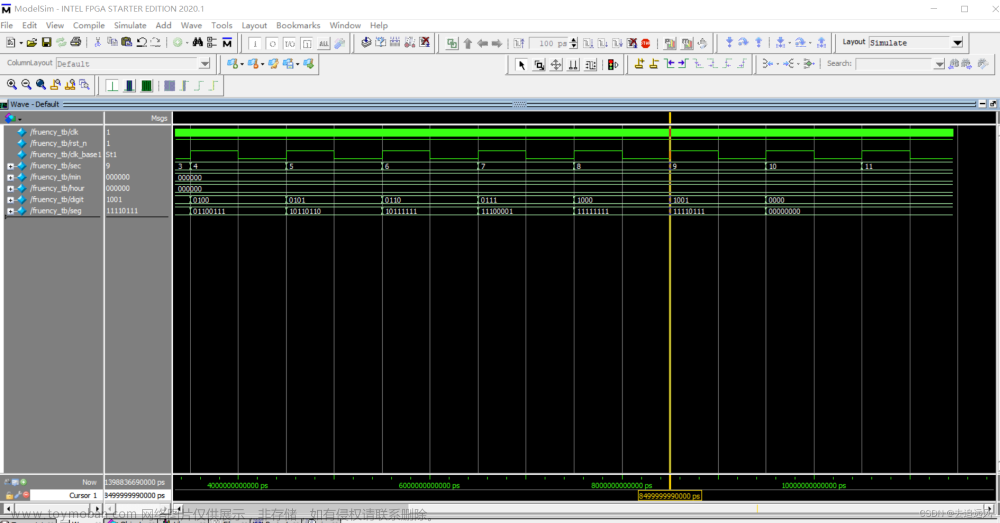

`timescale 1ns/ 1ps

module fre_tb() ;

reg clk;

reg clk in;

reg rst_n;

wire[5:0] sel_ 0;

wire[7:0] dig_ 0;

fre test uut (

.clk(clk),/ / INPUT

rst n(rst n),/ / INPUT

clk in(clk in),// INPUT

.se1

0(sel_ 0),// OUTPUT[5:0]

.dig_ 0(dig_ 0) // OUTPUT[7:0]

);

initial begin

clk=0 ;

clk_in=0;

rst_n=0 ;

#10;

rst n=1 ;

end

always #1000 clk in=~clk in;

always #10 clk= ~clk;S

endmodule

文章来源:https://www.toymoban.com/news/detail-794399.html

文章来源:https://www.toymoban.com/news/detail-794399.html

文章来源地址https://www.toymoban.com/news/detail-794399.html

文章来源地址https://www.toymoban.com/news/detail-794399.html

到了这里,关于【FPGA & Modsim】数字频率计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!