在对Verilog代码进行静态时序分析的时候,建立时间和保持时间是需要我们重点关注的指标。

1.建立时间和保持时间的是什么?

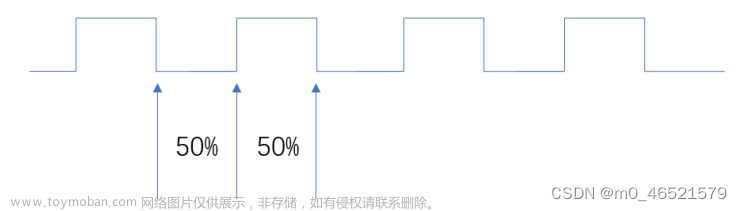

建立时间(Setup Time):指采样时钟边沿到来之前,数据需要保持稳定的时间。如果数据在采样时钟的边沿到来之前的建立时间内这段时间变化,可能会造成时钟采样的数据在0和1之间跳变,使得寄存器进入亚稳态(亚稳态:可以理解为不稳定的状态)。

保持时间(Hold Time):指采样时钟边沿到来之后,数据需要保持稳定的时间。如果数据在采样时钟的边沿到来之后的建立时间内这段时间变化,可能会造成寄存器进入亚稳态,寄存器内的数据采样数据可能无法正确存储。

建立时间和保持时间,总的来说就是,采样时钟跳变沿到来的前一段时间和后一段时间,被采样数据都不能变化,要保持稳定,如果在采样时钟跳变沿来之前的一小段时间内变化,则可能无法正确对数据进行采样,如果在采样时钟跳变沿来之后的一小段时间内变化,则可能出现采样了之后但数据没有正确地保存在寄存器里面。

下面,举一个例子来说明时钟和建立时间以及保持时间的关系。想象一下你(数据)坐公交(时钟)从你家到学校,公交车每隔10分钟来一趟(相当于某一时钟频率)。假设公交车每天的8:00am会到你家附近的公交站(时钟的采样沿),如果你8点踩点去公交站,那你有可能会错过那一趟公交车(数据在时钟跳变沿来之前还没稳定),因为公交车可能会来早点或者来晚一点。那么,怎么能确保你一定坐上8:00am那一趟公交车呢?答案很明显,就是提前几分钟过去公交站等(这个等待的时间就是建立时间)。而你上车之后,可能要坐10分钟的车,3个站,但是时间还没到,你就提前一个站下车,那你就无法准时到达学校(不考虑你下车后叫司机来接你的情况)。也就是说,你必须要在车上待足够长的时间(这个等待的时间就是保持时间),否则,公交车无法将你送到学校(寄存器数据可能无法正确保存)。

2.建立时间和保持时间的作用是什么?

在对Verilog代码进行静态时序分析的时候,建立时间和保持时间是需要我们重点关注的指标。它们关系到代码能否正常地在FPGA中的运行。Verilog代码使用Vivado,Quartus等开发套件编译完成后,都可以看到静态时序分析报告。在时序分析报告中,通常出现的是setup time slack(建立时间裕量)和hold time slack(保持时间裕量),即建立时间和保持时间还有多少余量,如果setup time slack为正值,则表示建立时间裕量还有空余,意味着该路径可以运行在更高的时钟频率下;而setup time slack为负值时,则表示建立时间不满足要求,意味着该路径无法在该时钟频率下稳定运行,需要做时序优化。至于hold time slack,一般都不用管,几乎遇不到会出现保持时间违例的情况。(本人对保持时间违例的情况了解甚少,需要学习)

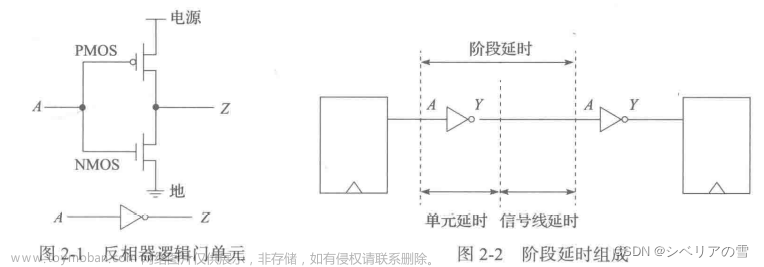

上图是一个 经典的时序分析图,展示的是一个寄存器到寄存器的路径。一般来说,绝大部分的静态时序分析都是在分析寄存器到寄存器之间的路径。接下来用一段简短的代码来辅助说明一下。

//========= code 1 ========

reg in ;

reg out;

always@(posedge clk or negedge rst_n)

if(!rst_n)

out <= 1'd0;

else

out <= ~in;

//========= code 2 ========

reg [ 7: 0] in ;

reg [17: 0] out;

always@(posedge clk or negedge rst_n)

if(!rst_n)

out <= 1'd0;

else

out <= (~in + 1'b1) * (~in + 1'b1);以上两段代码,都是从寄存器到寄存器的路径,唯一的区别就是,从in到out的计算不一样,第一段只是将in取反就送给out了,而第二段既做了取反,还做了加法和乘法,计算相对第一段明显复杂了。这个时候,我们思考这样一个问题:上面这两段代码中的时钟clk到底支持多高的频率?100MHz,200MHz还是300MHz?

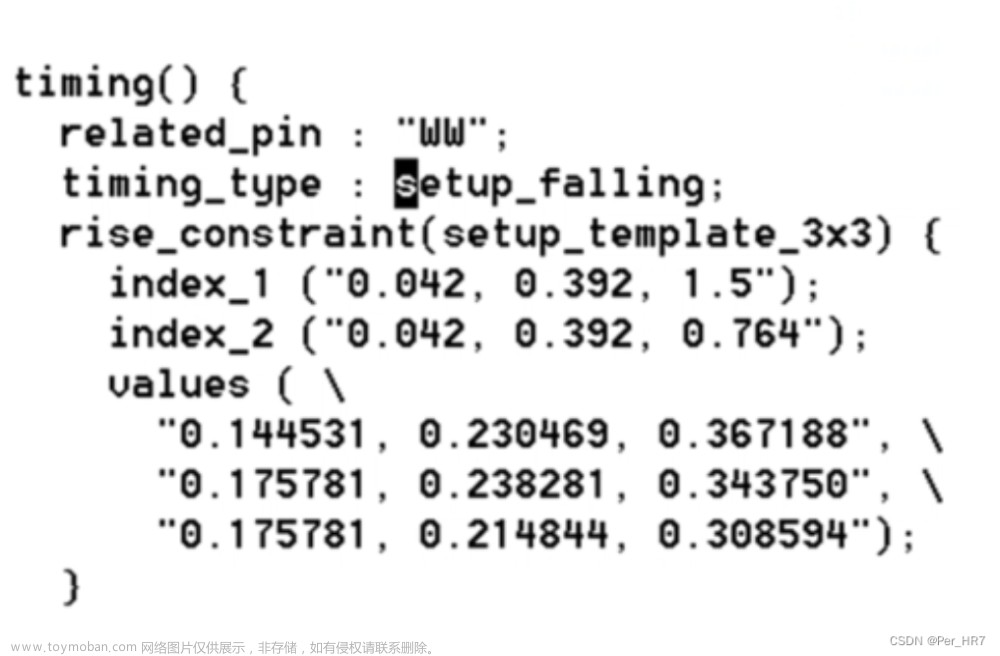

计算最大工作频率的公式如上,其中,Tco为发端寄存器从时钟到达直至数据到达Q端的时间,Tlogic为组合逻辑延迟,Tnet为两级寄存器之间的布线延迟,Tsetup为收端寄存器建立时间,Tskew两级寄存器的时间skew,其值等于时钟同一边沿到达两个寄存器时钟端口的时间差。在FPGA中,对于同步设计,Tskew可以忽略,Tco和Tsetup取决于芯片工艺,通常越先进的工艺,Tco和Tsetup越小。因此,一旦芯片型号选定只能通过Tlogic和Tnet来改善最大频率。对于FPGA来说,由于布局布线的过程一般都是自动完成的(除非你加了额外的约束),Tnet也不是我们能决定的因素。

因此,上面的代码支持的最大频率主要由Tlogic决定,亦即如果想代码运行得快一点,那就得缩短Tlogic,这个关系到时序优化的方法,内容很多,以后我有时间会再写一篇关于时序优化的文章,和大家一起学习一下。文章来源:https://www.toymoban.com/news/detail-794642.html

总结一下,建立时间和保持时间,是静态时序分析中的重要一环,通常以建立时间裕量和保持时间裕量的形式出现,来评价Verilog设计的电路是否符合要求。而静态时序分析,又是评价Verilog代码能否在硬件载体中稳定运行得一个重要手段,是上板调试前的必要步骤,因此初学者应该充分理解其含义,为后续的深入学习打下基础。以上内容仅为个人的学习分享,如果错误,还望指正。文章来源地址https://www.toymoban.com/news/detail-794642.html

到了这里,关于一文弄懂Verilog静态时序分析中的建立时间和保持时间的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[静态时序分析简明教程(八)]虚假路径](https://imgs.yssmx.com/Uploads/2024/02/434351-1.png)