第一章 方案设计

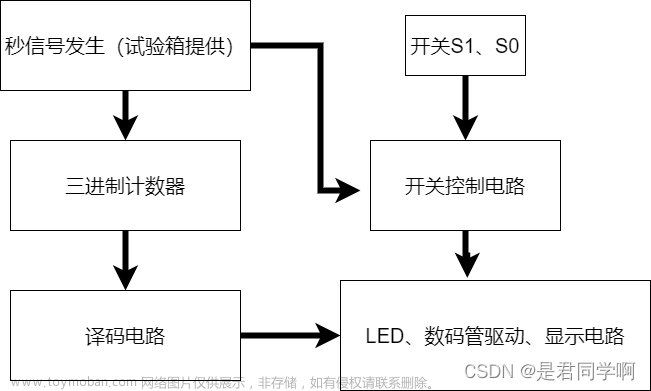

要设计制作一个花样彩灯控制电路。有十只LED,L0到L9,显示方式为先奇数灯依次灭,再偶数灯依次灭,再由L0到L9,依次灭。显示间隔为1S。

由题目可知,我们可以分成23种情况:首先全亮这是第一种情况,然后接下来奇数灯依次灭5种情况,然后在全亮一种情况,接下来偶数灯依次灭5种情况,再然后10灯全亮一种情况,最后10个灯依次灭。共计23种情况。

这23种情况分给10盏灯。为了方便可以改成24种情况,最后一种情况视为不管。那整个实验就可分为3个模块:24进制的构成、24进制的分配以及将24种情况分给10盏灯来实现预计。

需要用到的逻辑器件:74LS161十六进制计数器,74HC139四选一数据选择器,74LS138八选一数据选择器,与非门,与门,LED灯以及数字时钟。

图1----74LS161引脚图

图2----74LS138引脚图

方案实施:首先24进制的构成,为了方便24进制的分配模块,我们不采用同步置零法与异步清零法,而是将24分成3组,每8个为一组,这样就相当于主要用一片74LS161的三个输出作为主要输出,其余用这片剩下的一个输出与另外一片的一个输出构成控制端口去控制这三组的输出。而在分配模块,我们用上面所说的控制输出端口通过74HC139的输出作为74LS138的使能端,再通过3片74LS138的输出最后实现24种情况。在将24种情况分配给10盏灯时,需要逐个分析每盏灯在每种情况的亮灭问题,通过列表,经过与非门和与门的控制,最后实现彩灯问题。

图3----彩灯原理框图

第二章 电路设计

2.1 24进制的构成

由于我们构造的是3个八进制组合成的24进制,而一片16进制计数器不够所以由74LS161十六进制计数器的功能表可知,我们可以当这一片16进制完成一个周期后在传给下一片16进制的计数器,第二片计数器也需要设置个限制条件。我们已经将第一片16进制的计数器的三个输出端作为主要输出端,而另外一个输出端就理所当然的成为了限制第二片计数器的工具之一。

表2.1.1----16进制计数器的功能表

具体实现方法:将两片74LS161十六进制的计数器的CLK端都连接数字时钟,A、B、C、D都接地或者接低电压。右边的计数器ENT、ENP、LOAD端连接高电压,而要实现第三个八进制的进位,左边的计数器的ENP、ENT端口则需要当右边的计数器完成一个周期后,四个输出QA、QB、QC、QD通过与门传入。而还要实现限制清零,这就要用到前面所提到的右边计数器的QC、QB、QA三个端口同时输出1,在和左边计数器QA端口输出1一起与非在传入给两片计数器的CLR端口实现异步清零。具体如图4所示。

图4----24进制的构成电路图

2.2 24进制的分配

我们已经将整个24分成了3个八种情况,这样右边计数器的QA、QB、QC将作为主要输出,右边计数器的QD与左边计数器的QA作为控制端并且只有3种情况00,01,10。这样我们就应该将右边计数器的QD与左边计数器的QA作为74HC139四输入选择器的输入,而它的前三个输出就成为我们控制剩下的三个74LS138的使能端。而由于数据选择器输出的都是非,所以为了控制其他三个八选一数据选择器,我们应该将四选一数据选择器的输出连接八选一数据选择器的G2A非端。具体如图5所示。

图5----四选一数据选择器的输出输出

由图可知,1A端连接QD端,1B端连接QA端,八选一数据选择器的A、B、C端都连接的是右边计数器的QA、QB、QC端口,G1与VCC端连接的是高电压,G2B与GND端连接的是低电压或者接地。

2.3 24种情况分配给10盏灯

根据前面所分析,我们可以得出以下表格。1表示亮,0表示灭。

QA1 |

QD2 |

QC2 |

QB2 |

QA2 |

LED1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

表2.3.1----24种情况10盏灯的亮灭情况

令第一个八选一数据选择器为A,第二个八选一数据选择器为B,第三个八选一数据选择器为C。

由表可知:

LED1=YA0+YA6+YA7+YB0+YB1+YB2+YB3+YB4

LED2=YA0+YA1+YA2+YA3+YA4+YA5+YA6+YB4+YB5

LED3=YA0+YA1+YA6+YA7+YB0+YB1+YB2+YB3+YB4+YB5+YB6

LED4=YA0+YA1+YA2+YA3+YA4+YA5+YA6+YA7+YB4+YB5+YB6+YB7

LED5=YA0+YA1+YA2+YA6+YA7+YB0+YB1+YB2+YB3+YB4+YB5+YB6+YB7+YC0

LED6=YA0+YA1+YA2+YA3+YA4+YA5+YA6+YA7+YB0+YB4+YB5+YB6+YB7+YC0+YC1

LED7=YA0+YA1+YA2+YA3+YA6+YA7+YB0+YB1+YB2+YB3+YB4+YB5+YB6+YB7+YC0+YC1+YC2

LED8=YA0+YA1+YA2+YA3+YA4+YA5+YA6+YA7+YB0+YB1+YB4+YB5+YB6+YB7+YC0+YC1+YC1+YC2+YC3

LED9=YA0+YA1+YA2+YA3+YA4+YA6+YA7+YB0+YB1+YB2+YB3+YB4+YB5+YB6+YB7+YC0+YC1+YC2+YC3+YC4

LED10=YA0+YA1+YA2+YA3+YA4+YA5+YA6+YA7+YB0+YB1+YB2+YB4+YB5+YB6+YB7+YC0+YC1+YC1+YC2+YC3+YC4+YC5

以奇数部分为例:可以将一些公共部分挑出来作为一个整体一起通过与门作为一个分支。例如上面黄色部分与绿色部分则为奇数部分公共的。青色部分与粉色部分则为偶数LED灯公共的。

当然,有许多偶数部分与奇数部分共有的,也可将其挑选出来成为整体分支。

由于数据选择器输出的为非,所以还要将挑出来的分支再通过与非门才能得到最后的结果。最终连接如下图。

图6----24进制分配连接具体图

第三章 测试及结果分析

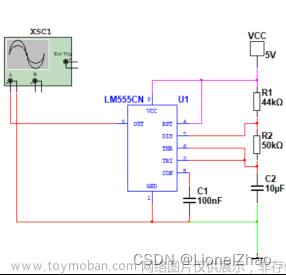

3.1 灯的好坏电路仿真测试

可以进行情况1,情况7以及情况13所有灯全亮,如果符合预期,则证明灯没有问题。

如图所示,和预计的一样,说明电路连接以及灯没有问题。

3.2 奇偶变化仿真测试

按照预计,情况2-情况6应该是1,3,5,7,9灯依次灭。

按照预计,按照预计,情况8-情况12应该是2,4,6,8,10灯依次灭。

由结果图可知,我们的预计和演示结果相同,说明奇数偶数部分是正确的。

3.3 依次灭灯仿真测试

按照预计,情况14-情况23应该是从LED1到LED10依次灭。

由图可知,结果正确。

3.4 整体仿真测试

按照题目要求,LED灯先奇数灯依次灭,再偶数灯依次灭,再由L0到L9,依次灭。而上图也完美证明了每个模块的正确,从情况1到情况23,都没有问题。说明整体电路合格。文章来源:https://www.toymoban.com/news/detail-796850.html

图26----整体电路图文章来源地址https://www.toymoban.com/news/detail-796850.html

有些地方上传有问题,无法达到预期,所以是截图!!!

到了这里,关于数字逻辑大作业----花样彩灯的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!