问题描述

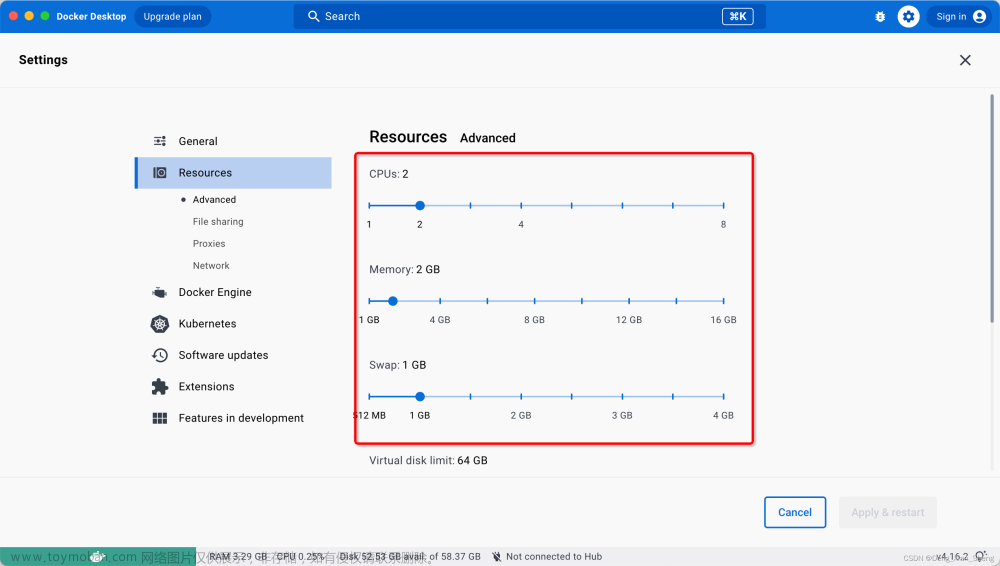

FPGA verilog 编程使用vscode,资源占用多 卡顿 卡死 内存占用多解决方案。

32G内存,动不动就暂用50%!!

解决方案

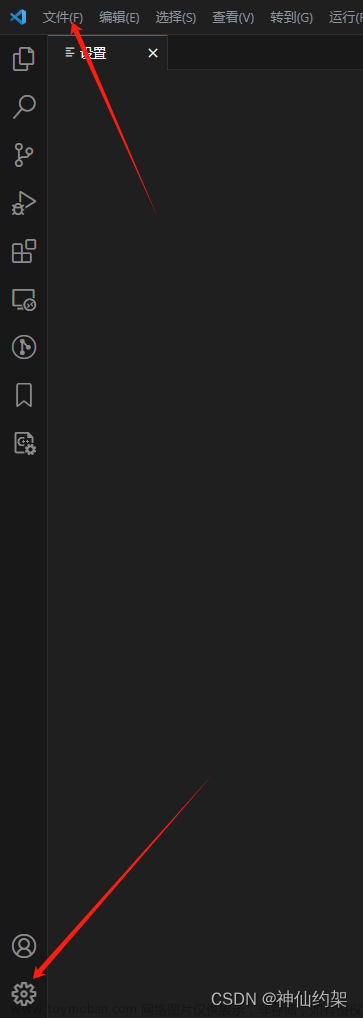

1.打开设置

文件->首选项->设置 或者点击软件界面的左下角的齿轮按钮

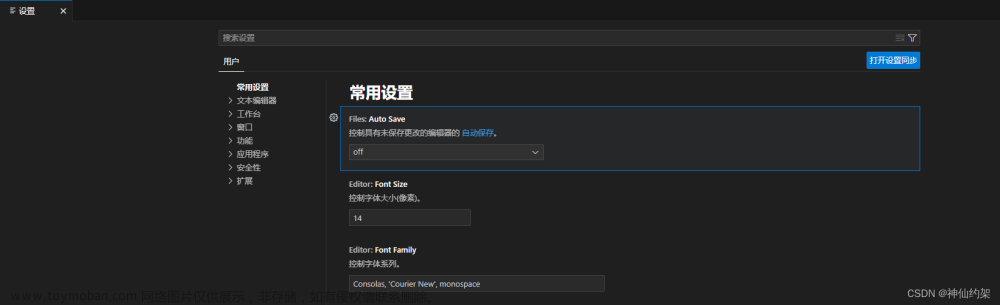

2.进入如下【设置】界面

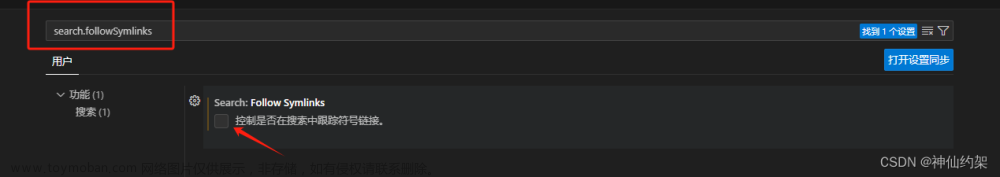

3.在上面搜索框中输入: search.followSymlinks,消除勾选

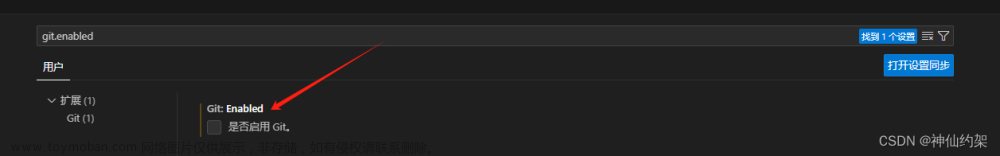

4.在上面搜索框中输入: git.enabled,消除勾选:不在vscode 启用 git 功能

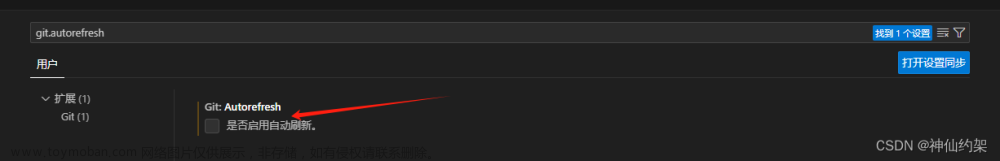

5. 在上面搜索框中输入: git.autorefresh,消除勾选:关闭自动保存或设置自动保存时间间隔延长文章来源:https://www.toymoban.com/news/detail-798336.html

文章来源地址https://www.toymoban.com/news/detail-798336.html

文章来源地址https://www.toymoban.com/news/detail-798336.html

到了这里,关于【学习】FPGA verilog 编程使用vscode,资源占用多 卡顿 卡死 内存占用多解决方案的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!