按时来更新了 不过由于作者这边的考试推迟 第八章I/O没有学到,不能全更了 不过我会把相应的练习题上传,对于第八章,大家可以给班里同学商量着做。

若是下周能学到,会第一时间补上。

6.控制器

7.总线

8.输入、输出设备

6.控制器

一、填空

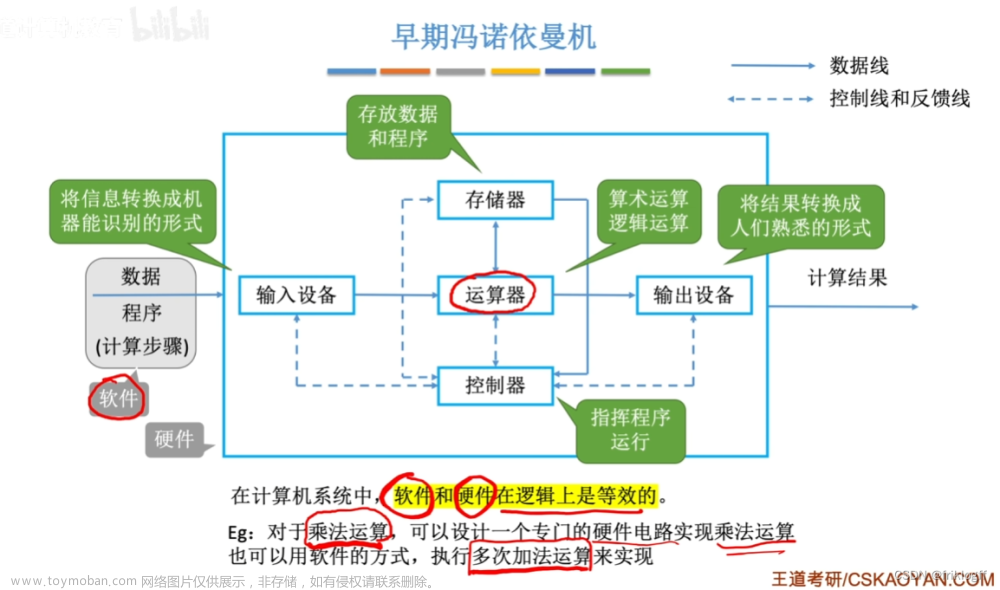

1. 控制器 是整台计算机的指挥系统,它指挥和控制全机的各个部分,使他们有条不紊的工作。

2.取指刚开始时,PC中包含的是 现行指令 。取指完成后,PC中包含的则是 下一条指令 。

3.指令从内存中取出后,要放到控制器的 指令寄存器 中,然后被分析,由控制器发出各种控制信号,控制有关功能部件执行指令。

4. 指令译码器ID 分析指令所代表的操作,产生相应的控制信号。

5. 控制器的功能包括 指令控制功能 、 时序控制功能 、 操作控制功能 、 数据加工控制功能 。

6.据微操作信号的产生方式不同,可把控制器分成 组合和逻辑 和 存储逻辑 两大类。

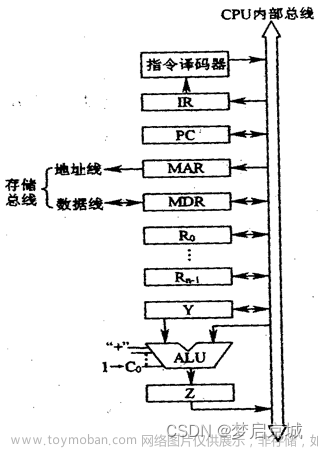

7. CPU中的专用寄存器主要有 程序计数器PC 、 指令寄存器IR 、 存储器数据寄存器MDR 、 程序状态字PSWR 、 存储器地址寄存器MAR 。

8. 从取指开始,到执行完该指令所需的全部时间称为 指令周期 。

9. 指令周期一定包含 取指 、 执行 周期,还可能包含 间址 、 中断 周期。

10.CPU执行一个基本操作所需的时间称为 机器周期 ,其一般以CPU在内存中读取一个指令字的最短时间来规定。

11. 机器主频16M,平均每条指令的执行时间为2个机器周期,每个机器周期由2个时钟周期组成,机器的速度为 4 MIPS。

12. 加速指令执行的方法是 超标量技术(空间并行) 、 (流水线技术)时间并行 。

13. 指令的 微程序控制 控制的思路是将一个复杂过程分成多个需时相等的子过程,每个子过程由一个独立的功能部件完成。

14. 在一个时钟周期内一条流水线可执行一条以上的指令。一条指令分为十几段指令来由不同电路单元完成,这种流水线称为 动态 流水线。

二、判断题

( F )1. 重迭不仅能加快一条指令的实现,只能加快相邻两条指令或一段程序的实现。

( T )2. 实现重迭,须以不增加功能部件(如:取指、分析、执行等)为前提。

( T )3. 流水线只能使用一套功能部件,要保证流水线的效率,必须使流水线不断流。

( T )4. 能用“关中断”指令来屏蔽的,只是可屏蔽中断,非屏蔽中断,不能用“关中断”来屏蔽。

( F )5. “关中断”指令能屏蔽所有类型的中断。

( T )6. CPU响应中断后就“关中断”,外来更高级别的中断需要中断处理时再响应。

( T )7. 非屏蔽中断一旦发生,CPU必须马上响应,因此,不能用“关中断”来屏蔽。

( F )8. 对中断源排队判优,不能由硬件实现,只能由软件实现。

( T )9. 对中断源排队判优,可由硬件实现,亦可由软件实现,硬件实现速度快,软件实现速度慢。

三、简答

1. 控制器的主要功能有哪些?

取指令

分析指令

执行指令

指令控制

时序控制

操作控制

数据加工控制

2. CPU中的专用寄存器主要有哪些?

指令寄存器(IR)

程序计数器(PC)

存储器地址寄存器(MAR)

存储器数据寄存器(MDR)

状态标志寄存器(PSW)

3.加法指令ADD R1,@R0,其含义为:((R0))+(R1)→R1 ,根据如图所示的数据通路,分析指令的执行过程。

PC->MAR

M[MAR]->MDR

MDR->IR

PC+1->PC

(R0)->MAR

M[MAR]->MDR

MDR->Y

R1->ALU

Z->R1

4. 为什么要有中断系统?

答:提出采用中断的原因主要为:

处理异常情况或特殊需求

提高CPU利用率

5. 什么是中断?中断与“转子”有何区别?

中断指计算机在运行过程中,遇到一些异常情况或特殊请求,CPU能暂停正在执行的程序,转去为外来请求服务,并在服务结束之后,自动返回原程序的过程或功能。

- 转子是事先设定好的,中断不可设置,是随机的

- 转子主-子程序有联系,而中断没有联系

- 中断过程较转子过程更复杂

6. CPU响应中断后,一开始就“关中断”,为什么?

为了在恢复原先程序的的过程中不被打断

- 什么是中断源的排队判优?

按照优先级给中断排好顺序,CPU运行过程中,优先响应优先级高的中断,这个过程就叫做排队判优。

四、分析与计算

1.中断响应顺序1→2→3→4,CPU在为1服务时,来了2的请求,为2服务时,来了3的请求,依此类推。处理优先次序为:1→3→4→2,如何处理?给出屏蔽字,画出中断过程示意图。

| 1 |

2 |

3 |

4 |

|

| 1 |

1 |

1 |

1 |

1 |

| 2 |

0 |

1 |

0 |

0 |

| 3 |

0 |

1 |

1 |

1 |

| 4 |

0 |

1 |

0 |

1 |

2.机器共有4级中断,中断响应次序为1→2→3→4,处理次序为1→3→4→2,CPU在为中断1服务时,同时来了2、4的请求,在处理4未完时,又来了3的请求。给出屏蔽字,画出中断过程示意图。

| 1 |

2 |

3 |

4 |

|

| 1 |

1 |

1 |

1 |

1 |

| 2 |

0 |

1 |

0 |

0 |

| 3 |

0 |

1 |

1 |

1 |

| 4 |

0 |

1 |

0 |

1 |

3.机器共有4级中断,中断响应次序为1→2→3→4,若处理顺序为1→4→2→3,CPU在为1服务时,同时来了2、3、4的请求。给出屏蔽字,画出中断过程示意图。

| 1 |

2 |

3 |

4 |

|

| 1 |

1 |

1 |

1 |

1 |

| 2 |

0 |

1 |

1 |

0 |

| 3 |

0 |

0 |

1 |

0 |

| 4 |

0 |

1 |

1 |

1 |

7.总线

一、填空

1. 总线 是连接各个部件的信息传输线,是各个部件共享的传输介质。

2. 总线是 连接各个信息的传输线,是各个部件共享的传输介质 。

3. 总线上信息的传送分为 单向传输 和 双向传输 。

4. 总线分为 片内总线 、 系统总线 和通信总线。

5. 总线带宽是指 单位时间上总线传输的数据位数 。

6. 假设总线的时钟频率是50MHz,总线的传输周期为2个时钟周期,总线的宽度为32位,则总线的带宽为 100Mbps 。采取 总线宽度增加一倍 的措施,可提高一倍的带宽。

7. 异步通信中主设备和从设备之间的应答方式分为 不互锁 、 半互锁 和 全互锁 三种方式,它们分别应用于单机、多机及网络通信中。

8. 在异步串行传输系统中,若字符格式为:1个起始位,8个数据位,1个奇校验位、1个终止位。假设波特率为1 200bps,其比特率为 872.73 。

9. 总线判优控制的目的是 解决多个部件同时申请总线的使用权分配问题 。

10. 总线判优 解决多个部件同时申请总线时的使用权分配问题。

11. 给出计算机主板上4个以上的部件 CPU插板 、 主存插板 、 I/O插板 、 线路插板 。

二、判断题

( T )1. 数据总线是双向的。

( T )2. 地址总线是单向的。

( T )3. 控制总线有出有入。

( T )4. 数据总线和控制总线是双向的,地址总线是单向的。

( F )5. 总线通信控制的目的是解决通信双方协调配合问题。

( T )6. 总线判优控制的目的是解决多个部件同时申请总线时的使用权分配问题。

( T )7. 总线的同步通信由统一时标控制数据传送。

( F )8. 总线的同步通信采用应答方式,有统一时标控制数据传送。

( T )8. 总线的异步通信采用应答方式,没有公共时钟标准。

( F )9. 总线的同步通信和异步通信均有统一的时标控制数据传送。

( F )10. 总线的同步通信和异步通信均采用应答方式进行通信。

( T )11. 计算机主板上的各个I/O部件都与总线相连。

三、简答

1. 总线分为哪几种类型?

片内总线

系统总线

通信总线

- 总线的特性包含哪几个方面的特性?

机械特性

电器特性

功能特性

时间特性

- 假设总线的时钟频率是50MHz,总线的传输周期为2个时钟周期,总线的宽度为32位,试求总线的带宽。若想提高一倍的带宽,可采取什么措施?

100Mbps

增加一倍总线宽度 减小一倍时间周期 增加一倍时钟频率

4.总线控制部件采用链式查询方式进行总线判优控制,当I/O接口1和 I/O接口5同时提出总线的申请,简述其判优控制过程。总线控制部件把总线的控制权分配给哪个I/O接口?

- 在异步串行传输系统中,假设每秒传输120个数据帧,其字符格式规定包含1个起始位,8个数据位,1个奇校验位、一个终止位,试计算其波特率。

120*11 = 1320波特

6. 在异步串行传输系统中,若字符格式为:1个起始位,8个数据位,1个奇校验位、一个终止位。假设波特率为1 200bps,试计算其比特率。

比特率:单位时间内传送二进制有效数据的位数。

1200*(8/11) = 872.73bps

8.输入输出设备

1. I/O 设备的编址方式有 统一 编址和 不统一 编址。

2. I/O设备通过 接口 和主机连接在一起。

3. 总线连接方式的 I/O 接口通过 、 、 、

和CPU连接。

4. CPU的工作周期为20ns,主存存取周期为10ns,此时DMA接口适合采用 方式与CPU共享主存。

二、判断题

( )1. 接口能够实现数据缓冲,达到速度匹配。

( )2. 接口能够实现数据串并格式转换。

( )3. 接口能够实现电平转换。

( )4. 接口能够反映设备的状态。

三、简答题

1. 当你按下键盘上的一个键时,系统是如何知道你按下了一个键?按下的是哪个键?如何把该信息读入CPU?

2. 为什么计算机要设置接口?

3. DMA方式的特点有哪些?

4. DMA与主存交换数据有哪三种方式?

四、计算

1. 一个DMA接口可采用周期窃取方式把字符传送到存储器,它支持的最大批量为600个字节。若存取周期为100ns,每处理一次中断需10µs,现有的字符设备的传输率为9 600bps。假设字符之间的传输是无间隙的,若忽略预处理所用的时间,试问采用DMA方式每秒因数据传输需占用处理器多少时间?若采用中断方式,又需占用处理器多少时间?

总结:时间紧任务重,难免有错误,请大家帮忙指正。如果大家不理解哪个题,请将问题留在评论区,我会一一回复。

若此篇对您有帮助,请多多点赞关注

最后祝大家期末取得理想成绩~~文章来源:https://www.toymoban.com/news/detail-799578.html

第八章会在学完后在此篇进行更改 文章来源地址https://www.toymoban.com/news/detail-799578.html

到了这里,关于计算机组成原理期末考试知识点练习题(补发)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!