前言

很多INTEL(ALTERA) IP生成的时候会自带例程,如LVDS SERDES IP,在菜单Generate中可以选择生成官方例程。

之后会在IP所在目录下生产【lvds_0_example_design】文件夹,但在这个文件夹中并没有FPGA工程。

例程在哪?

查看readme.txt。

This is the readme.txt file for the example design file set of the Altera

LVDS SERDES IP. Files in this directory allow you to do

the following:1) Create a Quartus Prime project that instantiates an LVDS

interface (same configuration as what you specified in generation).

You can optionally specify the target device and pin location

assignments, run a full compilation using the Quartus Prime software,

verify timing closure, and test the interface on your board using the

programming file generated by the Quartus Prime assembler.

2) Create simulation projects for various supported simulators. The

simulation projects instantiate an LVDS interface (same

configuration as what you specified in the MegaWizard),

and an example test bench that exercises the interface.

The projects are generated so you can run simulation and use the

results as a way to understand the behavior of the LVDS

interface IP. This flow only supports functional simulation. Timing

simulation is not supported, and you must use static timing analysis

provided by the TimeQuest software to verify timing closure.

Notes:

In external PLL mode, an example external PLL is provided in a

standalone QSYS file (lvds_external_pll.qsys).

This can be modified and used in the user's design for external

PLL mode.

In the synthesis example design, there is an example of how to

connect the external PLL to the LVDS IP including a top-level

SDC file.

The file under the qsys_interface_bridge directory:

qsys_interface_bridge_hw.tcl defines a custom component to help

connect LVDS to the PLL in QSYS. It simply allows the connection

between non-matching QSYS interfaces (i.e. clock to conduit).

Make sure these files are added to the project directory if you

wish to modify either the synthesis or simulation QSYS systems.

The qsys_interface_bridge is not needed if using the provided PLL as a

RTL instantiation and connecting the components manually in RTL

rather than a QSYS system.###############################################################################

Generating a Quartus Prime Example Design

###############################################################################

For information about supported arguments, run:

quartus_sh -t make_qii_design.tcl -help

To generate a Quartus Prime example design, run:

quartus_sh -t make_qii_design.tcl

To specify an exact device to use, run:

quartus_sh -t make_qii_design.tcl -device [device_name]

The generated example design is stored under the "qii" sub-directory.

To re-generate the design, simply delete it and re-run the commands above.

To generate non-default example designs like the DPS (Dynamic Phase Shift),

combined TX/RX or others:

quartus_sh -t make_qii_design.tcl -device [device_name] -system [system_name]Note: [system_name] is the name of the QSYS system for the given example design.

For the default "ed_synth.qsys" the system name is "ed_synth".The generated example design is stored under the "qii_<system_name>" sub-directory.

###############################################################################

Generating a Simulation Example Design

###############################################################################

To generate simulation example designs for a Verilog or a mixed-language

simulator, run:quartus_sh -t make_sim_design.tcl VERILOG

To generate simulation example designs for a VHDL-only simulator, run:quartus_sh -t make_sim_design.tcl VHDL

The generated example designs for various simulators are stored under the "sim"

sub-directory. For example, to run simulation using Synopsys' VCS, run:cd sim/synopsys/vcs

./vcs_setup.sh

其中提到

To generate a Quartus Prime example design, run:

quartus_sh -t make_qii_design.tcl

也就是说运行这句TCL就可以生产例程。

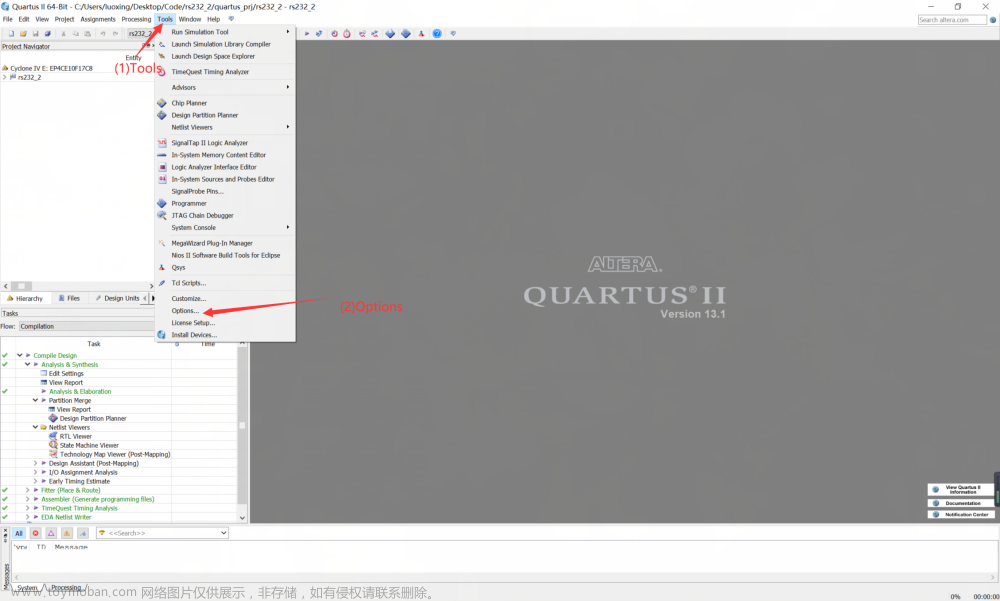

运行TCL

1.在当前文件夹新建文本文件,更改后缀名为bat

2.把“quartus_sh -t make_qii_design.tcl ”复制到文本文件。

3.双击运行bat文件,会弹出cmd窗口,等待一会。

4.会在当前目录下产生文件夹【qii】 ,这个就是例程的FPGA工程。

TCL无法运行怎么办

大概率是系统环境变量设置错误。需要在环境变量中是否添加了Quartus II。

系统属性 --- 环境变量 --- 用户变量 --- Path,添加

*\quartus\bin64

延展阅读:文章来源:https://www.toymoban.com/news/detail-799928.html

震惊!FPGA配置居然一键完成! - 知乎文章来源地址https://www.toymoban.com/news/detail-799928.html

到了这里,关于【INTEL(ALTERA)】如何使用Tcl打开quartus IP自带的例程的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!