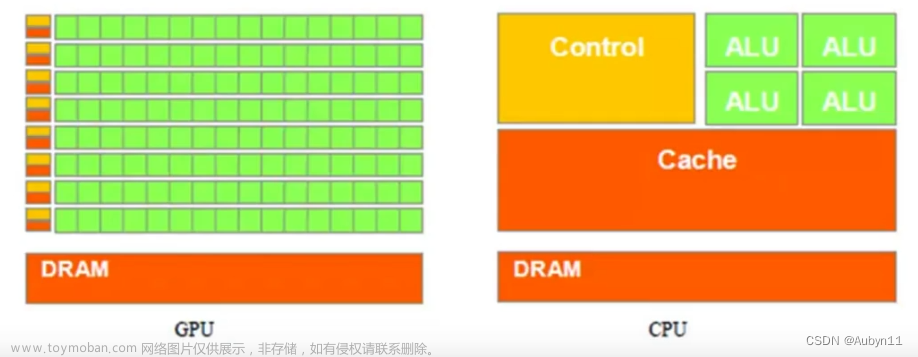

数值控件选板上的大部分数学函数都支持整数或定点数据类型,但是需要请注意,避免使用乘法、除法、倒数、平方根等函数,此类函数比较占用FPGA资源,且如果使用的是定点数据或单精度浮点数据仅适用于FPGA终端。

1.整数运算

支持的数据类型:

- 8位有符号和无符号整数数值

- 16位有符号和无符号整数数值

- 32位有符号和无符号整数数值

- 64位有符号和无符号整数数值

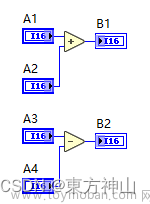

1.1加减法

1.2乘除法

为了节省FPGA资源,最好不直接用FPGA上乘的除法函数。一般可以用 商与余数 和 按2的幂缩放 。(但是在FPGA里,乘法需要先转成二进制做加法运算,再做乘法,除法也是先转成二进制做减法在做除法)

除法函数可以用商与余数替代,但是这同样会使用较多FPGA资源。

乘除法可以用 按2的幂缩放 替代。

如果想把数据按非整数缩放,比如0.4。那就需要先乘再缩放。

2.二进制运算

3.定点数运算

定点数表示用户指定范围和精度内的有理数。定点数的大小在1-64位之间。可配置定点数为带符号或不带符号。

以定点数据类型表示有理数

定点数具有固定个数的整数位和分数位。整数位和分数位分别在二进制点的左、右两侧。由于定点数可指定其确切的位数,故二进制小数点的位置是固定的。

例如,在LabVIEW中,有理数0.5可表示为一个总位数为8、整数位为4的定点数。

| 有理数 | 对应的定点数 |

|---|---|

| 0.5 | 0000.1000 |

在LabVIEW中,同一个有理数也可表示为一个总位数为16、整数位为8的定点数。

| 有理数 | 对应的定点数 |

|---|---|

| 0.5 | 00000000.10000000 |

| 注: 以定点数表示有理数时,如未指定定点数确切的位数,LabVIEW将调整定点数的位数,尽量避免数据丢失。LabVIEW无法处理大于64位的数字。 |

配置定点数

要将一个数设置为定点表示法,右键单击数据对象,从快捷菜单中选择表示法,改变对象的数据类型。可配置定点数的编码。还可指定定点数是否包括上溢状态,以及数值函数如何处理定点数的上溢和凑整。如要配置一个定点数,右键单击常量、控件,或数值函数,从快捷菜单中选择属性,打开数值属性、数值常量属性或数值节点属性对话框进行配置。

编码

如要数值的比特数为特定值,需指定定点数的二进制编码方式。

- 有符号-指定定点数据是否带符号。如选择有符号,则符号位总在表示数据的位字符串的第一位。

- 无符号-指定定点数据是否有符号。

- 字长-位字符串的总位数,是LabVIEW表示定点数据时的位数。LabVIEW接受的最大字长为64位。某些终端可能仅支持字长较短的数据。如在终端上打开一个VI而VI包含的定点数大于终端所能接受的字长,则VI出现断线。参考终端的相关文档,确定终端接受的最大字长。

- 整数字长-指位字符串中LabVIEW用于表示定点数的整数位数,或从最高有效位左侧或右侧的初始位置开始,将二进制小数点移动到最高有效位所需的位数。整数字长的长度可以大于字长,可以为正也可以为负。

例如:

<s, 16, 8>是一个整数位为8的16位有符号数。下图表示一个字长为16、整数字长为8的有符号数。

| 1 | 字长(16位) |

| 2 | 整数字长(8位) |

| 3 | 符号位 |

| 4 | 二进制小数点 |

长整数或负整数字长

如整数字长大于字长,则LabVIEW不保存超过字长的那部分整数位。下图表示一个字长为8、整数字长为10的数。

| 1 | 字长(8位) |

| 2 | 整数字长(10位) |

| 3 | 整数位未保存 |

| 4 | 二进制小数点 |

如整数字长为负,LabVIEW将不保存任何整数位,并且也不保存从二进制小数点算起与负数相同的分数位。下图表示一个字长为8、整数字长为-2的数。

| 1 | 字长(8位) |

| 2 | 字长-整数字长(8位-2位) |

| 3 | 分数位未保存 |

| 4 | 二进制小数点 |

范围

LabVIEW根据用户为定点数指定的编码值计算定点数的范围和delta。

- 最小值-设置定点数据范围的最小值。

- 最大值-设置定点数据范围的最大值。

- Delta-指定范围内数字间的增量。

将光标移动到传递定点数据的连线上时,LabVIEW在即时帮助窗口中以下列格式表示该定点数据的配置情况:

[最小值,最大值]:Delta

例如:

[–4, 4]:1的最小值为–4,最大值为4,delta为1。

定点算术

对指定字长的定点数进行算术运算时,二进制小数点的位置与VI运行之前二进制小数点的位置相同,并无改变。这与浮点数恰好相反,进行浮点数算术运算时,浮点数的二进制小数点或十进制小数点的位置将改变。如算术运算所要求的字长大于定点数的字长,则运算后可能导致数据损失。

LabVIEW将调整数值函数的输出值的字长以尽量避免数据损失。然而,如表示输出值所要求的字长超出了指定的最大范围或LabViEW所允许的64位,则LabVIEW无法避免数据损失。如要配置数值函数的输出设置,右键单击函数,从快捷菜单中选择属性,打开数值节点属性对话框进行配置。

上溢和凑整

对定点数进行算术运算或使用转换为定点数函数将数值数据转换为定点数据时,都可能发生上溢和凑整。通过配置,LabVIEW可避免数值函数输出的定点数发生溢出或凑整。但在某些条件下LabVIEW无法避免溢出或凑整。

例如,将定点值连线数值函数(加、减、乘、平方),LabVIEW将默认为增加输出值的字长以使运算结果得以正常显示。此做法同样适用于浮点值。然而,如避免溢出或凑整所要求的字长超出了LabVIEW可接受的最大字长或用户指定的最大字长,则溢出或凑整可能无法避免。LabVIEW接受的最大字长为64位。

| 注: 如将一个定点值连接至除函数、倒数函数、平方根函数,因为精度无穷,所以经常会发生凑整状态。 |

在二进制中无法确切表示的类型周期和值也可能导致溢出或凑整。

溢出

当运算结果在输出类型能表示的值的范围外时,将发生溢出。可为溢出选择下列溢出模式进行处理:

- 饱和-如输出值大于输出类型可接受范围的最大值,LabVIEW将强制,即对将该值四舍五入至指定的最大值。如值小于可接受范围的最小值,LabVIEW将值强制转换为指定的最小值。

- 绕回-如输出值在输出类型可接受范围之外,LabVIEW将舍弃输出值的有效位,直到输出值位于输出类型的可接受范围内。该选项要求输出值符合指定的编码方式。如选择该选项便无法指定可接受范围,因为LabVIEW将自动使范围符合编码方式。

| 注: 通常情况下,饱和模式需要FPGA终端上额外的硬件资源。 |

将定点数配置为包括上溢状态,确定是否发生上溢。如定点值包括上溢状态,LabVIEW将分配额外的存储空间,用于追踪作为计算结果的定点值是否溢出。将定点数配置为包括上溢状态后,可在定点数控件和常量上显示上溢状态LED。定点值的溢出状态为TRUE时,LED灯亮。也可使用定点溢出?函数确定定点数的上溢状态。定点函数可对定点数字的溢出状态进行操作。

| 注: LabVIEW不检查定点数的下溢情况。 |

使用比较函数比较定点数时,LabVIEW将忽略上溢状态,只比较数值。例如,如使用等于?函数比较上溢状态为TRUE的定点数和数值为1.5,无上溢状态的定点数,LabVIEW将返回TRUE。

如要配置数值函数的输出设置,右键单击函数,从快捷菜单中选择属性,打开数值节点属性对话框进行配置。该对话框用于配置LabVIEW处理溢出和凑整。

凑整

当输入值或运算结果的精度大于输出类型的精度时,将发生凑整。LabVIEW将输入值强制为一个与输出类型精度相同的值。例如,假设输出类型可表示下列连续值s和t。如运算结果为x,且x在s和t之间,即s<x<t,由于输出类型无法精确表示x,所以需要进行凑整。

可为凑整选择下列凑整模式进行处理:

-

截断舍入-向下取整到输出类型能表示的最近值。LabVIEW将舍弃值的最低有效位。取整模式的性能最佳,但得到的输出值精度最低。

例如,如输出值x在连续值s和t之间,即

s<x<t,

则LabVIEW将x设为与s相同。 -

半值向上-取整到输出类型能表示的最近值。如值正位于两个有效值之间,该模式将值取整为两个有效值中较大的一个。LabVIEW在输出值上加上最低有效位的一半,然后截断该值。这种取整模式比阶段模式的输出值更准确,但对性能影响较大。

例如,如输出值x在连续值s和t之间,即

s<x<t,

LabVIEW将x设为等于s或t二者之中较近的那个值。如x正位于s和t之间,则LabVIEW将选择使x等于t。 -

奇偶舍入-取整到输出类型能表示的最近值。如取整的值刚好在两个有效值之间,LabVIEW将检查该值中取整后将成为最低有效位的位。如该位为0,该模式将把值取整到两个值中输出类型能表示的较小的值。如该位不为0,该模式将值取整到两个值中较大的值。取整模式对性能的影响最大,但其输出值比截断模式更准确。该模式也将并且中和了进行多次半值向上的取整时可能出现的趋向较大值的倾向。该模式为默认取整模式。

例如,如输出值x在连续值s和t之间,即

s<x<t,

LabVIEW将x设为等于s或t二者之中较近的那个值。如x正位于s和t之间,如取整后最小有效位为0时,选择s;如取整后最小有效位不为0时,选择t。如取整后最小有效位不为0时,选择t。

| 注: 取整模式对性能的影响都微乎其微。但是,如在FPGA的终端运行处理溢出的VI,则取整可能会对性能有较大的影响。 |

定点配置对FPGA资源的影响

在FPGA VI中使用定点数时,为特定函数选择正确的溢出和四舍五入模式非常重要。高吞吐率数学函数和部分数值函数带有配置对话框,可用于模式选择。如能够产生溢出或四舍五入,这些模式将影响FPGA VI所需的FPGA资源量。如不能产生溢出或四舍五入,操作不需要使用额外的FPGA资源。

多数情况下,在函数的配置对话框中勾选匹配至源复选框可避免溢出。如勾选此复选框,LabVIEW将尝试调整输出数据类型的宽度和范围,从而不会产生溢出或四舍五入。但此调整并不适用于所有情况。例如,函数包含除法时会一直产生四舍五入。且某些函数不包含此复选框。

溢出模式的影响

通常溢出模式以下列几种方式影响FPGA资源:

- 饱和-需要FPGA资源判定输入值是否位于输出类型的范围内并选择返回原始值或饱和值。

- 截位-所需的FPGA资源少于饱和模式。

四舍五入模式的影响

通常四舍五入模式以下列几种方式影响FPGA资源:

- 截断舍入-移除位,因此不需要占用FPGA资源。但此模式对于多数数据流将产生最大的平均误差。此模式为整型操作的默认模式。

- 半值向上(非对称)-添加至输出数据类型的最低有效位。此选项需要一个宽度等于输出数据类型的加法器。

- 奇进偶舍-所需FPGA资源最多,且在三种舍入模式中生成最长的组合路径。但此模式对于多数数据流可返回统计意义上最正确的结果,因此其为定点数据类型的默认四舍五入模式。

|

注: 高吞吐率除和高吞吐率倒数函数使用输出值向零取整的四舍五入模式。此模式将输出值四舍五入为数据类型能够表示的最接近的值。如值为整数,LabVIEW进行截断取整。如值为负数,假设至少有一位删除的位不为零,LabVIEW删除最低有效位(LSB)并为剩余的LSB添加符号位。 例如,输出值x位于连续值s和t之间(s < x < t),如x为正数,LabVIEW设置x等于s。如x为负数,LabVIEW设置x等于t。 对于这两个函数,与其它四舍五入模式相比,向零取整使用的FPGA资源最少。不能为这些函数指定不同的四舍五入模式。 |

如何将定点数缩放到整数的整个范围

LabVIEW 中可用于将定点 (FXP)转换 为整数或浮点的 函数有:

- 定点到整数转换 用于转换整数。

- 用于转换任何数值数据类型的 定点函数。

将任意大小的 FXP 缩放为整数

定点到整数转换可用于将 FXP 数字转换为整数,并且整数的大小将基于 FXP 数字的大小。例如,如果您的 FXP 的字长为 8 位,则会将其转换为 I8,但字长为 9 的 FXP 将转换为 I16。(字和整数字长描述)

这在某些情况下可能没问题,但是如果我们需要将任何FXP(任何字长)转换为特定大小的整数,例如将任何大小的 FXP 转换为 I16,我们需要将该 FXP 转换为在使用定点到整数转换之前,字长为 16 位:

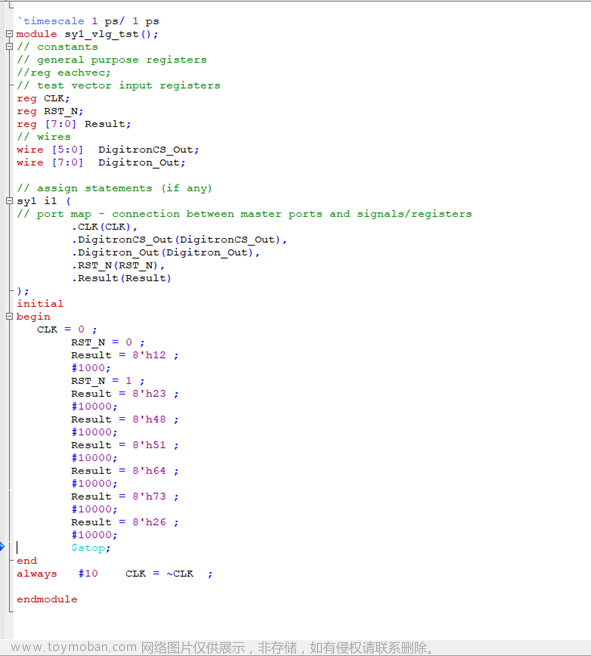

1.创建您的初始 FXP 编号,这可以来自 FPGA I/O、常数或控件。

如果使用控件或常量,您可以右键单击它,选择“属性”=>“数据类型” 并编辑字长和整数字长。设置 字长 = 4 位,整数字长 = 2 位。

2.将 FXP 控件(或常数)连接到 定点 转换函数,并将输出配置设置为 16 位。

3.右键单击 “到定点” 并选择 “属性”=>“输出配置”。将编码设置为带符号, 字长 = 16 位,整数字长 = 2 位。这将确保输出设置为 16 位有符号整数 (I16),这意味着 I16 数字的整个范围为 -32768 I16 到 +32767 I16,而无符号 16 位整数 (U16) 的范围为 0 到 65535

4.将定点 转换函数的输出连接到定点到整数转换 函数。其输出将是一个 16 位整数,缩放到正确的范围。

将整数转换回 FXP

要转换回定点数,请反转函数。1.将整数连接到 整数到定点 函数,

将已知的 FXP 值连接到整数到定点转换函数 上的 定点类型输入。可以使用控件或常量,只要具有与初始 FXP 数字相同的属性(字和整数字长度)即可确保其以正确的格式转换回来。或者,将初始 FXP 值直接连接到定点类型 输入。

注意:它不是 必需的 输入,但建议连接,以便您更好地控制功能。  文章来源:https://www.toymoban.com/news/detail-800695.html

文章来源:https://www.toymoban.com/news/detail-800695.html

2.整数到定点 转换的输出 将是一个 FXP 数字,其属性与初始 FXP 数字相同。文章来源地址https://www.toymoban.com/news/detail-800695.html

到了这里,关于【LabVIEW FPGA入门】FPGA中的数学运算的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!