1. 什么是FPGA

-

这个问题太low了,身处数字时代,从事电子信息行业,居然不知道FPGA?岂非笑谈?

-

介绍FPGA的资料太多了,还是从它的字面上来初识它吧。

-

FPGA,Field-Programmable Gate Array,每个单词意义如下:

- Field:现场,指的是在最终实际运行的现场(数字芯片)上直接硬件编程。

- Programmable:可编程的,意味着硬件功能可以通过编程来改变。

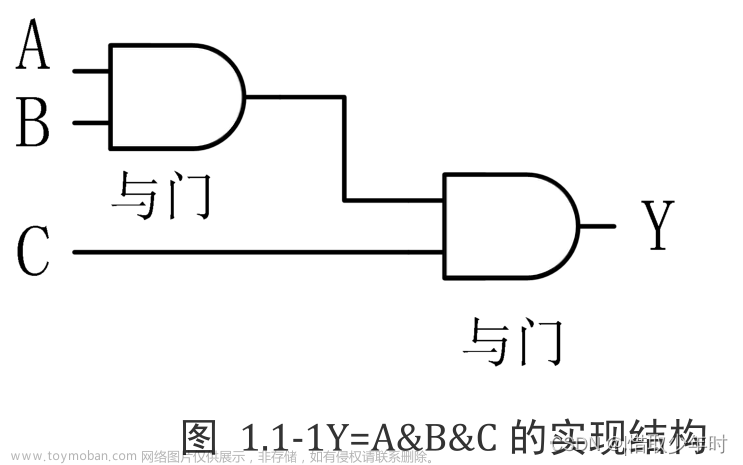

- Gate:门,指的是逻辑门电路,门电路是数字电路的基本单元。

- Array:阵列,指的是FPGA内部的结构布局,由大量的逻辑门电路有规则的排列而成。

合起来:现场可编程逻辑门阵列,它是:

-

一种最初由赛灵思发明的可硬件编程芯片;

-

一种利用EDA软件进行逻辑设计,用它来实现设计的半定制集成电路;

-

一种新的数字系统实现方法与平台;文章来源:https://www.toymoban.com/news/detail-800812.html

-

人工智能时代的耀眼明星;文章来源地址https://www.toymoban.com/news/detail-800812.html

2. 学习FPGA有什么用

- 职场生涯:建立技术壁垒,提高个人在电子信息市场的竞争力

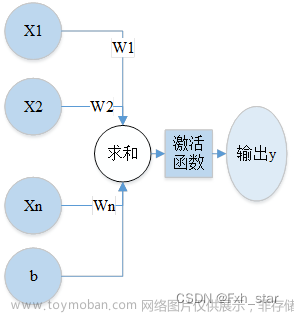

- 基础研究:提供AI底层技术支撑

3. 学习FPGA需要何种先决条件

- 掌握逻辑代数的基本理论与方法

- 掌握数字电路的基本分析与设计方法

- 组合电路分析与设计方法

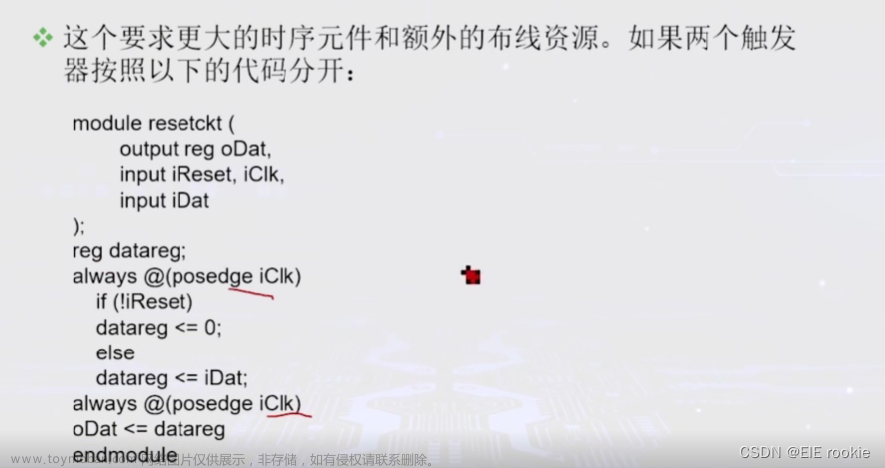

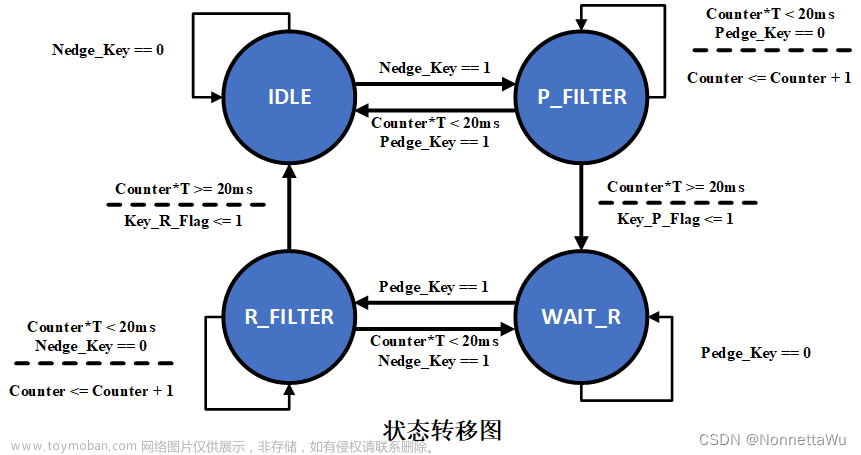

- 时序电路分析与设计方法

- 脉冲波形的变换与产生原理(可选)

上述先决条件都是数字电路基础的内容。

不具备以上先决条件,会遇到什么问题?

遇到的问题就像梅超风练九阴真经

到了这里,关于1. FPGA概述的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!