题目:

Since digital circuits are composed of logic gates connected with wires, any circuit can be expressed as some combination of modules and assign statements. However, sometimes this is not the most convenient way to describe the circuit. Procedures (of which always blocks are one example) provide an alternative syntax for describing circuits.

For synthesizing hardware, two types of always blocks are relevant:

Combinational: always @(*)

Clocked: always @(posedge clk)

Combinational always blocks are equivalent to assign statements, thus there is always a way to express a combinational circuit both ways. The choice between which to use is mainly an issue of which syntax is more convenient. The syntax for code inside a procedural block is different from code that is outside. Procedural blocks have a richer set of statements (e.g., if-then, case), cannot contain continuous assignments, but also introduces many new non-intuitive ways of making errors. *(*Procedural continuous assignments do exist, but are somewhat different from continuous assignments, and are not synthesizable.)

For example, the assign and combinational always block describe the same circuit. Both create the same blob of combinational logic. Both will recompute the output whenever any of the inputs (right side) changes value.

assign out1 = a & b | c ^ d;

always @(*) out2 = a & b | c ^ d;

我的解法:

// synthesis verilog_input_version verilog_2001

module top_module(

input a,

input b,

output wire out_assign,

output reg out_alwaysblock

);

assign out_assign=a&b;

always @(*) out_alwaysblock=a&b;

endmodule

结果正确:

此题考查两种赋值方法:

两种类型:

output wire out_assign

output reg out_alwaysblock

对应两种不同赋值方法:文章来源:https://www.toymoban.com/news/detail-801178.html

assign out_assign=a&b;

always @(*) out_alwaysblock=a&b;

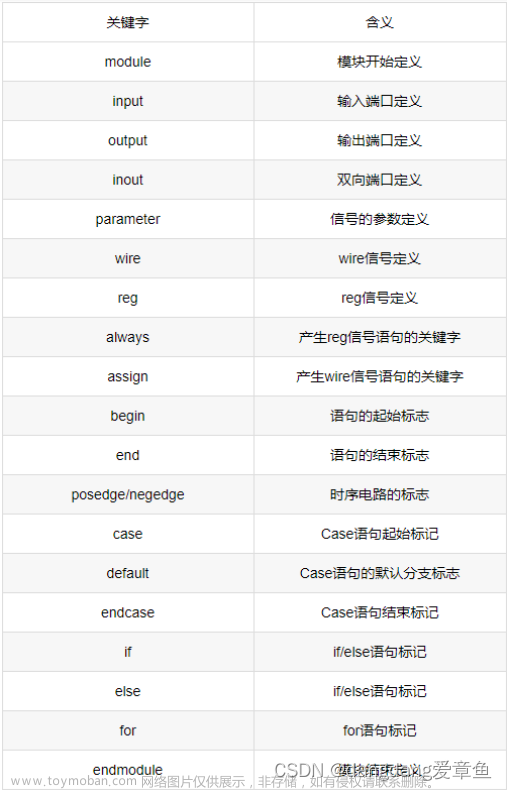

关于 wire 与 reg 的说明:赋值语句的左侧必须是 net 类型(例如,wire),而过程赋值的左侧(在 always 块中)必须是变量类型(例如,reg)。这些类型(wire 与 reg)与合成的硬件无关,只是 Verilog 用作硬件仿真语言时遗留下来的语法。文章来源地址https://www.toymoban.com/news/detail-801178.html

到了这里,关于Verilog刷题笔记16的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!