🌈个人主页:Sarapines Programmer

🔥 系列专栏:《机组 | 模块单元实验》

⏰诗赋清音:云生高巅梦远游, 星光点缀碧海愁。 山川深邃情难晤, 剑气凌云志自修。

目录

🌺一、 实验目的

🌼二、 实验内容

🌻三、 实验详情

实验1:数据输入通用寄存器

实验2:寄存器内容无进位位左移实验

实验3:寄存器内容无进位位右移实验

🍀四、 实验步骤

实验1 数据输入通用寄存器

实验2 寄存器内容无进位位左移实验

实验3 寄存器内容无进位位右移实验

🌿五、 实验结果

🌷六、 实验体会

📝总结

🌺一、 实验目的

- 掌握寄存器组成及硬件电路;

- 掌握通用寄存器单元的工作原理运用。

🌼二、 实验内容

- 数据输入通用寄存器;

- 寄存器内容无进位位左移实验;

- 寄存器内容无进位位右移实验。

🌻三、 实验详情

实验1:数据输入通用寄存器

● 把RA-IN(8芯的盒型插座)与右板上二进制开关单元中的J01插座相连(对应二进制开关H16~H23),把RA-OUT(8芯的盒型插座)与数据总线上的DJ6相连。

● 把RACK连到脉冲单元的PLS1,把ERA、X0、X1、RA-O、M接入二进制拨动开关。(请按下表接线)。

| 控制信号 |

接入开关位号 |

| RACK |

PLS1 孔 |

| X0 |

H12 孔 |

| X1 |

H11 孔 |

| ERA |

H10 孔 |

| RA-O |

H9 孔 |

| M |

H4 孔 |

接线图示:

● 二进制开关H16~H23作为数据输入,置42H(对应开关如下表)。

| H23 |

H22 |

H21 |

H20 |

H19 |

H18 |

H17 |

H16 |

数据总线值 |

| D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

8位数据 |

| 0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

42H |

置各控制信号如下:

| H12 |

H11 |

H10 |

H9 |

H4 |

| X0 |

X1 |

ERA |

RA-O |

M |

| 1 |

1 |

0 |

0 |

1 |

● 按启停单元中的运行按钮,置实验平台为运行状态。

● 按脉冲单元中的PLS1脉冲按键,在RACK上产生一个上升沿,把42H打入通用寄存器。

●此时数据总线上的指示灯IDB0~IDB7 应该显示为42H。由于通用寄存器内容不为0,所以LED(ZD)灯灭。

实验2:寄存器内容无进位位左移实验

● 按照实验1数据输入的方法把数据42H打入通用寄存器中,数据总线上显示42H。实现左移功能,置各控制信号如下:

| H12 |

H11 |

H10 |

H9 |

H4 |

| X0 |

X1 |

ERA |

RA-O |

M |

| 0 |

1 |

0 |

0 |

1 |

● 按启停单元中的运行按钮,置实验平台为运行状态。

● 按脉冲单元中的PLS1脉冲按键,在RACK上产生一个上升沿,使通用寄存器中的值左移。

● 此时数据总线上的LED指示灯IDB0~IDB7 应该显示为84H。由于通用寄存器内容不为0,所以ZD(LED)灯灭。

● 按脉冲单元中的PLS1脉冲按键,使通用寄存器中的值左移,此时数据总线上的LED指示灯IDB0~IDB7应该显示为09H。若一直按PLS1,在总线上将看见数据循环左移的现象。

实验3:寄存器内容无进位位右移实验

● 按照实验1数据输入的方法把数据42H打入通用寄存器中,数据总线上显示42H。实现右移功能,置各控制信号如下:

| H12 |

H11 |

H10 |

H9 |

H4 |

| X0 |

X1 |

ERA |

RA-O |

M |

| 1 |

0 |

0 |

0 |

1 |

● 按启停单元中的运行按钮,置实验平台为运行状态。

● 按脉冲单元中的PLS1脉冲按键,在RACK上产生一个上升沿,使通用寄存器中的值右移。

● 此时数据总线上的LED指示灯IDB0~IDB7 应该显示为21H。由于通用寄存器内容不为0,所以ZD(LED)灯灭。

● 按脉冲单元中的PLS1脉冲按键,使通用寄存器中的值右移,此时数据总线上的LED指示灯IDB0~IDB7应该显示为90H。若一直按PLS1,在总线上将看见数据循环左移的现象。

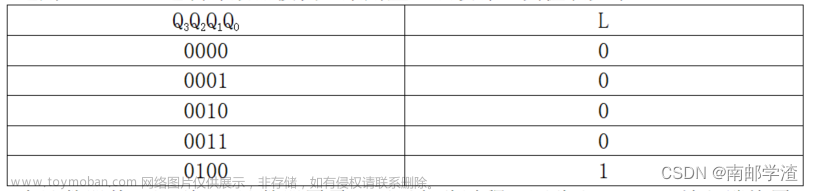

附:通用寄存器的逻辑

通用寄存器(8位并入并出移位寄存器)

| CLR |

X1 X0 |

CLK |

SL SR |

QA~AH |

| 0 |

X X |

X |

X X |

全 0 |

| 1 |

X X |

0 |

X X |

保持不变 |

| 1 |

1 1 |

上升沿 |

X X |

并行接数A~H |

| 1 |

0 1 |

上升沿 |

X 0 |

右移 移入0 |

| 1 |

0 1 |

上升沿 |

X 1 |

右移 移入1 |

| 1 |

1 0 |

上升沿 |

0 X |

左移 移入0 |

| 1 |

1 0 |

上升沿 |

1 X |

左移 移入1 |

🍀四、 实验步骤

实验1 数据输入通用寄存器

(1)step1:把RA-IN、RA-OUT分别与二进制开关单元JO1和总线DJ6相连,并把DACK使用连接线接到脉冲单元的PLS1上,具体接线如表1。

表1

| 控制信号 |

接入开关位号 |

|

| RACK |

PLS1 |

孔 |

| X0 |

H12 |

孔 |

| X1 |

H11 |

孔 |

| ERA |

H10 |

孔 |

| RA-0 |

H9 |

孔 |

| M |

H4 |

孔 |

(2)step2:二进制开关H16至H23作为数据输入,置42H(对应开关如表2)。

表2

| H23 |

H22 |

H21 |

H20 |

H19 |

H18 |

H17 |

H16 |

数据总线值 |

| D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

8位数据 |

| 0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

42H |

置各控制信号如表3.

表3

| H12 |

H11 |

H10 |

H9 |

H4 |

| X0 |

X1 |

ERA |

RA-0 |

M |

| 1 |

1 |

0 |

0 |

1 |

(3)step3:启动机箱的运行键,按下PLS1脉冲按键,在D1CK产生上升沿,把42H打入通过寄存器中,运算结果在数据总线上的指示灯IDB0-IDB7的LED显示灯应为42H,但由于通用寄存器不为0,所以LED(ZD)灯灭。

实验2 寄存器内容无进位位左移实验

(1)step1:在实验1基础上,置各信号如表4。

表4

| H12 |

H11 |

H10 |

H9 |

H4 |

| X0 |

X1 |

ERA |

RA-0 |

M |

| 0 |

1 |

0 |

0 |

1 |

(2)step2:启动机箱的运行键,按下PLS1脉冲按键,在D1CK产生上升沿,运算结果在数据总线上的指示灯IDB0-IDB7的LED显示灯应为84H,但由于通用寄存器不为0,所以LED(ZD)灯灭。

(3)step3:启动机箱的运行键,再次按下PLS1脉冲按键,运算结果在数据总线上的指示灯IDB0-IDB7的LED显示灯应为09H,若一直按PLS1,可发现数据循环左移现象(通过灯的变化判断)。

实验3 寄存器内容无进位位右移实验

(1)step1:在实验1基础上,置各信号如表5。

表5

| H12 |

H11 |

H10 |

H9 |

H4 |

| X0 |

X1 |

ERA |

RA-0 |

M |

| 1 |

0 |

0 |

0 |

1 |

(2)step2:启动机箱的运行键,按下PLS1脉冲按键,在D1CK产生上升沿,运算结果在数据总线上的指示灯IDB0-IDB7的LED显示灯应为21H,但由于通用寄存器不为0,所以LED(ZD)灯灭。

(3)step3:启动机箱的运行键,再次按下PLS1脉冲按键,运算结果在数据总线上的指示灯IDB0-IDB7的LED显示灯应为90H,若一直按PLS1,可发现数据循环右移现象(通过灯的变化判断)。

🌿五、 实验结果

实验1 数据输入通用寄存器

实验2 寄存器内容无进位位左移实验

实验3 寄存器内容无进位位右移实验

🌷六、 实验体会

- 通过使用通用寄存器实现置42H,完成数据左移和右移功能,我明白了通用寄存器的硬件工作原理,以及通用寄存器的组成。

- 通过完成不带进位移位实验,最初在机箱实验并未发现数据总线的灯的变化,其中灯始终全亮但在IDB0-IDB7的LED显示灯变化正确,在按下停止按钮并重新运行时,可发现数据总线灯的变化,原因在于设备反应可能因为年代原因较为迟钝。

- 对于实验三,在键入42H后(即第一次实验基础上)设置信号如表5,按下PLS1按键后并未由42H变为21H而是84H,连续三遍实验结果一致,但在其他机箱操作显示正确,所以正确的机箱设备也是实验成功的重要因素。

📝总结

计算机组成原理领域就像一片广袤而未被完全探索的技术海洋,邀请你勇敢踏足数字世界和计算机组成原理的神秘领域。这是一场结合创造力和技术挑战的学习之旅,从基础概念到硬件实现,逐步揭示更深层次的计算机结构、指令集架构和系统设计的奥秘。渴望挑战计算机组成原理的学习路径和掌握计算机硬件的技能?不妨点击下方链接,一同探讨更多数字技术的奇迹吧。我们推出了引领趋势的💻 计算机组成原理专栏:《机组 | 模块单元实验》,旨在深度探索计算机系统技术的实际应用和创新。🌐💡

文章来源:https://www.toymoban.com/news/detail-801484.html

文章来源:https://www.toymoban.com/news/detail-801484.html

文章来源地址https://www.toymoban.com/news/detail-801484.html

文章来源地址https://www.toymoban.com/news/detail-801484.html

到了这里,关于【机组】通用寄存器单元实验的解密与实战的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!