本设计实现AES加密算法为ecb模式,填充模式未设置,同时支持AES-128/192/256三种密钥长度。代码完全开源,开源链接在文章末尾。

1.文件架构

下图为GitHub仓库中上传的文件第一级结构,第一级为matlab和user,matlab中存储的是在进行列混淆运算时查表所用的coe文件,这些文件用来初始化vivado中的bram IP以便于查表运算。

user

ip:存放使用到的Xilinx ip文件;

src:存放算法设计的Verilog文件;

sim:存放仿真文件。matlab

gen_coe.m:用于产生对应的coe文件

*.coe:用于初始化IP。

2.代码说明以及仿真结果

2.1 代码结构

为了方便进行上板验证,在设计时我使用串口进行了代码的封装,因此顶层文件top中添加了串口以及串口协议解析的部分代码,这些代码是和aes算法本身没有关系的,所以可以直接忽略。aes算法的核心应该是aes_core以及它的子文件。

top

key_filter:按键滤波接入外部控制信号(与aes算法无关,建议忽略);

uart_aes_packed:次顶层,该部分将aes代码和串口解析代码以及串口接口封装到了一起(与aes算法无关,建议忽略);串口解析部分:这部分代码没有封装成子模块,直接在uart_aes_packed文件中编写,这个部分的任务主要是将接收到的串口数据解析为密钥或者明文,比如我设定首先连续接收到“key”字符表示数据为密钥,然后下一个字符为“a/b/c”分别来指代当前的密钥长度为128/192/256bit三种模式。

uart_tx/rx:串口接收发送模块;

aes_core:aes算法顶层代码。该部分代码为实现重点。aes_key_expasion:密钥拓展模块,实现同时支持AES128/192/256三种密钥长度的密钥拓展。

aes_sbox:实现同时支持4byte的S盒替换。

aes_encipher:加密模块,实现分别支持三种密钥长度的aes加密;

aes_sbox_128:实现同时支持16byte的S盒替换;

aes_col_mux:实现列混淆计算;

轮密钥加和行移位较为简单,直接在代码中实现未单独写为v文件。aes_decipher:解密模块,实现分别支持三种密钥长度的aes解密。

aes_inv_sbox_128:实现同时支持16byte的逆S盒替换;

aes_inv_col_mix:实现逆列混淆计算。

2.2 代码仿真结果

2.2.1 密钥拓展模块仿真

AES-128密钥拓展结果(与(二)中c++结果对比)

AES-128密钥拓展结果(与(二)中c++结果对比)

AES-192密钥拓展结果(与(二)中c++结果对比)

AES-192密钥拓展结果(与(二)中c++结果对比)

AES-256密钥拓展结果(与(二)中c++结果对比)

AES-256密钥拓展结果(与(二)中c++结果对比)

2.2.2 加密模块仿真

AES-128加密结果(与(二)中c++结果对比)

AES-128加密结果(与(二)中c++结果对比)

AES-192加密结果(与(二)中c++结果对比)

AES-192加密结果(与(二)中c++结果对比)

AES-256加密结果(与(二)中c++结果对比)

AES-256加密结果(与(二)中c++结果对比)

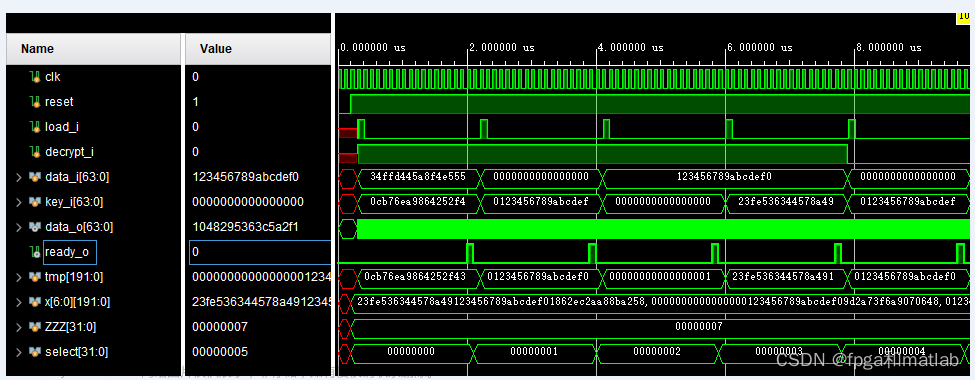

2.2.3 解密模块仿真

与输入明文相同,解密成功。

与输入明文相同,解密成功。

2.2.4 整体结果仿真(包含串口解析以及串口收发部分)

这部分仿真了串口接入密钥以及明文数据后的结果,但是使用串口只是为了方便上实物,我认为如果没有上实物需求可以完全忽略这部分,而且应该有更好的上板验证方法。

这部分仿真了串口接入密钥以及明文数据后的结果,但是使用串口只是为了方便上实物,我认为如果没有上实物需求可以完全忽略这部分,而且应该有更好的上板验证方法。

2.3 上板验证结果

开发板板连接

开发板板连接 串口发送的密钥流

串口发送的密钥流

串口发送的明文流

串口发送的明文流

接收到的密文和仿真结果密文对比

接收到的密文和仿真结果密文对比

接收到的解密结果

接收到的解密结果

2.4 资源消耗

aes_core的资源消耗(在vivado 2023.2平台下,器件为zynq7020的情况下的综合结果)

aes_core的资源消耗(在vivado 2023.2平台下,器件为zynq7020的情况下的综合结果)

2.5 接口说明

密钥拓展模块

module aes_key_expasion

(

input wire clk ,

input wire rst ,

input wire [ 255:0] key_in ,//*按有可能输入的最大值来输入(256bit)

input wire [ 1:0] keylen ,//*0 1 2

input wire init ,//*indicate the initial key is ready

input wire [ 3:0] round ,//*indicate the current round

output wire [ 127:0] round_key ,//*output the round key

output wire key_ready ,//密钥拓展完成信号

output wire [ 3:0] round_num //表明当前的加密模式总共有多少轮

);

加密模块

module aes_encipher (

input wire clk,

input wire rst,

input wire next,//开始工作信号,表明明文准备完毕

input wire [3:0] round_num,//需要加密的轮数,表示不同的密钥长度

input wire key_ready,//密钥准备完成信号

input wire [127:0] round_key,//轮密钥

output reg [3:0] round,//当前轮

input wire [127:0] plain,//输入明文

output reg [127:0] cipher,//输出密文

output reg cipher_ready,//加密完成标志

output wire error //*密钥未生成,收到了加密信号

);

解密模块文章来源:https://www.toymoban.com/news/detail-801693.html

与加密模块基本相同

https://github.com/MaxWei250/aes_fpga 代码地址

如有帮助希望可以star💕文章来源地址https://www.toymoban.com/news/detail-801693.html

到了这里,关于AES算法基于FPGA的硬件实现(3)AES算法的Verilog实现(完结)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!