⭐️作者简介:

小瑞同学,一个努力精进的FPGA和通信学习者。

🍎个人主页:小瑞同学的博客主页

🌻个人信条:越努力,越幸运!

⏰日期:2023.12.6

🔍来源:自学经历

📖文章内容概述:简单介绍了FIFO IP核常用参数的配置,通过仿真分析了异步IP的读写数据过程。

连载系列:FPGA中FIFO的应用

完整工程已上传至CSDN:下载链接

- 同步FIFO设计

- 异步FIFO设计

- Vivado FIFO IP核的调用

1.FIFO IP核参数配置简介

参考文档:pg057 P156—P173

1.1 Basic

①选择FIFO的接口类型:

- 传统接口

- AXI存储映射接口

- AXI Stream接口。

②FIFO的实现方式:这个种类有很多,这里不详细列出。

- common clock表示同步FIFO

- independent clock表示异步FIFO

1.2 Native Ports

在Basic界面选择传统接口后,其配置界面如下:

①读类型:

- 标准FIFO

- 首字掉入FIFO,

②数据端口参数:设置读写宽度和深度,

补充:

- 一般我们选择标准FIFO即可,有关首字掉入FIFO的说明详见P99。

- 虽然读写位宽可以设置为不同,但读深度不可设置,而是会根据上边三个参数自行计算出来,一般要满足:写宽度 * 写深度=读宽度 * 读深度。

- 写深度我们设置的使256,但IP核所实现的实际深度却是255,也就是比设置深度少1。

1.3 Status Flags

①可选标志:

- 将满标志

- 将空标志

补充:

- almost_empty和almost_full可看作是empty和full的警告信号,它们相对于empty和full会提前一个时钟周期拉高。

1.4 Data Counts

①数据计数器:用来记录读写数据的个数,可分别设置读写数据计数器的位宽。

2.仿真验证

2.1 testbench文件

`timescale 1ns / 1ps

module tb();

parameter FIFO_WIDTH=8;

reg wr_clk;

reg rd_clk;

reg [7:0] din;

reg wr_en;

reg rd_en;

wire [7:0] dout;

wire full;

wire almost_full;

wire empty;

wire almost_empty;

wire [7:0] rd_data_count;

wire [7:0] wr_data_count;

initial begin

wr_clk=1'b0;

rd_clk=1'b0;

din='b0;

wr_en=1'b0;

rd_en=1'b0;

#10;

repeat(10)begin

@(negedge wr_clk)begin

din={$random}%(2^FIFO_WIDTH);

wr_en=1'b1;

end

end

repeat(10)begin

@(negedge rd_clk)begin

rd_en=1'b1;

din={$random}%(2^FIFO_WIDTH);

end

end

end

always #10 wr_clk=~wr_clk;

always #20 rd_clk=~rd_clk;

fifo_generator_0 fifo_generator_u (

.wr_clk(wr_clk), // input wire wr_clk

.rd_clk(rd_clk), // input wire rd_clk

.din(din), // input wire [7 : 0] din

.wr_en(wr_en), // input wire wr_en

.rd_en(rd_en), // input wire rd_en

.dout(dout), // output wire [7 : 0] dout

.full(full), // output wire full

.almost_full(almost_full), // output wire almost_full

.empty(empty), // output wire empty

.almost_empty(almost_empty), // output wire almost_empty

.rd_data_count(rd_data_count), // output wire [7 : 0] rd_data_count

.wr_data_count(wr_data_count) // output wire [7 : 0] wr_data_count

);

endmodule

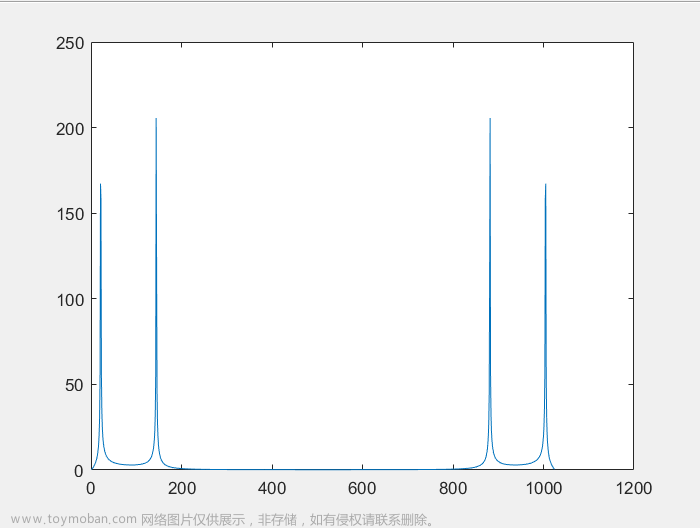

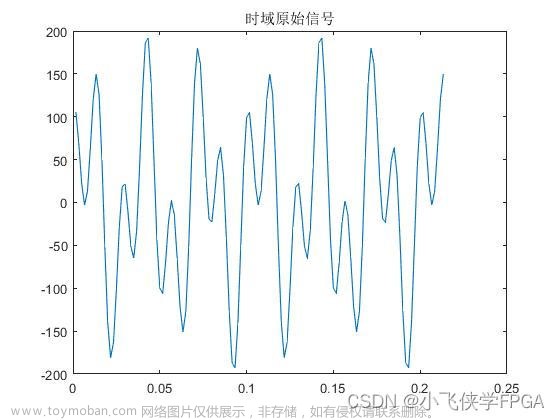

2.2 原始仿真结果

☀️IP核配置即为上述各图中所示,结果如下:

2.3 修改参数后的仿真结果

☀️为了验证异步FIFO作不同数据宽度的数据接口这一应用,这里我们简单修改一下,使读位宽大于写位宽,设置读位宽为16位,读深度则为128。可以看到一个读出数据对应两个写入数据,也就是说,当读位宽大于写位宽时,几个写入数据拼接成一个读出数据。

☀️然后再试试写位宽大于读位宽的情况,这里设置读位宽为4,则读深度为512,并将输入数据扩大2倍。可以看到每次先读出输入数据的高4位,再读出低4位,也就是说,几个读出数据对应一个写入数据。

文章来源:https://www.toymoban.com/news/detail-801905.html

文章来源:https://www.toymoban.com/news/detail-801905.html

❤️如果觉得文章对你有所帮助的话,别忘了点个收藏和赞哦~

❤️更多优质内容可浏览本人主页👇,期待再次与你相遇!

🎉🎉🎉🎉🎉🎉小瑞同学的博客主页🎉🎉🎉🎉🎉🎉文章来源地址https://www.toymoban.com/news/detail-801905.html

到了这里,关于FPGA中FIFO的应用(三)——Vivado FIFO IP核的调用的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!