-

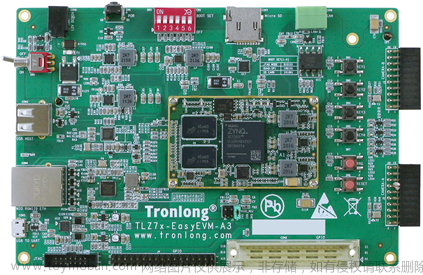

设置拨码开关为JTAG方式

-

烧写LED bit stream

a. 点击“Program device”烧录程序到FPGA中(重新上电程序就丢失了)

b.

/01_led/led.runs/impl_1/led.bit 文章来源:https://www.toymoban.com/news/detail-801976.html

文章来源:https://www.toymoban.com/news/detail-801976.html -

程序烧录到Flash中

ZYNQ与以往的直接烧录Flash不同,首先必须PS,然后烧录PL,参考这个实例。 文章来源地址https://www.toymoban.com/news/detail-801976.html

文章来源地址https://www.toymoban.com/news/detail-801976.html

到了这里,关于Alinx ZYNQ 7020 LED调试--in RAM的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[ZYNQ]开发之MATALB与FPGA联合仿真平台设计](https://imgs.yssmx.com/Uploads/2024/02/765704-1.png)

![FPGA:调试报错Error:add_1 must be in range [-1,DEPTH-1]解决办法和调试思路](https://imgs.yssmx.com/Uploads/2024/02/618133-1.png)