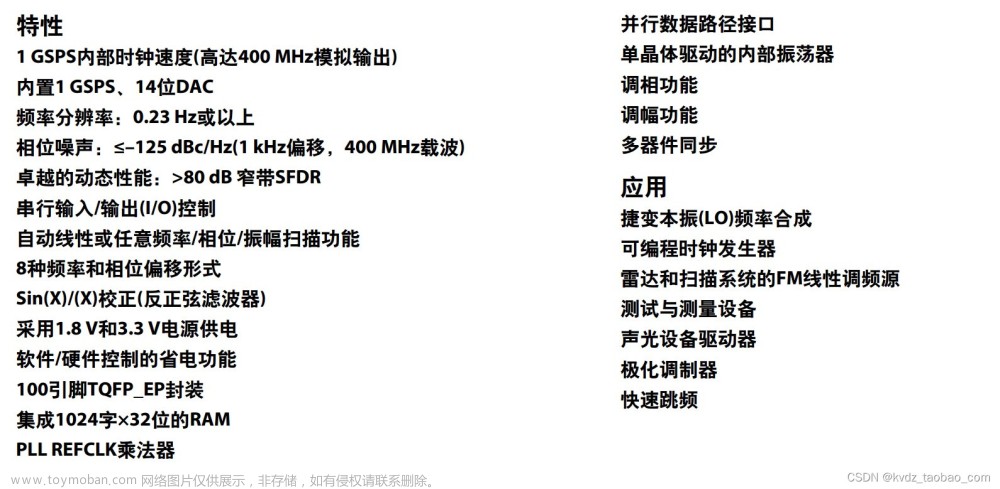

引言:上一篇文章我们简单介绍了AD9129的基础知识,包括芯片的重要特性,外部接口相关的信号特性等。本篇我们重点介绍下项目中FPGA与AD9129互联的原理图设计,包括LVDS IO接口设计、时钟电路以、供电设计以及PCB设计。

-

LVDS数据接口设计

当AD9129作为FPGA外设进行互联设计时,需要考虑AD9129芯片IO接口电平,DAC芯片与K7芯片互联的IO Bank。AD9129与FPGA互联接口特性如下表所示。

表1 AD9129接口特性

根据FPGA其他外设整体布局规划,DAC分配至FPGA Bank12和Bank13上,如下图所示。

图1:FPGA IO Bank规划

由于Bank12和Bank13为HR IO Bank,FPGA LVDS接口电平标准为LVDS_25,特性如下图所示,因此这两个Bank VCCO采用2.5V供电。

表2 LVDS_25 DC特性

DAC LVDS数据及控制接口设计如下图所示。

图2:FPGA与AD9129 LVDS IO分配电路

图3:AD9129外围电路设计

另外,考虑到DAC控制接口电平为LVCMOS18电平标准,当DAC控制接口与FPGA 2.5V VCCO IO互联时,需要使用电平转换芯片,以满足IO Bank电气兼容要求。详细原理图设计如下图。

FPGA IO Bank供电

图4: DAC SPI电平转换电路

2.时钟电路设计

手册推荐的典型时钟供电电路如下图所示。

图5:AD9129典型时钟电路

DACCLK_x输入的峰峰值电压为0.25~2V,典型值为1V,共模电压为1.25V。DACCLK_x输入时钟频率范围为1.4G~2.85GHz。

本设计选用ADI ADF4355为AD9129提供时钟,原理图如下图。

图6:时钟电路设计

3.电源设计

AD9129电源分为模拟电源和数字电源,整个芯片最大功耗在1.1W左右,最大功耗工作时,需要考虑芯片散热问题。

模拟电源VSSA=-1.5V,Imax=54mA;

模拟电源VDDA=1.8V,Imax=230mA;

数字电源VDD=1.8V,Imax=336mA。

图7:AD9129供电电路

图8:AD9129滤波电路

4. AD9129 PCB设计

电路板采用12层PCB设计,层叠设计如下图所示。

图9:PCB层叠设计

AD9129电路设计完成的PCB版图如下图所示。

图10:AD9129 PCB设计(图中绿色范围内)

5. 小结

本篇我们重点介绍了FPGA与AD9129互联的原理图设计,包括LVDS IO接口设计、时钟电路以、供电设计以及PCB设计。下一篇再对AD9129接口SPI接。

文章来源:https://www.toymoban.com/news/detail-802171.html

文章来源:https://www.toymoban.com/news/detail-802171.html

延伸阅读:基于Xilinx K7-410T的高速DAC之AD9129开发笔记(一)文章来源地址https://www.toymoban.com/news/detail-802171.html

到了这里,关于基于Xilinx K7-410T的高速DAC之AD9129开发笔记(二)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!