0x00 优先级编码器(Priority encoder)

"能将多个二进制输入压缩成更少数目输出的电路或算法的编码器"

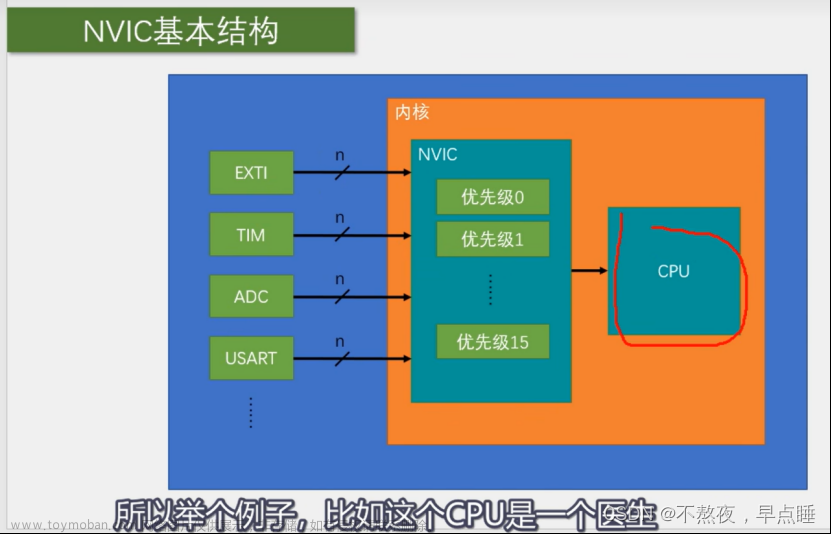

优先级编码器是一种编码器,它考虑了两个或更多输入位同时变为 1 但没有收到输入的情况。当输入进来时,优先级编码器会按照优先级顺序进行处理。

通常,它按升序或降序排列输入的优先级,当没有输入时,它会向 输出一个 1,以区分零输入和零输出。在下面的真值表中,输入值的优先级顺序如下:文章来源:https://www.toymoban.com/news/detail-802504.html

| 优先级编码器文章来源地址https://www.toymoban.com/news/detail-802504.html |

到了这里,关于【FPGA】Verilog 实践:优先级编码器 | Priority encoder的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![c语言[]优先级大于*优先级](https://imgs.yssmx.com/Uploads/2024/01/808419-1.png)