1.M:几个模拟通道就为几

2.N:ADC和DAC中量化位数:16bit——N=16.

3.N':以半字节及4bit为单位:16bit——N'=4,14bit——N'=4(多余的2bit以CS控制位和T结束位占位)

4:F:每一帧的字节数:2byte——2(一般在器件手册上以OCTET标识)

5:K:多帧包含的帧数:32——32(器件手册一般这样定义Ceil (17 / Number of Octetsper Frame) ≤ Multiframe Size (In Terms of Number of Frames),即Ceil (17 / 6) ≤ K。因此K必须要大于等于3,小青菜哥哥决定K取4。)

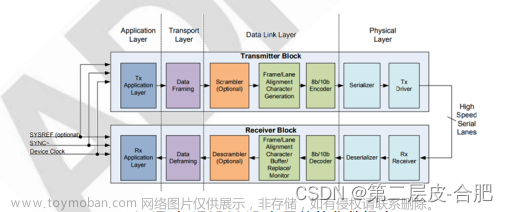

6:当FPGA做TX使用时——JESD204B IP核或者也可以配合JESD204b phy使用。

7:当FPGA做RX使用时——单独使用JESD204B IP核。

11.JESD204B的参考时钟tx_core_clk=单条lane的线速度(ip核设置的,一般是器件支持的最大速度)/40 用户决定IP核的core clk是否由glbclk(p/n)管脚输入。当refclk(p/n)频率不等于core clk时,必须外部输入core clk。本篇中的线速率为4.8Gbps,因此core clk为120MHz,所以本人将参考时钟输入频率也调成120MHz,这样IP核只需要一个120MHzd的参考时钟输入接口了。

对于7系列器件,如果IP核的模式为“Include Shared Logic inexample design”,则频率范围为10MHz~200MHz

如果IP核的模式为“Include Shared Logic incore”,则频率范围和Transceiver DRP时钟频率范围相同

13.DRP Clock Frequency:配置页面已经提到过,对于七系列器件,DRP clk和AXI4-Lite clock为同一时钟,所以这里也不可选了,只能为前面定下的80MHz。

14.数据从时钟中恢复(CDR技术,Clock Data Recovery)

15.

Clock Data Recovery时钟恢复电路一般是通过PLL电路(鉴相器PD、环路滤波器LF、压控振荡器VCO)实现,其作用是从数据流中准确的恢复出时钟和数据信息。

参考时钟输入到鉴相器(PD),鉴相器比较的是两个相位,一个是参考时钟,一个是数据恢复时钟,两个时钟之间存在两种差异,一种是频率差,另一种是相位差,当恢复时钟相位与参考时钟相位之间存在差异的话会产生一个对应比例的积分值,根据积分值的大小,控制数据时钟提取电路的时钟进行偏移,从而使得数据恢复时钟和参考时钟相位进行对齐,此时认为输出时钟锁定,即所向为认为时钟已经锁定到了所需要的相位或者频点上,就可以作为一个可以使用的时钟。

16.Comma码(K码)

以K28.5为例:

28表示8位数据的后五位为27,即5’b1_1100

5表示的8位数据的前三位为5,即3’b101

故K28.5的二进制形式为:8’b1011_1100,即8’hBC

S(samples)

S表示每一个转换器每一侦中的采样次数。一般情况下,S都是1。 S必须是整数。协议中允许S大于1,但是S等于1的时候可以保证侦时钟和采样时钟相等。比如S=1,则一个500MSPS的转换器,侦时钟也为500M

20.LVDS接口的DAC和204B接口的DAC数据(给DAC芯片)区别在于:

(LVDS接口)rom表出64bit数据/时钟芯片进FPGA时钟——通过oserdes原语将64bit分成4组16bit的然后通过oserdes并转串通过LVDS接口发送给DAC芯片。

,(204B接口)rom表(该表的ceo文件来自于DDS产生的数字信号(DDS ip核的输入时钟(即数据速率),DDS最终产生的波形时钟))——ESD204B IP(input tx_tdata)——JESD204b phy(output txp/n out)出去。通过204B接口发送给DAC芯片

17.子卡工程备注是1.875M——为啥?——此处就是多帧时钟,奇哥一分为二的信号

| tx_sysref |

输入 |

JESD204B协议的SYSREF信号,作为确定性延迟的参考信号 |

18. jesd 204b的IP核输入的数据(tx_tdata)是64bit位宽——来源子卡DAC

19.jesd 204b的IP核输出(tx_tready)——代表输入 jesd 204b的IP的64bit数据有效

20.以GSM019 (12GHZ_DAC来说):RX需要向TX输入syncout同步信号,根据参考工程一直连接至JESD204IP的tx_sync(途中经过IBUFDES)

21.jesd204 IP核的AXI4-Lite配置时钟:默认为100MHz。与JESD204b phy中的DPR时钟一样。

22.线速率的计算:N’*4*采样频率*(10/0.8)——总的线速率/lane的条数——每条lane的线速率

23.JESD204B ip核Reference Clock=每条lane的线速率/40(eg:120MHZ)

背景:ADS54j60(ADC)/JESD204 IP核——shared logic in example design/JESD204 PHY IP核——shared logic in the core

JESD204 IP核

.rx_core_clk(rx_core_clk), //input wire rx_core_clk逻辑输入时钟,频率为单条线速度的1/40

.rx_reset(rx_reset), // input wire rx_reset 来源于外部逻辑

.rx_reset_gt(reset_gt), // output wire rx_reset_gt 输出到Jesd204_PHY的复位信号

.rx_reset_done(rx_reset_done), // input wire rx_reset_done Jesd204_PHY已复位完成标志信号

.rx_aresetn(rx_aresetn), // output wire rx_aresetn AXI4-Stream 复位,低有效,和发送数据逻辑相关。文章来源:https://www.toymoban.com/news/detail-803678.html

.s_axi_aclk(100hmz), // input wire s_axi_aclk AXI4-Lite时钟,源于JESD204 IP核的 100hmz 配置由逻辑产生

.s_axi_aresetn(~rx_reset), // input wire s_axi_aresetn AXI4-Lite控制逻辑复位,与rx_reset相关。

JESD204 PHY IP核

.tx_core_clk(tx_core_clk), //input wire tx_core_clk逻辑输入时钟,频率为单条线速度的1/40

.rx_core_clk(rx_core_clk), //input wire rx_core_clk逻辑输入时钟,频率为单条线速度的1/40

.tx_sys_reset(rx_reset), // input wire tx_sys_reset 来源于外部逻辑

.rx_sys_reset(rx_reset), // input wire rx_sys_reset 来源于外部逻辑

.tx_reset_gt(reset_gt), // input wire tx_reset_gt 来源于JESD204 IP核

.rx_reset_gt(reset_gt), // input wire rx_reset_gt 来源于JESD204 IP核

.rx_reset_done(rx_reset_done), // output wire rx_reset_done 输出到Jesd204 IP核的复位完成标志信号

//逻辑模块

. tx_core_clk(tx_core_clk) //output tx_core_clk来源于BUFG——IBUFDES_GET2——高速bank的参考时钟输入

.rx_reset(rx_reset) //output rx_reset

.s_axi_aclk(100hmz), //output 100hmz文章来源地址https://www.toymoban.com/news/detail-803678.html

到了这里,关于JESD204B知识点的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!