系列文章目录

分享一些fpga内使用riscv软核的经验,共大家参考。后续内容比较多,会做成一个系列。

本系列会覆盖以下FPGA厂商

- 易灵思 efinix

- 赛灵思 xilinx

-

阿尔特拉 Altera

本文内容隶属于【易灵思efinix】系列。

【risc-v】易灵思efinix FPGA sapphire_soc IP配置参数分享-CSDN博客

【risc-v】易灵思efinix FPGA riscv 时钟配置的一些总结-CSDN博客

目录

系列文章目录

前言

源码文件夹的生成

文件说明

【BSP】

【config】和【config_linux】

【software】

延伸

前言

在efinix fpga中使用riscv是一件相对容易的事,efinix官方提供了一套集成riscv核心的应用IP,在IP catalog中可以很方便的生成、修改。裁剪IP的功能。

上一节我们在efinity IP catalog中选择生成了 riscv IP,在【Deliverables】页可见默认勾选了【embedded_sw】。

本章节就产生的【embedded_sw】进行文件说明。

源码文件夹的生成

IP核生成的同时,会在FPGA工程根目录生成【embedded_sw】文件夹

/embedded_sw/

这个文件夹是 嵌入式软件工程源码文件夹。

我选择是riscv ip是sapphire,因此自动产生【sapphire_soc】文件夹,展开这个文件夹有如下文件夹

文件说明

•nbsp--板级支持包。

•config--适用于Windows系统的Eclipse项目设置文件和OpenOCD调试配置设置文件。

•config_linux--适用于linux系统的Eclipse项目设置文件和OpenOCD调试配置设置文件。

•software——软件示例。

•tool--帮助脚本。

•cpu0.yaml---用于调试的CPU文件。

【BSP】

板级支持包(BSP)定义了地址映射,并与Sapphire SoC硬件地址映射对齐。BSP文件位于nbsp/efinix/EfxSapphireSoC子目录中。

| 文件或目录 |

描述 |

| app |

示例软件和引导加载程序使用的文件。 |

| include\soc.mk |

支持的指令集 |

| include\soc.h |

定义系统频率和地址映射 |

| linker\default.ld |

主内存地址和大小的链接器脚本。 |

| linker\bootloader.ld |

引导加载程序地址和大小的链接器脚本。 |

| openocd |

OpenOCD配置文件。 |

【config】和【config_linux】

Efinix在【config】和【config_linux】文件夹提供了一个C/C++项目设置文件,该文件定义了C代码的包含路径和符号。将这些设置导入到项目中可以让您轻松地浏览和跳过代码。

要导入设置,请执行以下操作:

1。选择“文件”>“导入”打开“导入”向导。

2.展开C/C++。

3.选择“C/C++”>“C/C++项目设置”。

4.单击“下一步”。

5.单击“设置”文件框旁边的“浏览”。

6.转到以下目录,然后单击“打开”:

7。在“选择项目”框中,选择要为其导入设置的项目名称。

8.单击“完成”。

Eclipse在项目中创建一个名为Includes的新文件夹,其中包含项目使用的所有文件。导入设置后,请清理项目(Project > Clean),然后生成(Project> Build Project

)。生成过程对所有文件进行索引,以便将它们链接到项目中。

【software】

Efinix提供了各种示例软件代码,用于执行诸如通过UART通信、控制GPIO中断、执行Dhrystone基准测试等功能。每个示例都包括一个makefile和包含源代码的src目录。

这部分内容很多,下一章节继续。

延伸

---关于易灵思

易灵思是一家国产FPGA公司,采用逻辑和路由可以互换的XLR结构,发明了突破性的Quantum架构,PPA优势是传统世界领先FPGA公司的4倍。公司从架构与IC设计、工艺制程、封装与测试、成本/品质/交付管控,到EDA工具设计、 IP与应用方案设计、营销与技术支持,均坚持质与量并行,力求问鼎行业桂冠。

---关于risc-v

RISC-V是一个开源的标准指令集架构(ISA,包含基本指令集和可选的扩展集),由非盈利的RISC-V基金会管理。由于RISC-V是免费的和开源的,它已经在世界范围内流行起来,目前有超过65个开源或商用的RISC-V内核。易灵思基于Charles Papon提出的VexRiscv核心创建了RISC-V SoC。

VexRiscv在2018年的RISC-V SoftCPU竞赛中获得第一名,是一个32位CPU,使用ISA RISCV32I具有M和C两种扩展模式,有五级流水(读取、解码、执行、内存和回写),以及一个可配置的特征集。SoC具有RISC-V处理器、内存、一系列I/O和用于嵌入用户功能的接口。您可以轻松地在同一个钛金系列或Trion®系列FPGA中创建包含嵌入式计算和用户定义加速器的完整系统。

---关于Sapphire SoC

- VexRiscv处理器,具有5级流水 (读取,解码,执行,内存,回写),中断和机器模式(Machine Mode)的异常处理

- 20 - 400 MHz 系统时钟频率

- 4 - 512 KB 带SPI flash引导加载程序的片上RAM

- DDR或HyperRAM的内存控制器

- 内存支持4MB - 3.5 GB

- 用户可配置外部内存总线频率

- 1个半双工AXI3接口(最高256位),用于外部存储器通信

- 400 MHz DDR 时钟频率, 800 Mbps数据带宽

- 200 MHz HyperRAM 时钟频率, 400 Mbps数据带宽

- 多达2个AXI主通道用于用户逻辑

- 1 AXI从通道到用户逻辑

- 包含浮点运算单元

- 包含一个可选的Linux内存管理单元(MMU)

- 包含一个具有1024个ID的自定义指令接口,以执行不同的功能

- 支持可选的RISC-V扩展,例如atomic和compressed

- APB3 外设可支持

- 32个 GPIOs

- 3个 I2C masters

- PLIC

- 3个 SPI masters,最高时钟频率 25 MHz — 最多 3个 user timers

- 3个 UARTs,115,200 baud rate

- 5个 从外设

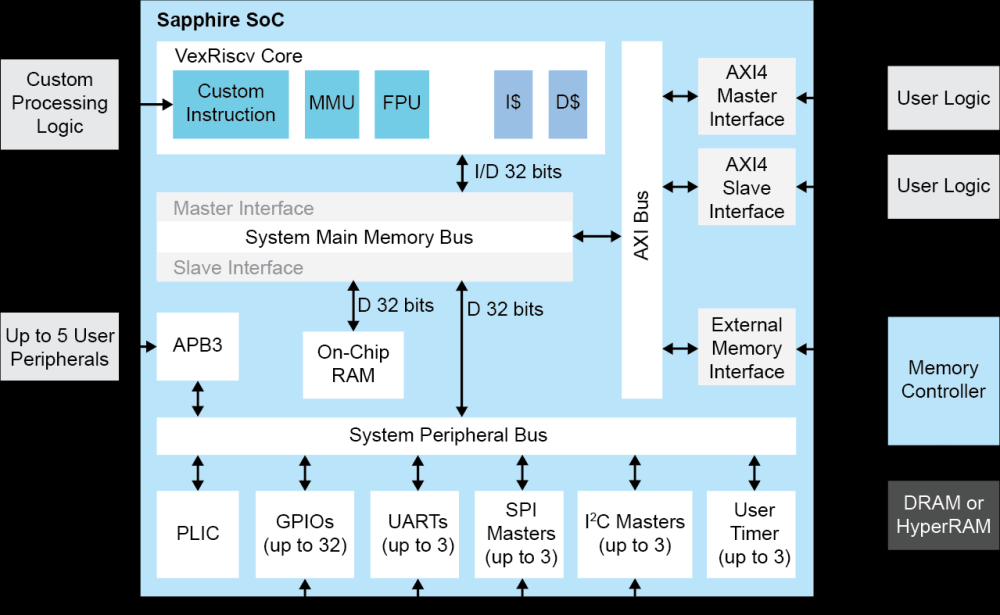

Sapphire SoC框图:

Sapphire SoC集成了一个32位RISC-V处理器,该处理器具有多达8路的指令缓存和可配置大小的1-32KB,多达8路的数据缓存和可配置大小的1-32KB,4-512KB的片上RAM,以及各种外设(包含1-5 APB3从站外设和1个AXl从站)。您可以在20-400MHZ范围内配置工作频率(实际性能受设计fMAX的限制)。SoC包括1-3个I2C外设、1-3个UART、1-3个用户定时器和1-3个SPI主器件。还具有浮点单元(FPU)、自定义指令接口和Linux内存管理单元 (MMU)

默认配置具有多达256位半双工AXl总线,可与Efinix DDR控制器或HyperRAM控制器进行通信。

- DDR控制器 - 该内核使用Trion FPGA硬DDR DRAM接口来复位外部DRAM模块(重置并重新初始化Trion FPGA的DDR接口以及DDR模块)

- 超 RAM 控制器 - 此内核控制超RAM内存模块 您可以使用 Efinity®软件中的IP管理器自定义SoC

参考资料:

产品中心 / RISC-V-易灵思

易灵思文章来源:https://www.toymoban.com/news/detail-804047.html

技术支持 / 公开文档-易灵思文章来源地址https://www.toymoban.com/news/detail-804047.html

到了这里,关于【risc-v】易灵思efinix FPGA riscv嵌入式软件源码分享的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!