硬件设计-TYPE-C电路设计

1.引脚说明

由于USB2.0的数据率最高只有480Mbps, 可以不考虑信号走线的阻抗连续性,USB2.0的D+/-信号可以不被MUX控制而直接从主控芯片走线,然后一分二连接至USB Type-C插座的两组D+/-管脚上。

但USB3.0或者USB3.1的数据率高达5Gbps或者10Gbps,如果信号线还是被简单地一分二的话,不连续的信号线阻抗将严重破坏数据传输质量,因此必须由MUX切换来保证信号路径阻抗的一致性,以确保信号传输质量。

- 检测 USB 端口的连接

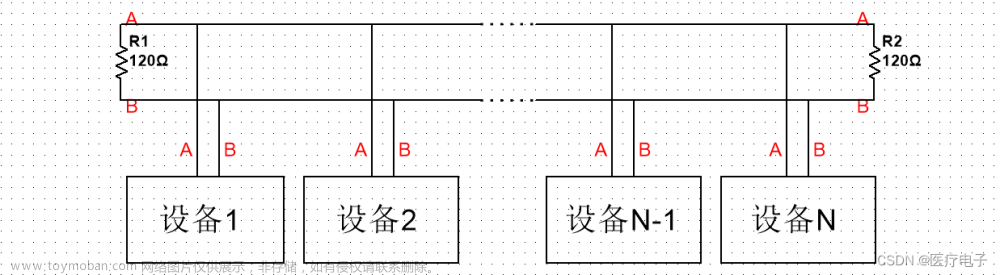

DFP为Host端,UFP 为device端。在DFP的CC pin会有上拉电阻Rp,在UFP会有下拉电阻Rd。在DFP与UFP未连接之前,DFP的VBUS是没有输出的。当DFP与UFP连接后,CC pin相接,DFP的CC pin 侦测到UFP pulldown Rd,表示接到Device,DFP便打开VBUS的FET开关,输出VBUS电源给UFP。

- 检测正反插

由于Type-C是支持正反插,CC pin被用来侦测正反插,从DFP的角度来看,当CC1接到Pulldown就是正插,如果是CC2接到Pulldown就是反插。在侦测完正反插后,就会输出相对应的USB信号,例如CC1对应的是SSTX1与SSRX1。下图的右边整合了MUX,由于USB 3.1的data rate高达10 Gbps,为了避免PCB的走线出现分支,所以正反插进来的信号会由MUX来切换,正插时:切换到SSRX1&SSTX1,反插时:切换到SSRX2&SSTX2

- PD充电检测

USB PD的功能还需要有USB PD Phy chip来完成Protocol沟通,而Protocol信号是载在两端连接的CC pin上。沟通方式是通过双相标记编码(BMC)编码。

- 数据线上的Ra

带电子标签的线缆,其中一个CC管脚被更名为VCONN,用于给电子标签芯片供电。这个VCONN管脚与GND之间需要一个Ra电阻,这个电阻值范围是800Ω~1.2KΩ。

如果其中一个CC引脚上检测到有效的Rp/Rd连接,则VCONN电源可以接到另一个对应的CC引脚。

如果其中一个CC引脚上检测到有效的Rp/Rd连接,先检查另一个CC引脚是否也有Rp/Ra连接,然后再提供VCONN。

先检测是否有Ra存在,如果有说明需要Vconn供电,此时再提供Vconn。检测过程不需要Vconn存在。

注意,每一个CC引脚内部都有一个开关,轮训CC和VCONN功能,下图是一个典型的连接方式:

- 手机都是DRP

现实中,我们的手机都是DRP,既能做DFP,又能做UFP,那么是如何切换呢?

DRP在待机模式下每50ms在DFP和UFP间切换一次。当切换至DFP时,CC管脚上必须有一个上拉至VBUS的电阻Rp或者输出一个电流源,当切换至UFP时,CC管脚上必须有一个下拉至GND的电阻Rd。此切换动作必须由CC Logic芯片来完成。当DFP检测到UFP插入之后才可以输出VBUS,当UFP拔出以后必须关闭VBUS。此动作必须由CC Logic芯片来完成。下面是一个CC逻辑芯片框图,CC上有一个开关,在不断切换功能。

- 模拟耳机

协议要求模拟耳机转接线上把两个CC引脚直接接到GND(必须小于Ra)。

2.设计架构

TYPE-C接口需要有两组USB3.0的发送和接收差分对。

TYPE-C接口可以通过MUX复用器芯片进行桥接,通过芯片检测CC1还是CC2

还可以有多路U3通道的情况下通过两路U3通道

全功能的TYPE-C不仅包含了U3通道,还包括了DP显示接口。中间通过MUX芯片进行识别与判断。

SUB线缆在使用DP接口是,化身为AUX_P/AUX_N差分引脚。

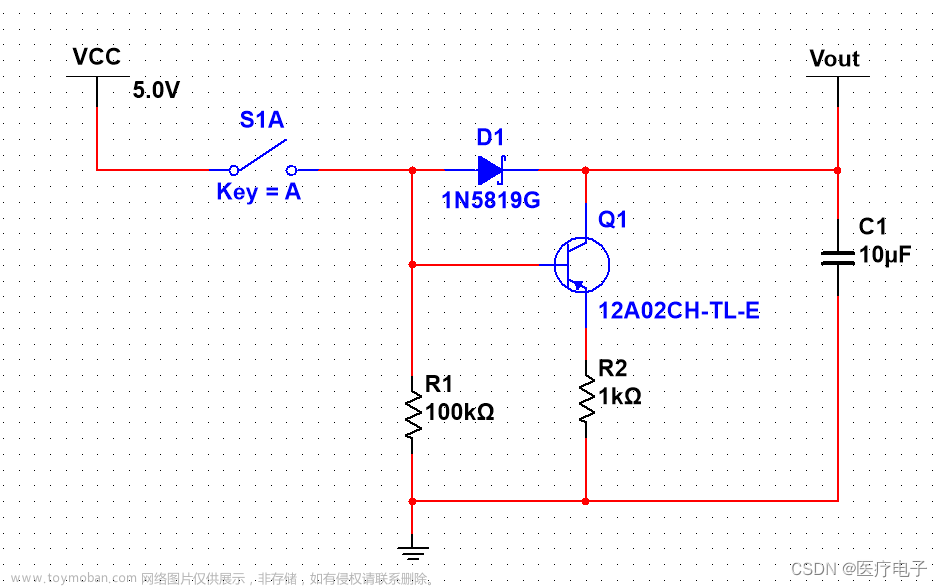

TYPE-C快充解决方案

CC检测方案 文章来源:https://www.toymoban.com/news/detail-804480.html

文章来源:https://www.toymoban.com/news/detail-804480.html

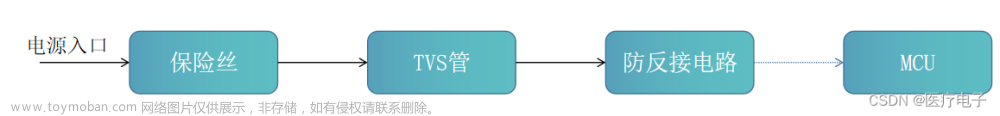

3.电路设计要点

文章来源地址https://www.toymoban.com/news/detail-804480.html

文章来源地址https://www.toymoban.com/news/detail-804480.html

- AC耦合电容放置在TX端

- 对外接口处的ESD芯片必须要有

- 机壳地与数字地隔离

- 注意P与N的线序不能接反

- CCI CC2的上下拉电阻

- 数据线上的滤波电感必不可少

- 差分90R走线,参考层完整,等长布线

- TX 信号对上的电容器应尽可能靠近 USB Type-C 连接器放置

- CC信号应作为单端走线布线,阻抗为50Ω。不要将 CC 信号作为差分对路由。CC信号很敏感,因此它们的布线应没有全板短截线。CC信号不得跨平面分裂,因为这会导致不可预测的返回路径电流,这可能会导致信号完整性问题以及EMI问题。

到了这里,关于27-硬件设计-TYPE-C电路设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!