情景

在代码中添加Mark_debug的方式进行debug时,综合完成后,又修改了代码或者xdc,重新综合后,再布局布线就会出现这个报错。

注:使用在图上标记和添加ila ip的方式基本上不会出现这个问题。

报错

Error:

[Chipscope 16-213] The debug port ‘dbg_hub/clk’ has 1 unconnected channels

Critical Warning:![[chipscope 16-213] the debug port 'dbg_hub/clk' has 1 unconnected channels (,error解决,fpga开发,Vivado,error](https://imgs.yssmx.com/Uploads/2024/01/804836-1.png)

前提是检查后确实没有xdc上的错误才尝试这种解决方法!!!

解决方法

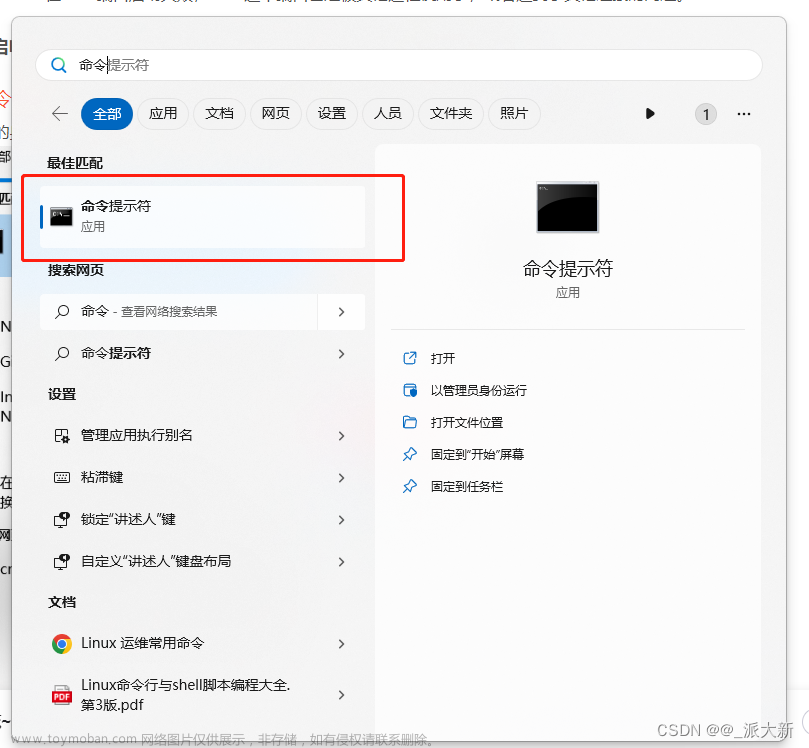

我尝试的方法步骤是:

- 修改了工程后,保存!

- 打开xdc文件,将xdc中自动生成的ila相关的代码删除,关闭xdc文件!

- 重新综合,综合完成

- 重新设置set up debug ,保存!

- 再综合,综合完成后打开综合结果!

- 布局布线

这样可以解决问题。

下面还有两种参考的方法:

-

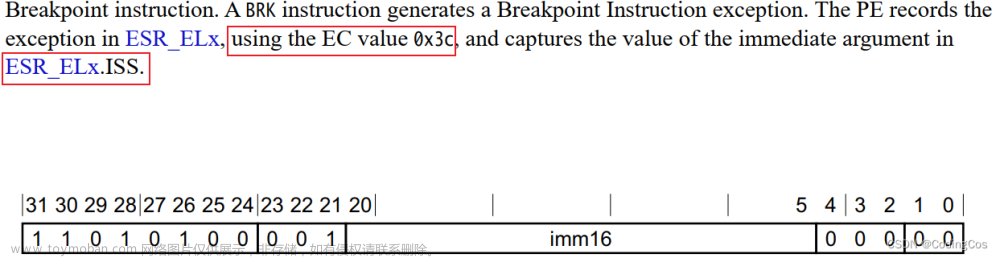

出现这种问题的原因是ILA更新了,但是约束没有自动更新,导致找不着dbg_hub的时钟,而这种时钟名是软件生成的,每次都不一样,可以在XDC文件中注释或删除掉dbg_hub的相约束。然后implement下打开IO,再然后取消一个IO的锁定并重新勾上之后按CTRL+S保存,这时会生成新的约束,如下图,然后重新编译工程吧文章来源:https://www.toymoban.com/news/detail-804836.html

-

加完debug后布线报错:[Chipscope 16-213] The debug port ‘dbg_hub/clk’ has 1 unconnected channels (bits). This will cause errors during implementation.

原因:综合之后没有选debug的设置,有的线还没有连时钟。给clk加debug好像有个buff报错解决不了,就把clk的debug删了。文章来源地址https://www.toymoban.com/news/detail-804836.html

到了这里,关于[Chipscope 16-213] The debug port ‘dbg_hub/clk‘ has 1 unconnected channels 解决的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!