前段时间,有时间整理了一下关于+vcs+initreg+random 编译和仿真选项的心得,草草写了两篇笔记。自觉得对该选项已经掌握了,后来实际应用中再次触及到了该知识点,不想又卡壳了。今天,继续追加一篇,希望对大家能有所帮助!不正之处,请指正。

对于上述规则rule#2和 rule#3, 并没有什么可值得推敲的地方。今天我们着重看第一点,rule#1。

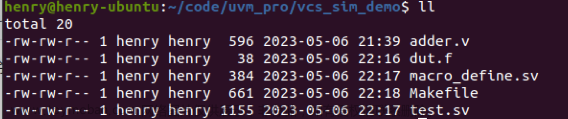

代码:

`timescale 1ps/1ps

module tb_top;

wire aa,bb,cc,dd;

reg clk;

reg rst_n;

wire [7:0] t_i, t_j, t_k, t_l_a, t_l_b, t_l_c;

wire [1:0] t_bit_a, t_bit_b;

wire [7:0] t_byte;

wire [63:0] t_time_value;

wire [127:0] t_r_time_value;

wire [3:0] data_out0;

wire [3:0] data_out1;

reg [3:0] data_in0;

reg [3:0] data_in1;

bit [1:0] bit_a, bit_b;

integer age, score;

int i, j, k;

byte addr;

real time_value;

realtime r_time_value;

logic [5:0] l_a, l_b, l_c;

assign cc = aa + bb ;

assign cc = aa+dd;

counter u_counter0(.clk(clk), .rst_n(rst_n), .data_out0(data_out0), .data_out1(data_out1), .data_in0(data_in0), .data_in1(data_in1));

assign t_i = i;

assign t_j = j;

assign t_k = k;

assign t_l_a = l_a;

assign t_l_b = l_b;

assign t_l_c = l_c;

assign t_bit_a = bit_a;

assign t_bit_b = bit_b;

assign t_byte = addr;

assign t_time_value = time_value;

assign t_r_time_value = r_time_value;

initial begin

clk=1'b0;

forever begin

#1 clk = ~clk;

end

end

initial begin

rst_n = 1'b1;

#15 rst_n = 1'b0;

#180 rst_n = 1'b1;

#200 $finish;

end

initial begin

//data_in0 = 0;

wait(!rst_n);

wait(rst_n);

@(posedge clk);

data_in0 = 1;

@(posedge clk);

data_in0 = 2;

@(posedge clk);

data_in0 = 4;

@(posedge clk);

data_in0 = 8;

@(posedge clk);

data_in0 = 0;

end

initial begin

//data_in1 = 0;

wait(!rst_n);

wait(rst_n);

@(posedge clk);

data_in1 = 1;

@(posedge clk);

data_in1 = 2;

@(posedge clk);

data_in1 = 4;

@(posedge clk);

data_in1 = 8;

@(posedge clk);

data_in1 = 0;

end

initial begin

$fsdbDumpfile("tb_top.fsdb");

$fsdbDumpvars(0,"tb_top");

end

endmodule

一 操作对象范围

变量类型支持:reg、bit、interger、int、logic、byte, 但是 real 、realtime 类型不可以。

二 操作应用场景

这里提到应用场景,这个很重要。只有知道应用的场景,才能更好的使用这个功能。我们知道,之所以出现该选项,VCS 厂商也不是一拍脑袋定下的,也是客户反馈的需求。

该选项,其实主要应用在后仿真过程中,因为前仿真的环境下,初始化没有赋值的寄存器等变量非常少,即便有个别,估计对仿真也没有致命程度。而后仿真条件下,就会存在大量的这样寄存器。因为后仿真netlist ,会出现大量没有初始化的寄存器存在,估计考虑面积等原因,会被后端同事处理掉。针对这种场景,该选项可以提供很大帮助。

但是前仿真我们不是不可以使用,但前提是寄存器变量没有被赋初始数值。如果关注的寄存器被赋予了初始数值,那么该选项不会起作用。

如上面的rst_n reg ,在initial begin...end 中被赋值1,那么即便我们采用+vcs+initreg+0, 也是毫无用处的。这一点很重要。

文章来源:https://www.toymoban.com/news/detail-808619.html

文章来源:https://www.toymoban.com/news/detail-808619.html

文章来源地址https://www.toymoban.com/news/detail-808619.html

文章来源地址https://www.toymoban.com/news/detail-808619.html

到了这里,关于#VCS# 关于VCS 编译选项:+vcs+initreg+random的理解(3)回头是岸的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[VCS、verdi、makefile] 联合仿真 ——步骤](https://imgs.yssmx.com/Uploads/2024/02/428958-1.png)