一、问题描述

在综合一个SOC时,发现综合后的门级网表文件缺少了apb系统下的子模块的网表。该SOC已经成功在FPGA上运行了,按理说在设计上是没有问题的。在反复查看综合报告与RTL设计源码后,终于解决了Bug。

二、问题所在

查看综合报告,发现以下警告和报错: 首先分析Warning,这个Warning的意思是,无法解析‘cmsdk_apb_subsystem’模块中引用的 'apb_wtd_interface’模块。

首先分析Warning,这个Warning的意思是,无法解析‘cmsdk_apb_subsystem’模块中引用的 'apb_wtd_interface’模块。

这里,apb_wtd_interface是看门狗模块的apb接口封装,导致该接口模块无法解析的原因是上一条的Error导致的,Width mismatch。这条Error是指PADDR信号的位宽不匹配。

由于信号位宽的不匹配导致dc无法解析该模块,从而导致综合后的门级网表缺少该模块的综合信息。

三、问题解决

找到位宽不匹配的信号。 i_addr位宽为16位,而该接口文件中的PADDR位宽为11位。

i_addr位宽为16位,而该接口文件中的PADDR位宽为11位。

只需将interface中的PADDR位宽改为[15:0]即可。

只需将interface中的PADDR位宽改为[15:0]即可。 其他出现的无法解析警告也按照同样的方法将位宽修改好。

其他出现的无法解析警告也按照同样的方法将位宽修改好。

再次运行dc,发现Error与Warning没有再出现,输出的门级网表中出现了这些模块的综合信息,且综合时间明显加长。

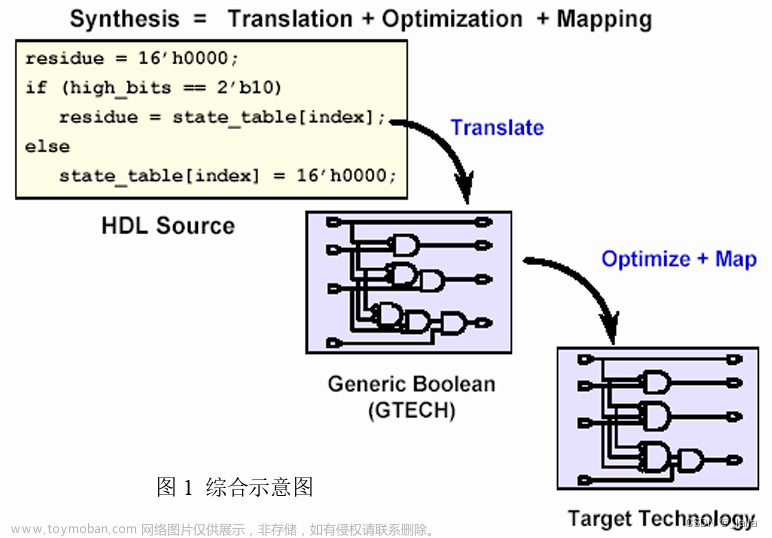

总结

4.1 Warning的产生

DC综合导致该Warning的原因有很多,如位宽不匹配的Error、读取设计时使用Read信号导致模块没有全部读入、例化模块重新赋值了Parameter参数等。

我们只需要将报告中的全部Error解决,该Warning也会随之解决,综合才能够正常进行。

4.2 代码风格

在进行Verilog代码编写时,一定要注意位宽匹配。

在大多数的FPGA集成开发环境中,编译器是能够帮我们自动对齐位宽的,但在DC中,便会报错。

例1:在例化blk_mem_gen_0时,ena位宽赋值为1,这边在DC中会报错,应该修改为ena(1’b1)

blk_mem_gen_0 RAM_0(

.addra(mem_w_addr),

.clka(HCLK),

.dina(mem_wr_data),

.wea(we|cr_en),

.ena(1),

.addrb(mem_r_addr),

.clkb(HCLK),

.doutb(HRDATA),

.enb(1)

);

例2:在寄存器赋值中,位宽不匹配。如在下面的例子中,将slv_reg[0]连接到tcounter寄存器。而tcounter是16位的,slv_reg是32位的,同样也会报错,正确写法应该为.tcounter(slv_reg[0][15:0])文章来源:https://www.toymoban.com/news/detail-808840.html

TimerA TimerA_inist0(

...

.tcounter(slv_reg[0]),

...

)

4.3 网表正确性

只有在综合报告中将所有的Error、ports mismatch、width mismatch、Unable resolve 解决,才能综合出正确的网表,且网表生成后,一定要通过后仿真检查正确性。文章来源地址https://www.toymoban.com/news/detail-808840.html

到了这里,关于【Synopsys Bug记录】DC综合报错(显示warning:Unable to resolve reference)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!