方法1:

1.首先需要用一个数字IO的输入FPGA端口,并将其拖入程序框图中,同时创建一个循环。

2.如果想要在循环中实现累加功能,就可以使用移位寄存器。

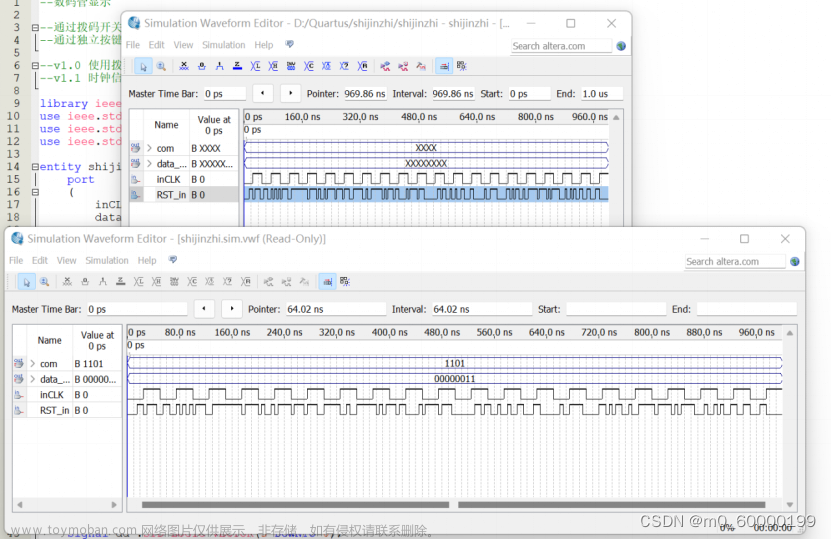

数字输入的当前值和历史值进行比较,用于一个判断大于,来确定是否出现了上升沿。

同时如果想确认上升沿的次数也可以用移位寄存器,如果出现上升沿则计数加1,否则保持原值。

方法2:

1.使用IO的方法节点,FPGA I/O方法节点检测到边沿后,程序框图的计数器值加1,且将计数器的值存储在While循环的移位寄存器内。使用前面板显示控件或局部变量可查看计数器的值。

文章来源:https://www.toymoban.com/news/detail-809739.html

文章来源:https://www.toymoban.com/news/detail-809739.html

文章来源地址https://www.toymoban.com/news/detail-809739.html

文章来源地址https://www.toymoban.com/news/detail-809739.html

到了这里,关于【LabVIEW FPGA入门】使用数字IO卡实现计数器输入功能的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!