一, 什么是异常

异常(Exception)通俗点来讲,就是系统在正常运行的时候出现的非正常事件,这个非正常事件会导致系统状态更改或者其他错误,为了确保系统功能能正常运行,需要一些带有特权的软件代码(exception handler)来采取一些补救措施或者更新系统状态,这个过程被称为异常处理,系统会停止当前程序,并进入handler,在handler处理完成之后,系统会从handler返回,再继续正常运行。

所以可以说,异常就是可以导致当前正常程序被挂起的任何事件。

如下图所示,程序正常执行过程中,发生了异常,程序挂起,并跳转到异常处理函数,在处理完异常后,从异常返回,程序恢复正常运行:

有些处理器架构可能会讲上述过程描述为一个中断,但是在ARM AArch64中,中断是一种由外部产生的,特殊类型的异常。

异常的用途非常广泛,包括以下:

- 模拟虚拟设备

- 虚拟内存管理

- 处理软件错误

- 处理硬件错误

- 调试

- 异常等级跳转或者安全状态切换

- 处理中断(定时器或者外设间的交互)

- 执行状态切换(AArch64和AArch32),也就是interprocessing

当异常发生时,处理器将会停止当前程序的运行,跳转到一段称为异常处理函数的代码来处理该异常,处理结束后将从exception handler返回到之前程序停止的地方继续执行。每一种异常类型都有属于自己的异常处理函数。此外,ARM架构将异常分为同步异常(synchronous exceptions)和异步异常(asynchronous exceptions)。

二,同步异常(synchronous exceptions)

同步异常用一句话概括就是:由处理器执行指令所产生的异常。同步异常和当前处理器所执行的指令流是同步的,因为正是处理器执行了某条指令才导致异常发生。比如,MMU定义了某个内存区间为只读属性,如果CPU对该区间某地址执行了写的指令(如STR),此时一个同步异常将会发生。

同步异常有如下特点:

- 同步异常是由于直接或试图执行指令而产生的。

- 处理异常后返回的地址(返回地址)与导致异常的指令之间的关系,是由arm体系结构定义的。

- 同步异常也称为 精准(precise)异常,因为我们可以知道具体是哪条指令导致的异常,可以精准地知道执行了哪条指令之后系统状态才开始发生变化,并且进入异常处理函数。

同步异常也分了很多种,并且也可能存在 执行一条指令,导致多个同步异常的产生的情况,为了处理多个同步异常同时产生的情况,ARM架构为每种同步异常规定了固定的优先级来处理。

2.1 无效的指令和陷阱异常(Invalid instructions and trap exceptions)

无效的指令有很多种情况,比如:

- Cortex-A73支持的某些指令或者寄存器,A53不支持,对于A53来讲就是无效的指令,如果执行这样的指令或者访问不支持的寄存器,处理器将进入 未定义的异常(UNDEFINED Exception)。

- 有些指令或者寄存器只针对特定的异常等级有效,如果在其他的异常等级下执行这样的指令或者访问这些寄存器,也将进入未定义的异常(UNDEFINED Exception)。

此外,ARM架构还允许操作系统或者hypervisor为更低异常等级的某些操作(比如读取一个特定的寄存器)设置陷阱。当处理器在这些更低异常等级执行这些操作的时候,将会触发一个异常。

例如,EL1上的操作系统内核可能会在EL0上禁用使用浮点指令,以节省在应用程序之间进行上下文切换时的时间(浮点寄存器通常有128-bit的宽度,是普通通用寄存器的两倍,上下文切换时,需要将所有GPR的值压入栈或者从栈中恢复到GPR)。这被称为惰性上下文切换;例如,如果在上下文切换之前没有使用SIMD/浮点(FP)单元(NEON),则出栈入栈的寄存器数量可以减少。所以,一般情况下,在应用程序跑的EL0异常等级下,禁用浮点指令,并且使用一个陷阱异常来处理边缘情况(少数情况下,某些应用程序需要开启浮点运算)。

在这种情况下,OS内核可以通过禁用SIMD/FP单元来监视SIMD/FP操作的状态。当执行FP或SIMD指令时,陷阱异常被带到EL1的OS内核。然后,内核可以启用SIMD/FP单元,以执行之前失败的指令,并设置一个标志,说明已经使能了SIMD/FP单元。这确保了在下一个上下文交换中,将大型SIMD/FP寄存器文件包含在上下文切换的寄存器上下文中。如果在下一个上下文切换中没有发现这个使能标志,则不需要包含SIMD/FP寄存器。

这种设置陷阱异常的能力对于虚拟化尤为重要。关于AArch64 的虚拟化操作,可以参考:AArch64 virtualization guide。

2.2 内存访问产生的异常

在访问内存时也会产生同步异常。可能的原因有:

- MMU使能后,MMU进行地址转换时进行检查产生的。

- 由内存系统(比如DDR)返回的错误。

比如,将MMU使能后,使用Load或者store指令访问内存的操作将会受到MMU的检查。比如对一些地址空间的内存属性设置了只读,这时候CPU对该区域进行写操作,还比如对一些地址空间设置了只有较高的异常等级才能去访问(即该区域具有特权),此时若CPU处于非特权状态去访问该区域,MMU对这些操作都会进行检查,并将这些操作拦截,然后触发一个MMU 错误的异常。由于MMU产生的错误是同步的,所以该异常的产生将会在内存访问之前。

此外,内存访问也同样会产生异步异常,比如SEerror。这个将会在下文中描述。

在AArch64中,同步的Data abort(数据访问中止)将会产生一个同步异常,如果是异步的abort,将会产生一个SError中断异常。

2.3 产生异常的指令

ARM架构提供了一些显式的指令,用于产生一个异常。这些指令用于实现系统调用接口,以允许低特权的软件向高特权的软件请求服务。这些方法有时被称为系统调用,通常用于基于软件的API。

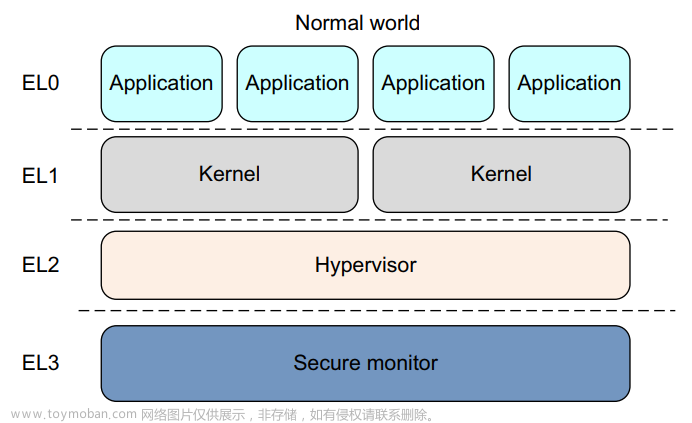

ARM架构包含三个异常产生的指令:SVC,HVC以及SMC。这三个指令仅仅是用于产生一个异常,并以此让处理器在各个异常等级中切换:

-

Supervisor Call (SVC),SVC指令用于EL0切换到EL1,比如一个工作在EL0的用户程序,可以使用SVC指令,请求一个工作在EL1操作系统的服务。

-

Hypervisor Call (HVC),如果虚拟化在当前架构中被实现,比如在虚拟机程序中,工作在EL1的操作系统可以通过HVC指令,向工作在EL2的hypervisor请求服务,可以进行不同的OS间的切换。

-

Secure Monitor Call (SMC),如果安全扩展功能在当前架构中被实现,则程序如果想要在安全世界(secure world)和非安全世界(normal world,non-secure world)切换,需要通过使用SMC指令来实现。

-

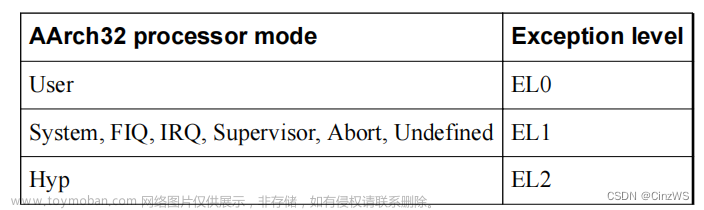

此外,异常等级切换(低等级向高等级切换)需要遵守如下图规则:

如果当前处理器处于EL0,则它不能直接使用HVC或者SMC,切换到更高等级。只能使用HVC指令先进入EL1,才可以切换到其他更高的异常等级。

由于异常无法向更低等级切换,换句话说,如果是由高等级切到低等级,而是使用ERET指令。总结如下: -

系统调用(System Call),切换(SVC,HVC,SMC)到更高等级。

-

返回(ERET,exception return)到更低等级。

所以,如果处于EL2的处理器执行SVC指令是不会切到EL1的。

2.4 调试异常 Debug exceptions

调试异常也是同步异常,该异常会被路由到当前调试器所处的异常等级。然后,调试器代码执行得很像异常处理程序代码一样。调试异常有很多种,包括如下:

- Breakpoint Instruction exceptions

- Breakpoint exceptions

- Watchpoint exceptions

- Vector Catch exceptions

- Software Step exceptions

关于调试异常的具体介绍,可以查看AArch64 self-hosted debug guide。

三, 异步异常 Asynchronous exceptions

上文我们提到过,同步异常是由于处理器执行指令触发的异常,而有些异常是产生于处理器外部,因此无法和CPU当前执行的指令流同步,这种和CPU当前执行的指令没有直接关系的异常,我们称为异步异常(Asynchronous exceptions),并且这种异常一般是由CPU外部的系统事件产生的,这可能是软件需要响应的系统事件,如计时器的活动或屏幕的触摸,但是我们并不知道它们什么时候会发生。

根据定义,如果一个异常不是同步的,则该异常是异步异常。中断(interrupts)实际上就是异步异常的一种。

在发生异步异常时,程序流将被中断,并传递给handler以专门处理此外部请求。因为不可能准确地保证何时会发生异步异常,所以AArch64架构只要求它在有限的时间内发生。

3.1 物理中断 Physical interrupts

物理中断是指为了响应来自处理器外部的信号而产生的中断,通常是由外围设备产生的。处理器并不需要主动地不断轮询这种外部信号,系统会通过产生中断的方式来通知处理器,处理器收到中断后,会进入相应的中断处理函数以响应该信号。

比如,系统中可能使用UART(Universal Asynchronous Receiver/Transmitter)连接CPU,并与外界通信。当UART收到数据后,系统中需要有个机制来告诉CPU,UART收到新数据了,CPU这边需要接收并处理这些数据。其中一种机制就是中断:UART可以产生一个中断来通知CPU有新数据需要处理。

在复杂的SOC系统中,可能有非常多的带有优先级的中断源,并且包含中断嵌套的能力:在处理较低优先级的中断时,更高优先级的中断可以打断低优先级中断的处理,在处理完高优先级中断后,再接着处理低优先级中断。

处理器在处理这种嵌套中断的响应速度可能是系统设计中的一个关键问题,这被称为中断延迟(interrupt latency)。

3.2 系统错误异常 SError

当内存系统响应了一些不正常的事件,并反馈给处理器,将会产生一种 SError的异步异常。在正常操作流程中,我们不希望有这种异常发生,但是处理器有必要知道它的一些和内存系统的交互是否触发了这种异常。这种异常的上报是异步的,导致这种异常发生的指令(比如读写内存系统的指令,load/store)可能已经执行完了。

一种典型的SError异常就是来自外部的异步中止,比如有:

- 内存总线上的错误,处理器发出一个访问内存的请求(比如读写),首先会经过MMU的检查(假设MMU被使能),MMU检查通过后,会传到内存总线上,在内存总线上遇到的错误。

- 在一些RAM上进行 奇偶检验或者错误纠正(Parity or Error Correction Code (ECC)时发生的错误,比如一些内置的cache。

- 将脏数据由cache line中写回到外部内存系统中发生的错误。

SErrors被视为一个单独的异步异常类型,因此用户代码通常对这些情况有单独的处理程序。并且SError异常的产生是由具体的架构实现来定义的。

3.3 IRQ和FIQ 中断

Arm体系结构有两种异步异常类型:IRQ和FIQ,旨在用于支持外围设备中断的处理。处理器会引出两个信号线:IRQ和FIQ,这些是用于传入外部事件,如设置的计时器(timer)超时了,这并不代表系统错误。IRQ和FIQ是外部信号与处理器的指令流之间的,虽然是异步的,但是预期的事件。IRQ和FIQ有独立的路由控制,通常用于实现安全和非安全中断。关于这两种中断类型的具体使用方式,由具体的架构实现来定义。

在老版本的Arm体系结构中,FIQ被用作更高优先级的快速中断。这与AArch64不同,在AArch64中,FIQ与IRQ具有相同的优先级。

在几乎所有的情况下,中断控制器(Generic Interrupt Controler)都与系统中的AArch64处理器成对使用,GIC用于收集、优先级排序和处理所有要发送到处理器的中断。所有的ARM架构实现都使用(GIC)架构来管理IRQs和FIQs。GIC执行中断管理、优先级和路由任务,为每个物理中断类型都提供一个中断号。详情可以参考 Arm Generic Interrupt Controller v3 and v4 guide。

3.4 虚拟中断 Virtual interrupts

如果系统中实现了虚拟化,则对中断处理有了更复杂的需求,一些中断可能由hypervisor处理,有些中断可以在VM(虚拟机程序)中处理。被虚拟机程序看到的中断就是虚拟中断。虚拟中断可以由软件产生,也可以由连接到中断控制器的外设产生。因此想要支持虚拟中断,必须要额外的机制,在AArch64架构中支持以下虚拟中断:文章来源:https://www.toymoban.com/news/detail-810926.html

- vSError, Virtual System Error

- vIRQ, Virtual IRQ

- vFIQ, Virtual FIQ

虚拟中断按照其中断类型被控制,这些虚拟中断的功能与物理对应的中断相同,但是它们只能向EL1发出信号。虚拟中断可以从EL2处的虚拟机管理程序或使用中断控制器生成。hypervisor必须在Hypervisor Configuration Register(HCR_EL2)中设置相应的控制bit。例如,要启用vIRQ信令,系统管理程序必须设置HCR_EL2的IMO位,此设置将物理IRQ异常路由到EL2,并允许将虚拟中断信号发送到EL1。

在寄存器 HCR_EL2中,有三个bit来控制虚拟中断的产生: - VSE,设置这个bit将注册一个 vSError.

- VI ,设置这个bit将注册一个vIRQ.

- VF, 设置这个bit将注册一个 vFIQ.

设置其中一个bit相当于一个中断控制器断言了其中一个虚拟中断信号到一个虚拟CPU。该方法的一个影响是:需要hypervisor来模拟虚拟机程序中的中断控制器的操作。当频繁地这样操作时,这可能会导致系统大量的开销,因此建议直接使用中断控制器模拟一个虚拟中断。

GICv2及更高版本提供物理CPU接口和虚拟CPU接口,并且同时支持物理中断和虚拟中断。关于GIC的详细使用可以参考: Arm

Generic Interrupt Controller v3 and v4.。关于虚拟中断,参考 AArch64 virtualization guide。

四,异常屏蔽(Masking)

对于异步异常:可以暂时屏蔽物理和虚拟的异步异常。这意味着异步异常可以保持在挂起状态,直到它们被停止屏蔽,并被处理器接收异常。这对于处理嵌套的异常特别有用。

对于同步异常:ARM架构无法屏蔽同步异常。这是因为同步异常是由指令的执行直接引起的,因此,如果它们被搁置或忽略,将会阻塞CPU的执行。

在2021年的扩展中,Armv8.8-A和Armv9.3-A增加了不可屏蔽的中断(Non-maskable interrupt,NMI)支持。当NMI被支持和启用时,可以通过该功能将具有超优先级(Superpriority)的中断发送给给处理器。文章来源地址https://www.toymoban.com/news/detail-810926.html

到了这里,关于ARMv8-AArch64 的异常处理模型详解之异常类型 Exception types的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![Yocto系列讲解[技巧篇]92 - armv8 aarch64兼容armv7 32位程序运行环境](https://imgs.yssmx.com/Uploads/2024/01/820513-1.png)