- 本文实现的是一个简单的计数器,模块中包含时钟信号和复位信号,计数使用的是一个四位的输出,复位键有效时,计数器置零,当时钟信号上升沿时,计数加一,实现计数。(仅供参考)

- 建立工程counter,并新建一个设计文件命名为:counter

3.打开counter文件,进行计数器的模块编码:

4.点击 RTL ANALYSIS→Open Elaborated Design→Schematic 项,可以查看 RTL 描述后的结构,如下所示

5.新建一个仿真文件命名为counter_simulation

6.点开counter_simulation进行模块仿真的编码:

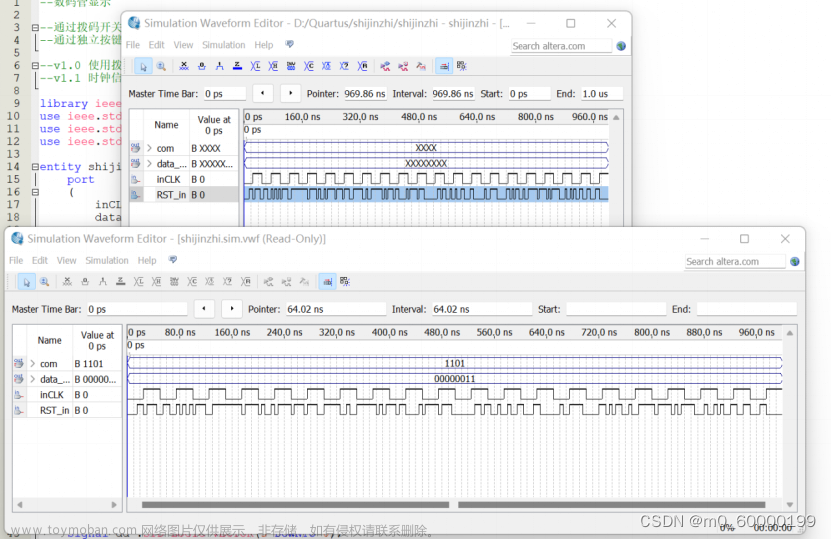

7.点击SIMULATION→Run Simulation→Run Behavioral Simulation进行

仿真,如下所示:

8.模块设计代码:文章来源:https://www.toymoban.com/news/detail-811668.html

module counter(

input clk,

input rst,

output reg[3:0] out // 4位计数器

);

always @ (posedge clk or posedge rst)

begin

if(rst) begin

out<=0;

end

else begin

out<=out+1;

end

end

endmodule仿真设计代码文章来源地址https://www.toymoban.com/news/detail-811668.html

module counter_simulation(

);

reg clk;

reg rst;

wire [3:0] out;

counter c(.clk(clk),.rst(rst),.out(out)); //例化

initial begin //初始化

clk=0;

rst=1;

#10;

rst=0;

end

always #5 clk=~clk;

initial begin

# 200 //仿真持续时间

$finish;

end

endmodule到了这里,关于FPGA Vivado环境下实现计数器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!