提示

- 该博客主要为个人学习,通过阅读官网手册整理而来(个人觉得阅读官网的英文文档非常有助于理解各个IP特性)。若有不对之处请参考参考文档,以官网文档为准。

- 阅读该文章,可以先查看AArch64 Exception Model学习,再来看该文章会非常简单

1. 执行状态

该体系结构只有AArch32执行状态。执行状态定义了处理器的执行环境,包括:

- 支持寄存器位宽

- 支持指令集

- 还有以下几方面

- 执行模型

- PMSA

- 编程模型

2. 异常等级

Armv8-R AArch32的异常等级为: EL0~EL2

EL0:Applications

EL1: 通常被描述为特权的操作系统内核和相关函数

EL2: Hypervisor

- EL0具有最低的软件执行特权,在EL0处的执行称为非特权执行。

- 从1到2表示增加了软件执行特权。

- EL2提供了对处理器虚拟化的支持。

只有在发生异常或从异常返回时,执行才能在异常级别之间切换: - 在发生异常时,异常级别会增加或保持不变。在发生异常时,异常级别无法降低。

- 当从异常返回时,异常级别会降低或保持不变。当从异常返回时,异常级别无法增加。

发生异常时执行更改或保留在的异常级别称为异常的目标异常级别,并且: - 每个异常类型都有一个目标异常级别:

- 隐含在异常的性质中

- 由系统寄存器中的配置位定义

- 异常目标不能是EL0

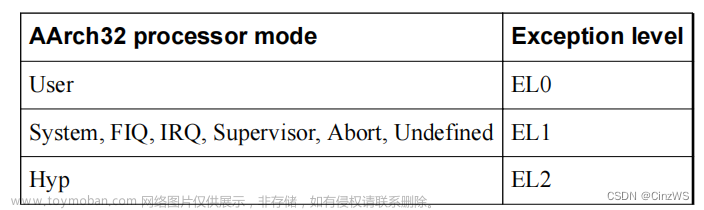

3. AArch32执行模式

当处于AArch32状态时,处理器可以以几种模式之一执行。每个模式都与一个异常级别相关联。有些模式有一些通用寄存器的私有、bank副本。异常情况会导致处理器切换到一个特定的模式。

下表显示了AArch32处理器模式,以及每个模式的异常级别

4. 支持v8内存类型

Armv8提供了互斥的内存类型。内存映射中的每个地址都有一个由MPU决定的内存类型。

内存类型:

- Normal:这通常用于大容量内存,包括读/写内存和只读内存。

- Device:这通常用于外设,它们可能是读敏感或写敏感的。Arm架构限制了对设备内存的排序、合并或推测。

Armv8架构将设备内存细分为几个子类型。这些属性涉及以下属性: - G:收集。将请求收集并合并为单个事务的能力。

- R:重新排序。重新排序事务的能力。

- E:早期承认。接受来自互连的事务的早期确认的能力。

下表描述了Armv8的内存类型。

5. 系统寄存器

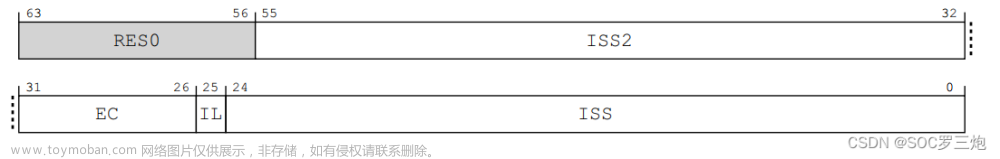

系统寄存器提供控制和状态信息。例如,寄存器可能提供有关core已采取的abort exception的综合信息,或提供一个启用或禁用缓存的控制。

系统寄存器使用一种标准的命名格式,<register_name>.<bit_field_name>,来识别特定的寄存器以及寄存器内的控制位和状态位。位也可以用它们在形式<register__name>[x:y]或通用形式bits[x:y]中的数字位置来描述。

系统寄存器包括:

- ID registers.

- General system control registers.

- Debug registers.

- Generic Timer registers.

- Performance Monitor registers.

- GIC CPU interface registers.

6. 通用寄存器

Armv8-R AArch提供了对15个32位通用寄存器R0-R14的访问。

其中,有两个有专门的或受限制的用途:

- R13通常被标识为SP,即堆栈指针。

- R14通常被标识为LR,即链接寄存器。

当然,还有一个32位的程序计数器(PC),R15。

其中一些寄存器是bank上的。这些是使用相同的标识符访问的多个物理寄存器,执行模式决定了访问哪个寄存器。例如: - 在abort模式下,对SP的访问将访问物理寄存器SP_abt。

- 在user模式下,对SP的访问将访问物理寄存器SP_usr。

在Hypervisor模式下,还有一个附加的专用链接寄存器,ELR_hyp。

高级SIMD和浮点指令使用了另一组寄存器。这些寄存器可以作为32位单精度寄存器S0-S31访问,也可以作为64位双精度寄存器D0- D31访问,或128位四元寄存器Q0-Q15访问,但这些是相同数据的不同视图。数据可以在高级SIMD和浮点寄存器和整数寄存器之间传输。

7. 程序状态寄存器

程序状态寄存器包括当前程序状态寄存器(CPSR)、应用程序状态寄存器(APSR)和已保存的程序状态寄存器(SPSR)。

CPSR包括:

- 可以由某些指令设置并决定其他指令的行为的标志。

- 反映处理器的当前模式和其他状态的状态位。

- 控制位决定例如中断掩蔽和数据大小端。

CPSR中的许多位都限制了使用,并且只能进行修改: - 在特权模式。

- 作为异常或异常返回的副本。

呈现给运行在异常级别EL0上的应用程序的CPSR的视图称为APSR。

每个可以采用异常的模式都有自己的SPSR。每个SPSR用于在发生异常时保存CPSR的副本,从而允许在异常返回时恢复它。

8. 数据类型

AArch32体系结构支持以下整数数据类型:

- Byte (8 bits).

- Halfword (16 bits).

- Word (32 bits).

- Doubleword (64 bits).

该架构还支持半精度、单精度和双精度的浮点数据类型。

9. 内存模型

该架构定义了PMSAv8内存模型,以确定:

- 对指令和数据执行内存访问的排序规则和其他限制。

- 内存访问的权限和其他属性,以及它们是如何由MPU确定的。

Cortex-R52+支持PMSAv8,并且没有MMU或地址转换功能。即使MPU不执行任何实际的转换,该函数仍然被称为转换。这是因为物理地址总是与虚拟地址是相同的。虚拟地址和物理地址是指由指令生成的转换前和转换后在总线上可见的地址。虚拟地址和物理地址可以作为Cortex-R52+的一套地址来处理。

10. GIC架构

Cortex-R52+处理器支持GIC架构的三个组件:分发器(Distributor)、再分发器(Redistributor)和CPU接口(CPU interface)。

分发器包含支持SPIs的寄存器,除了优先级逻辑,它计算每个核心的最高优先级等待中断。再分发器包含支持PPIs和SGIs的寄存器。CPU接口跟踪当前正在运行的优先级和虚拟中断。它决定了核心是否被中断。

中断被配置为对边缘触发或电平敏感的。每个中断都具有可编程启用、优先级(0-31)、组(0或1)、路由(仅SPI)配置和当前状态。

当接收到中断信号时,它被pending。根据其配置,一个pending中断可能会中断一个core的执行。软件可以读取中断的ID,并且激活(active)它。软件还可以结束一个中断,从而使其失效(deactives)。

虚拟中断是由系统管理程序(hypervisor)软件写入CPU接口中的列表寄存器而创建的,通常是为了响应物理中断。虚拟中断的处理方式与物理中断类似,但只能在core处于EL0或EL1中时中断它。当一个虚拟中断被停用(deactive)时,可以对其进行配置,即当该虚拟中断被停用时,相应的物理停用消息也会发送给GIC分发器。

该章会单独写几篇文章说明,别担心文章来源:https://www.toymoban.com/news/detail-812763.html

参考文献

Arm® Cortex®-R52+ Processor Technical Reference Manual文章来源地址https://www.toymoban.com/news/detail-812763.html

到了这里,关于Armv8-R AArch32 architecture概念学习的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!