《EDA技术实用教程(第六版)》学习笔记——第一章

1、 专业名词英文缩写

- ASIC(Application-Specific Integrated Circuit):专用集成电路

- SOC(System-on-Chip):片上系统

- SOPC(System-on-Programmable-Chip):片上可编程系统

- EDA(Electronic Design Automation):电子设计自动化

- HDL(Hardware Description Language):硬件描述语言

- FPGA(Field-Programmable Gate Array):现场可编程门阵列

- CPLD(Complex Programmable Logic Device):复杂可编程逻辑器件

- CAD(Computer-Aided Design):计算机辅助设计

- CAM(Computer-Aided Manufacturing):计算机辅助制造

- CAT(Computer-Aided Testing):计算机辅助测试

- CAE(Computer-Aided Engineering):计算机辅助工程

- IP(Intellectual Property ):知识产权

- PCB(Printed Circuit Board):印刷电路板

- IEEE(Institute of Electrical and Electronics Engineers):电气和电子工程师协会

- RTL(Register-Transfer Level):寄存器传输级

- ESL(Electronic System-Level):电子系统级

- STA(Static Timing Analysis):静态时序分析

2、EDA的定义

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VerilogHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

内容包含:

-

IC设计制造

-

FPGA/CPLD应用

-

PCB(印刷电路板)设计

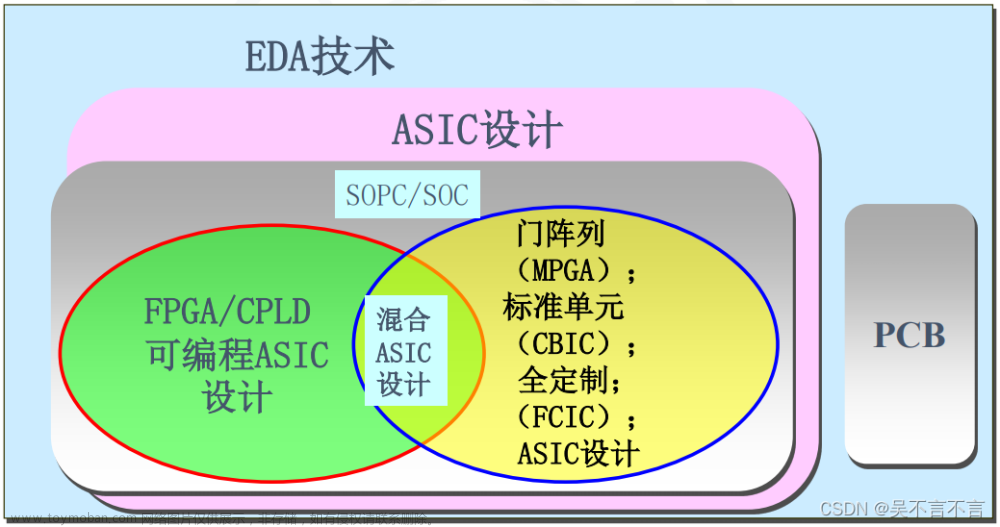

3、 三种途径实现EDA技术最终目标ASIC

-

可编程逻辑器件:

FPGA 和CPLD 是实现这一途径的主流器件,它们的特点是直接面向用户,具有极大的灵活性和通用性,使用方便,硬件测试和实现快捷,开发效率高,成本低,上市时间短,技术维护简单,工作可靠性好等。 -

半定制或全定制ASIC:

基于EDA设计技术的半定制或全定制ASIC,根据它们的实现工艺,可统称为掩模(mask)ASIC,或直接称ASIC。可编程ASIC与掩模ASIC相比,不同之处在于前者具有面向用户的灵活多样的可编程性。掩模ASIC大致分为门阵列ASIC、标准单元ASIC和全定制ASIC。 -

混合ASIC:

主要指既具有面向用户的FPGA可编程功能和逻辑资源,同时也含有可方便调用和配置的硬件标准单元模块,如CPU、RAM、ROM硬件加法器、乘法器、锁相环等。

4、 硬件描述语言(HDL,Hardware Description Language)

-

Verilog HDL(Verilog):

Verilog的部分语法是参照C语言的语法设立的,具有很多C语言的优点,代码简明扼要,使用灵活,语法规定不是很严谨,很容易上手。 -

VHDL:

它的英文全名是VHSI hardware description language,VHSIC是very high speed integrated circuit(超高速集成电路)的缩写。 -

System Verilog:

是一种新的硬件描述语言。System Verilog 主要定位于集成电路的实现和验证流程,并为系统级设计流程提供了强大的链接能力。 -

System C:

是C++语言的硬件描述扩展,主要用于ESL(电子系统级)建模与验证。

5、 HDL综合

综合(synthesis):将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。事实上自上而下的设计过程中每一步都可称为一个综合环节。

-

从自然语言转换到Verilog语言算法表述,即自然语言综合。

-

从算法表述转换到寄存器传输级(register transport level,RTL)表述,即从行为域到结构域的综合,即行为综合。

-

从RTL级表述转换到逻辑门(包括触发器)的表述,即逻辑综合。

-

从逻辑门表示转换到版图级表述(ASIC设计)或转换到FPGA的配置网表文件,可称为版图综合或结构综合。

6、 自顶向下的设计技术

-

自底向上的设计方法

特点是必须首先关注并致力于解决系统最底层硬件的可获得性,以及它们的功能特性方面的诸多细节问题;在整个逐级设计和测试过程中,始终必须顾及具体目标器件的技术细节。多数情况下,自底向上的设计方法是一种低效、低可靠性、费时费力且成本高昂的设计方案。 -

自顶向下的设计方法

只有在 EDA 技术得到快速发展和成熟应用的今天才成为可能。当今,自顶向下的设计方法已经是 EDA技术的首选设计方法,是ASIC或FPGA开发的主要设计手段。

7、 基于EDA软件的FPGA/CPLD开发流程

开发流程为:设计输入(原理图/HDL文本编辑)→功能仿真→综合(逻辑综合,生成网表文件)→适配(结构综合,生成下载文件)→时序仿真→编程下载→硬件测试

-

设计输入(原理图/HDL文本编辑):

图形输人通常包括原理图输人、状态图输人和波形图输人三种常用设计方法,HDL文本输入这种方式与传统的计算机软件语言编辑输人基本一致。 -

综合(逻辑综合):

整个综合过程就是将设计者在EDA平台上编辑输人的HDL文本、原理图或状态图形描述,依据给定的硬件结构组件和约束控制条件进行编译、优化、转换和综合,最终获得门级电路甚至更底层的电路描述网表文件。为达到速度、面积、性能的要求,往往需要对综合加以约束,称为综合约束。在综合后,综合器一般都可以生成一种或多种文件格式网表文件,如EDIF、VHDL、Verilog、VQM等标准格式。 -

适配:

适配器也称结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件,如 BIT、BIN、SOF、POF格式的文件。适配完成后可以利用适配所产生的仿真文件作精确的时序仿真测试,同时产生可用于编程的文件。 -

时序仿真与功能仿真、静态时序分析:

在编程下载前必须利用 EDA 工具对适配生成的结果进行模拟测试,就是所谓的仿真。

**(i)时序仿真:**时序仿真的仿真文件必须来自针对具体器件的综合器与适配器。综合后所得的EDIF、VOM等网表文件通常作为FPGA适配器的输入文件产生的仿真网表文件中包含了精确的硬件延迟信息。

**(ii)功能仿真:**是直接对HDL、原理图描述或其他描述形式的逻辑功能进行测试模拟,以了解其实现的功能是否满足原设计的要求,一般先功能仿真再综合、适配。

**(iii)静态时序仿真:**若纯粹分析电路各个部分的延迟,那么就需要进行静态时序分析(static timinganalysisSTA)。静态时序分析可以用参数直观地评价设计的电路的性能,现代的 EDA 工具往往通过使用门级功能仿真和静态时序分析来联合验证评估电路的功能与性能,而代替复杂耗时的时序仿真。 -

编程下载:

把适配后生成的下载或配置文件,通过编程器或编程电缆向FPGA或CPLD下载以便进行硬件调试和验证(hardware debugging)。通常,将对CPLD的下载称为编程(program),对FPGA中的SRAM进行直接下载的方式称为配置(configure),但对于反熔丝结构和Flash结构的FPGA的下载和对FPGA的专用配置ROM的下载仍称为编程。 -

硬件测试:

最后是将含有载人了设计文件的 FPGA或CPLD的硬件系统进行统一测试,以便最终验证设计项目在目标系统上的实际工作情况,以排除错误,改进设计。

8、 ASIC及其设计流程

ASIC是相对于通用集成电路而言的,ASIC主要指用于某一专门用途的集成电路器件。分为数字ASIC、模拟ASIC和数模混合ASIC。

9、常用EDA工具

-

设计输入编辑器

-

HDL综合器

性能良好的FPGA/CPLD设计的HDL综合器有如下三种:

Synopsys公司的DC FPGA综合器。

Synopsys公司的Synplify Pro综合器。

MentorLeonardoSpectrum综合器、 Precision RTL 。

两种使用模式:图形模式和命令行模式(Shell模式)。 -

仿真器

按处理的硬件描述语言类型分,HDL仿真器可分为:

(1) VHDL仿真器。

(2) Verilog仿真器。

(3) Mixed HDL仿真器(混合HDL仿真器,同时处理Verilog与VHDL)。

Mentor的ModelSim

(4) 其他HDL仿真器(针对其他HDL语言的仿真)。

按仿真的电路描述级别的不同,HDL仿真器可以单独或综

合完成以下各仿真步骤:

(1) 系统级仿真。

(2) 行为级仿真。

(3) RTL级仿真。

(4) 门级时序仿真。 -

适配器

适配器的任务是完成目标系统在器件上的布局布线。适配,即结构综合通常都由可编程逻辑器件的厂商提供的专门针对器件开发的软件来完成。这些软件可以单独或嵌入在厂商的针对自己产品的集成EDA开发环境中存在。 -

下载器

10、 Quartus概述

Quartus II包括模块化的编译器。编译器包括的功能模块有分析/综合器(analysis&synthesis)、适配器(fitter)、装配器(assembler)、时序分析器(timing analyzer)、设计辅助模块(design assistant)、EDA网表文件生成器(EDA netlist writer)、编辑数据接口(compiler database interface)等。其中13.1版本支持的早期器件系列较多,而16.1版本支持 Cyclone 4系列以后的器件系列,两者都没有内置的门级波形仿真器,需要借助ModelSim ASE或ModelSim AE来进行仿真。

11、 IP核

IP就是知识产权核或知识产权模块的意思。著名的美国Dataquest咨询公司将半导体产业的IP定义为用于ASIC或FPGA中的预先设计好的电路功能模块。IP分软IP、固IP和硬IP。

-

软IP(Soft IP):

是用VHDL/Verilog HDL等硬件描述语言描述的功能块,但是并不涉及用什么具体电路元件实现这些功能。软IP 通常是以硬件描述语言 HDL源文件的形式出现。(RTL HDL描述→灵活更改) -

固IP(Firm IP):

是完成了综合的功能块。它有较大的设计深度,以网表文件的形式提交客户使用。(门级描述→有限更改) -

硬IP(Hard IP):

提供设计的最终阶段产品:掩模。由于市场对IP核的需求各大FPGA厂家继续开发新的商品IP,并且开始提供“硬件”IP,即将一些功能在出厂时就固化在芯片中。(版图形式→固定工艺难以更改)

IP种类:

-

处理器核

CPU/FPU/GPU/DSP/MCU/NPU -

硬件加速模块

图像处理/视频编解码/AI加速音频CODEC -

高速接口

USB/PCIe/HDMI/SerDes -

外设

GPIO/SPI/UART/Timer/I2C/PWM文章来源:https://www.toymoban.com/news/detail-815244.html

如有需要课本PDF与课件可以评论区联系发邮箱。文章来源地址https://www.toymoban.com/news/detail-815244.html

到了这里,关于《EDA技术实用教程(第六版(黄继业, 潘松))》学习笔记——第一章的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!