👉个人主页: highman110

👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

目录

1.1 过孔添加与设置

1.2 添加差分对

1.3 添加布线集合

1.1 过孔添加与设置

布线换层时需要由过孔贯穿,而软件本身是没有过孔可以直接调用的,所以需要手动添加和设置。一般我们使用的都是通孔,盲孔和埋孔成本高,一般不使用。

孔径、线宽、线距、铜厚这些都和工厂的加工工艺相关,一般工厂的加工能力如下(从凡亿电路的材料上截取的,不同厂家工艺能力会有不同):

过孔的大小,一般可以按如下阶梯设置:

1)8/8mil,过孔选择12mil(0.3mm);

2)6/6mil,过孔选择12mil(0.3mm);

3)4/4mil,过孔选择8mil(0.2mm);

4)3.5/3.5mil,过孔选择8mil(0.2mm);

5)3.5/3.5mil,过孔选择4mil(0.1mm,激光打孔,盲埋孔);

6)2/2mil,过孔选择4mil(0.1mm,激光打孔,盲埋孔)。

以上线宽线距规则设置指的是线到孔、线到线、线到焊盘、线到过孔、孔到盘等元素之间的大小。

选择过孔的时候还要注意过孔的通流能力,一般情况下通流情况如下表,注意设计时要留有余量:

| 过孔孔径(mil) |

温升10度时的通流(A) |

|

| 理论计算值(A) |

设计推荐值(A) |

|

| 10 |

1.1848 |

1 |

| 12 |

1.3415 |

1.2 |

| 16 |

1.5521 |

1.4 |

| 20 |

1.7646 |

1.5 |

过孔有常规开阻焊过孔(过孔开窗,也就是在封装制作时增加了阻焊层,如果要将过孔打在焊盘上或者为了测试需要把过孔露出来就用此类)和常规塞孔过孔(盖绿油的孔,封装上没有阻焊层,通常用的就是此类)。过孔封装制作规格如下表:

|

|

常规开阻焊过孔 |

过孔简单描述(单位:mil) 孔径/环径/阻焊直径/Flash直径 |

常规塞孔过孔 |

过孔简单描述(单位:mil)孔径/环径/Flash直径 |

| 1 |

|

|

VIA6_F |

6/14/00 |

| 2 |

VIA8 |

8/16/20/25 |

VIA8_F |

8/16/25 |

| 3 |

VIA10 |

10/22/27/32 |

VIA10_F |

10/22/32 |

| 4 |

VIA12 |

12/24/29/36 |

VIA12_F |

12/24/36 |

| 6 |

VIA16 |

16/30/35/48 |

VIA16_F |

16/30/48 |

| 7 |

VIA18 |

18/34/39/54 |

VIA18_F |

18/34/54 |

| 8 |

VIA20 |

20/35/40/50 |

VIA20_F |

20/35/50 |

| 9 |

VIA24 |

24/40/45/60 |

VIA24_F |

24/40/60 |

| 10 |

VIA28 |

28/50/55/70 |

VIA28_F |

28/50/70 |

过孔添加步骤:

1、因为过孔实际上是个焊盘,所以要先添加封装的路径 ,padpath:焊盘文件路径,psmpath,flash文件路径。

2、setup-constraint-constraint manager打开规则管理器,或者直接点击图标。点击physical constraint set--all layers--VIA,找到想要添加的过孔双击即可添加,然后点击OK完成。

3、此时在走线命令下,option面板选中想要添加的过孔后,双击左键即可添加。

3、此时在走线命令下,option面板选中想要添加的过孔后,双击左键即可添加。

4、我们打过孔数量较多时,尽量不要排在同一排,推荐交错分排打过孔,避免平面割裂。

1.2 添加差分对

设计中不乏有差分信号的情况,添加差分对可以使这一对线同时布线,基本做到对内等长。

添加差分对有几种方法:

1、手动添加。Logic--assign differential pair,点击Net栏中想要设置差分对的网络,依次点击P和N端(也可以在option面板勾选net ,layout界面直接点击与网络连接的两个引脚,对于没有命名的网络可以用此方法),点击后此网络名会出现在下面Net1和Net2中,然后在diff pair name给此差分对命名,然后点击add,即可完成添加。注意不点add直接点OK是不行的。

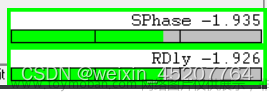

2、使用规则管理器添加。点击physic--all layers(spacing--all layers也可以),选中要设置为差分对的信号,如下随便拿了两个信号举例。Create--differential pair,然后命名差分对,点击create即可完成创建。想要删除这个差分对的设置,找到刚刚命名的差分对,右键--delete,即可完成删除。

3、自动模糊添加。这个操作在原理图网络命名比较规范时可以操作,比如差分对都是以P、N结尾或者以+、-结尾。Logic--assign differential pair--auto generate,填入尾缀,点击generate即可完成添加。

1.3 添加布线集合

在设计中,通常会有一些信号是同一类信号,同时适用同一种约束规则,这时就可以对这些信号进行分组,把同类信号添加到一个集合里。

软件有如下几种集合类型:

Bus:16.6以前用于归集某类信号的一个集合,可以直接对bus设置所有规则;

Class:仅用于设置线宽、线距的信号集合;

Net-Group:16.6以后用于归集某类信号的一个集合,可以直接对Net-Group设置所有规则;

Match-Group:仅用于某类信号的等长参数。

设置class/net group操作步骤:

Physical-net-all layers-选中需要添加进class的网络-右键-create-class,命名class,勾选下图红框,选中的话,在physical创建的class,会同步出现在spacing里。添加class后直接在class上选中规则就可以驱动所有信号了,不用一个一个去设置规则。创建net group的方法类似。

文章来源:https://www.toymoban.com/news/detail-815752.html

文章来源:https://www.toymoban.com/news/detail-815752.html

文章来源地址https://www.toymoban.com/news/detail-815752.html

文章来源地址https://www.toymoban.com/news/detail-815752.html

到了这里,关于【allegro 17.4软件操作保姆级教程五】布线前准备之过孔、差分对、布线集合添加的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!