提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

关于allego17.4差分对组内以及组间等长的设置以及操作方法,差分线不仅存在组内等长,有的还存在组间等长。

一、描述

现已四组差分数据线为例进行设置,原理图如下

注:此原理图只为演示本次差分设置操作使用,其不具有任何实用性功能,且差分对的设置已在原理图中完成DATA0/1/2/3共四组,不在PCB中在论述:

PCB中元器件摆放位置如下图:

二、组内差分设置

1、差分走线线宽/线距=0.102mm/0.102mm,此差分对规则设计与应用不在此论述

2、选择进入规则管理器“Constraint Manager->Electrical->Net->Differential Pair ”中Static Phase中Tolerance中下方的单位:此处设置为mm:

3、同时设置DATA0-DATA3差分对组内等长(这里设置的是0.1mm)

4、完成第三步设置后,进入PCB界面先连通四组差分走线如下,很明显一组差分不等长:

5、规则管理器下图位置选中几组差分对右键analyze

6、将其展开可以看到如下所示:

其中Tolerance表示我们设置的组内0.1mm长度误差。Actual表示实际走线的组内长度误差误差,Margin表示误差的剩余量Margin=Tolerance-Actual,其中DATA0两根差分线实际长度差为4.296mm,其Margin=0.1-4.296=-4.196mm;

7、进入“Tools->Quick Report-> Etch Length by Pin Pair Report”查看走线长度报告如下图:

其中DATA0_P-DATA0_N=13.5245-9.2285=4.296mm。其余DATA1、DATA2、DATA3,差分组由于对内走线长度相等故Actual=0mm,Margin=0.1mm。

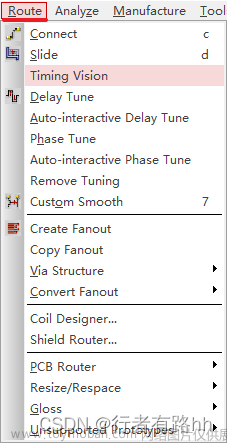

7、进行DATA0差分组内等长走线 选择Route->Delay Tune:

下图SPhase进度条红色表示在误差0.1mm以外,进度条绿色表示在0.1mm误差范围之内.需要调整进度条在绿色范围。

8、进入规则管理器查看DATA0Actual=0.0356mm,Margin=0.0644mm,满足误差要求

三、组间差分设置

1、进入"Constraint Manager->Electrical->Net->Relative Propagation Delay "中选中8根差分线创建Match Group:

2、Constraint Manager->Electrical->Net->Relative Propagation Delay 中Relative Dalay中Tolerance中下方的单位:此处设置为mm:并在下图MG1(8)右键Change

3、做出如下更改,设置四组差分对DATA0/1/2/3之间的等长为0.2mm:

4、此时点击Setup-> Constraint->Modes 选择Electrial中的Relative Propagation Delay将其状态由off更改为On。如此pcb的DRC才会检测此等长规则。

5、打开规则管理器在MG1(8)右键单击Analyze:

6、下图在Length中可以看到每条走线的长度系统会已一条最长的走线做为TARGET(目标值)DATA1_P其余七个走线都会向此目标值对齐,同样的Actual和Margin的含义与上面相同。

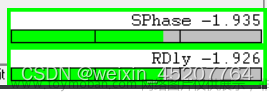

7、进行等长差分对组间等长走线,最长的DATA1差分对不需要动,调整其余三对。下图中由两个进度条SPhase(组内等长)和RDly(组间等长),同样的RDly红色进图条表示组间不满足0.2mm的等长误差,绿色进度条表示满足0.2mm的组间等长误差。

8、当SPhase(组内等长)和RDly(组间等长)进度条都为绿色,表示此差分对既满足组内等长0.1mm,又满足组间等长。

9、四组差分对等长如下所示:

10、规则管理器中查看等长规则,均满足等长要求。 文章来源:https://www.toymoban.com/news/detail-816085.html

文章来源:https://www.toymoban.com/news/detail-816085.html

总结

上述分别为差分组内等长和组间等长的设置操作方法,上文中使用的原理图和PCB材料只为了演示allego17.4的功能,无实际项目应用意义。文章来源地址https://www.toymoban.com/news/detail-816085.html

到了这里,关于Allgeo17.4差分对组内等长以及组间等长的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!