本专栏的目的是分享可以通过HDLBits仿真的Verilog代码 以提供参考 各位可同时参考我的代码和官方题解代码 或许会有所收益

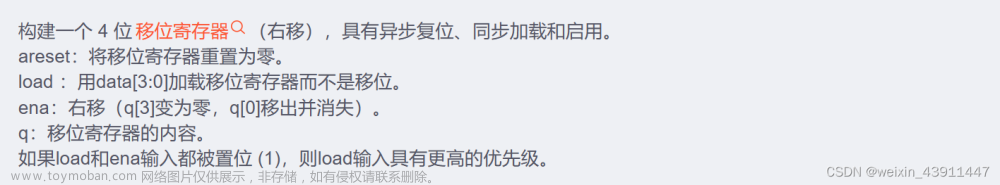

题目链接:Shift4 - HDLBits

module top_module(

input clk,

input areset, // async active-high reset to zero

input load,

input ena,

input [3:0] data,

output reg [3:0] q);

always @ (posedge clk or posedge areset) begin

if (areset) q <= 0 ;

else if (load) q <= data ;

else if (ena) q <= {1'b0, q[3:1]} ;

else q <= q ;

end

endmodule

题目链接:Rotate100 - HDLBits

module top_module(

input clk,

input load,

input [1:0] ena,

input [99:0] data,

output reg [99:0] q);

always @ (posedge clk) begin

if (load) q <= data ;

else

if (ena == 1) q <= {q[0], q[99:1]};

else if (ena == 2) q <= {q[98:0], q[99]};

else q <= q ;

end

endmodule

题目链接:Shift18 - HDLBits

module top_module(

input clk,

input load,

input ena,

input [1:0] amount,

input [63:0] data,

output reg [63:0] q);

always @ (posedge clk) begin

if (load) q <= data ;

else

if (ena) begin

case (amount)

0 : q <= {q[62:0], 1'b0} ;

1 : q <= {q[55:0], 8'b0} ;

2 : q <= {q[63], q[63:1]} ;

3 : q <= {q[63], {7{q[63]}}, q[63:8]} ;

endcase

end

else q <= q ;

end

endmodule

题目链接:Lfsr5 - HDLBits

module top_module(

input clk,

input reset, // Active-high synchronous reset to 5'h1

output [4:0] q

);

reg q4, q3, q2, q1, q0 ;

assign q = {q4, q3, q2, q1, q0} ;

always @ (posedge clk) begin

if (reset) q4 <= 0 ;

else q4 <= 0 ^ q0 ;

end

always @ (posedge clk) begin

if (reset) q3 <= 0 ;

else q3 <= q4 ;

end

always @ (posedge clk) begin

if (reset) q2 <= 0 ;

else q2 <= q3 ^ q0 ;

end

always @ (posedge clk) begin

if (reset) q1 <= 0 ;

else q1 <= q2 ;

end

always @ (posedge clk) begin

if (reset) q0 <= 1 ;

else q0 <= q1 ;

end

endmodule

题目链接:Mt2015 lfsr - HDLBits

module top_module (

input [2:0] SW, // R

input [1:0] KEY, // L and clk

output [2:0] LEDR); // Q

reg q0, q1, q2 ;

reg o0, o1, o2 ;

wire L, clk ;

wire t ;

assign L = KEY[1] ;

assign clk = KEY[0] ;

assign LEDR = {q2, q1, q0} ;

assign t = q1 ^ q2 ;

always @ (*) begin

if (L) o0 <= SW[0] ;

else o0 <= q2 ;

end

always @ (*) begin

if (L) o1 <= SW[1] ;

else o1 <= q0 ;

end

always @ (*) begin

if (L) o2 <= SW[2] ;

else o2 <= t ;

end

always @ (posedge clk) begin

q0 <= o0 ;

q1 <= o1 ;

q2 <= o2 ;

end

endmodule

题目链接:Lfsr32 - HDLBits

module top_module(

input clk,

input reset, // Active-high synchronous reset to 32'h1

output [31:0] q

);

reg [31:0] q_next;

always @(*) begin

q_next = q[31:1]; // Shift all the bits. This is incorrect for q_next[4] and q_next[2]

q_next[31] = q[0]; // Give q_next[4] and q_next[2] their correct assignments

q_next[21] = q[22] ^ q[0];

q_next[1] = q[2] ^ q[0];

q_next[0] = q[1] ^ q[0];

end

always @(posedge clk) begin

if (reset)

q <= 32'h1;

else

q <= q_next;

end

endmodule

题目链接:Exams/m2014 q4k - HDLBits

module top_module (

input clk,

input resetn, // synchronous reset

input in,

output out);

reg q0, q1, q2 ;

sub_module u0(clk, resetn, in, q0) ;

sub_module u1(clk, resetn, q0, q1) ;

sub_module u2(clk, resetn, q1, q2) ;

sub_module u3(clk, resetn, q2, out) ;

endmodule

module sub_module (

input clk,

input resetn,

input in,

output out

);

always @ (posedge clk) begin

if (!resetn) out <= 0 ;

else out <= in ;

end

endmodule

题目链接:Exams/2014 q4b - HDLBits文章来源:https://www.toymoban.com/news/detail-816253.html

module top_module (

input [3:0] SW,

input [3:0] KEY,

output [3:0] LEDR

); //

wire clk, E, L, w ;

assign {w, L, E, clk} = KEY ;

sub_module u0(clk, w, SW[3], E, L, LEDR[3]) ;

sub_module u1(clk, LEDR[3], SW[2], E, L, LEDR[2]) ;

sub_module u2(clk, LEDR[2], SW[1], E, L, LEDR[1]) ;

sub_module u3(clk, LEDR[1], SW[0], E, L, LEDR[0]) ;

endmodule

module sub_module (

input clk,

input w, R, E, L,

output Q

);

wire mux1_out, mux2_out ;

assign mux1_out = E ? w : Q ;

assign mux2_out = L ? R : mux1_out ;

always @(posedge clk) begin

Q <= mux2_out ;

end

endmodule

题目链接:Exams/ece241 2013 q12 - HDLBits文章来源地址https://www.toymoban.com/news/detail-816253.html

module top_module (

input clk,

input enable,

input S,

input A, B, C,

output Z );

wire [7:0] q ;

wire [2:0] sel ;

assign sel = {A, B, C} ;

sub_module u0(clk, enable, S, q[0]) ;

genvar i ;

generate

for (i = 1 ; i <= 7 ; i = i + 1) begin : x

sub_module ui(clk, enable, q[i-1], q[i]) ;

end

endgenerate

always @ (*) begin

case (sel)

0 : Z <= q[0] ;

1 : Z <= q[1] ;

2 : Z <= q[2] ;

3 : Z <= q[3] ;

4 : Z <= q[4] ;

5 : Z <= q[5] ;

6 : Z <= q[6] ;

7 : Z <= q[7] ;

endcase

end

endmodule

module sub_module (

input clk,

input enable,

input in,

output out

);

always @ (posedge clk) begin

if (enable) out <= in ;

else out <= out ;

end

endmodule

到了这里,关于「HDLBits题解」Shift Registers的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![Verilog刷题[hdlbits] :Module add](https://imgs.yssmx.com/Uploads/2024/02/739179-1.png)