目录

1.算法仿真效果

2.算法涉及理论知识概要

2.1 Hamming编码过程

2.2 Hamming解码与纠错

2.3 FPGA实现

3.Verilog核心程序

4.完整算法代码文件

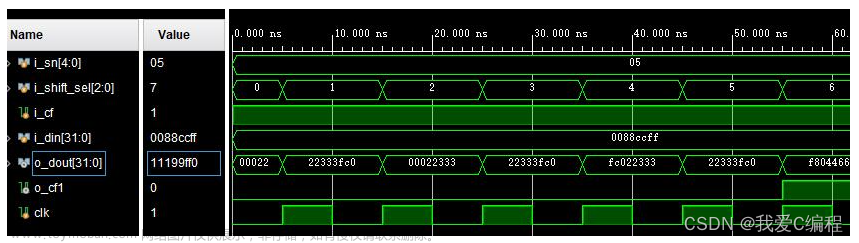

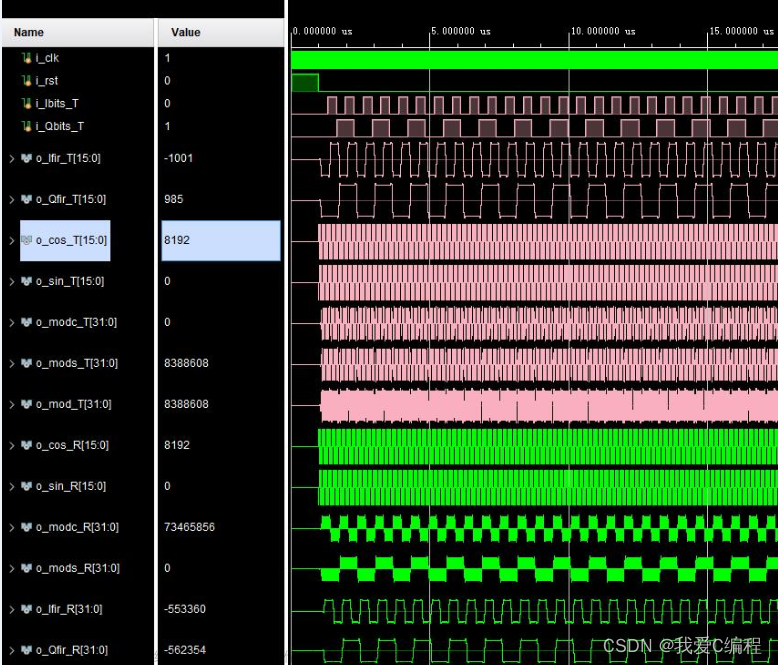

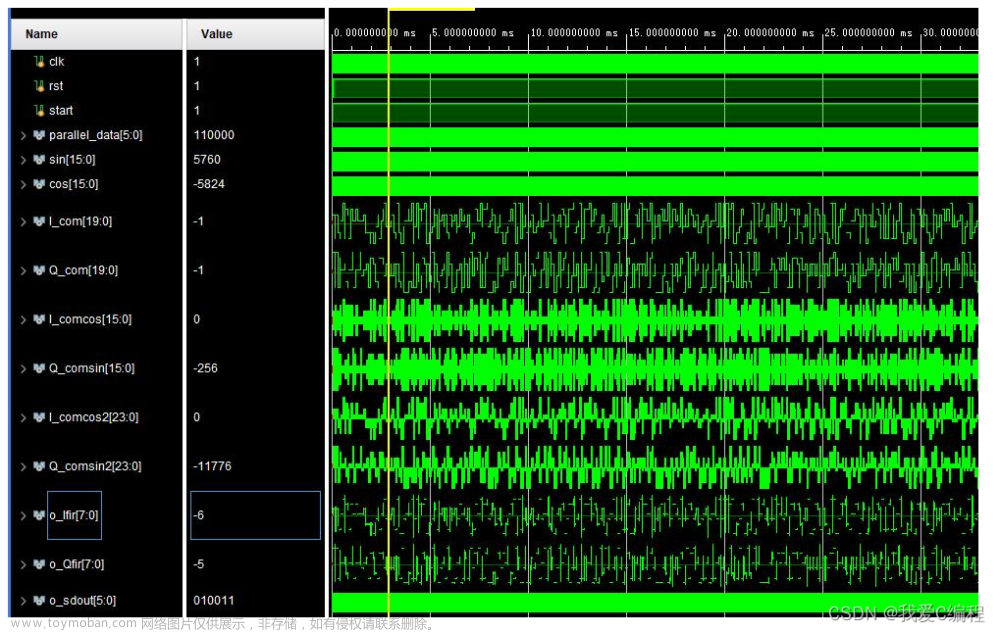

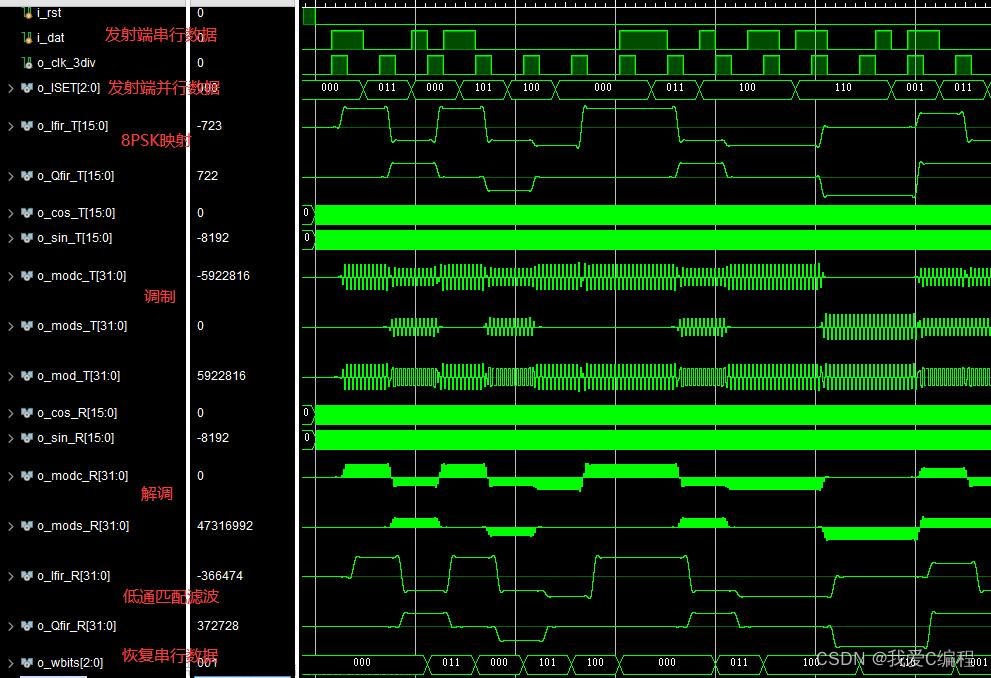

1.算法仿真效果

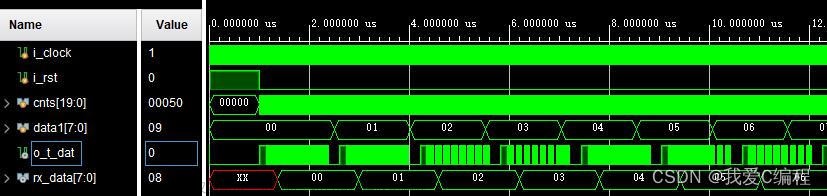

本系统进行了Vivado2019.2平台的开发,测试结果如下:

2.算法涉及理论知识概要

在现代数字通信和存储系统中,错误检测和纠正(Error Detection and Correction, EDC)机制是至关重要的。Hamming码,以其发明者Richard Hamming命名,是一种线性错误检测和纠正码,广泛应用于这些系统中。随着技术的发展,现场可编程门阵列(FPGA)已成为实现这些编码方案的高效平台。以下将详细介绍基于FPGA的Hamming汉明编译码的原理。

Hamming码是一种能够检测多个比特错误,同时纠正单个比特错误的线性纠错码。它通过增加冗余校验位来实现错误检测和纠正。

2.1 Hamming编码过程

假设我们要发送一个包含k个数据位的消息。为了使用Hamming码,我们需要增加一些校验位,使得总位数n满足(2^r \geq n + 1),其中r是校验位的数量,(n = k + r)。

-

确定校验位位置:校验位的位置是2的非负整数次幂,即1、2、4、8等位置。数据位则填充在剩余的位置。

-

构建校验方程:对于每一个校验位,我们需要构建一个校验方程。假设(p_i)是第i个校验位,那么与(p_i)对应的所有数据位和校验位的索引的二进制表示中,第i位都应该是1。

-

计算校验位值:通过异或运算计算每个校验位的值。将所有与特定校验位相关的位(包括其他校验位)进行异或运算,结果即为该校验位的值。

- 生成码字:将计算出的校验位插入到预定的位置,形成最终的码字。

2.2 Hamming解码与纠错

在接收端,通过重新计算校验和可以检测出错误。如果重新计算的校验和与接收到的校验和不匹配,说明发生了错误。Hamming码可以纠正单个比特的错误,其纠正过程如下:

- 计算校正子:校正子是接收到的码字中所有与特定校验位相关的位的异或结果。

- 错误定位和纠正:校正子可以看作是错误位置的二进制表示。如果校正子为0,说明没有错误;否则,校正子的二进制表示指出了错误发生的位置。通过翻转该位置的比特,可以纠正错误。

2.3 FPGA实现

在FPGA上实现Hamming编译码器主要涉及硬件描述语言(如VHDL或Verilog)的使用,以及数字逻辑设计。

编码器

编码器模块负责接收数据位,并计算出相应的校验位。它可以通过组合逻辑或有限状态机实现。组合逻辑实现通常更快,但可能消耗更多的资源。

解码器与纠错器

解码器模块负责接收完整的码字,并重新计算校验和。如果检测到错误,纠错器模块将定位并纠正错误。这两个模块也可以通过组合逻辑或有限状态机实现。

Hamming码是一种高效且广泛使用的错误检测和纠正机制。通过FPGA实现Hamming编译码器,可以显著提高数字通信和存储系统的可靠性和性能。FPGA的并行性和可配置性使得它能够以低成本和高效率实现这些复杂的编码方案。文章来源:https://www.toymoban.com/news/detail-816356.html

3.Verilog核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/01/06 03:26:47

// Design Name:

// Module Name: TEST

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TEST();

reg i_clk;

reg i_rst;

reg[7:0] i_din;

wire [11:0] o_data_enc;

wire [7:0] o_data_dec;

Hamming_enc Hamming_enc_U(

.i_clk (i_clk),

.i_rst (i_rst),

.i_din (i_din),

.o_dout(o_data_enc)

);

wire[11:0]o_data_err = o_data_enc ^ 11'b000_0001_0000;

Hamming_dec Hamming_dec_U(

.i_din (o_data_err),

.o_dout(o_data_dec)

);

initial

begin

i_clk = 1'b1;

i_rst = 1'b1;

i_din = 8'b0000_0000;

#100

i_rst = 1'b0;

end

always #5 i_clk = ~i_clk;

always #10 i_din = i_din + 8'd1;

endmodule

00_055m

4.完整算法代码文件

V文章来源地址https://www.toymoban.com/news/detail-816356.html

到了这里,关于m基于FPGA的Hamming汉明编译码verilog实现,包含testbench测试文件,不使用IP核的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!