实际工作中使用的是型号为TMS320C6678的DSP,并通过EMIF接口与FPGA通讯。

由于EMIF接口比较简单,本文以FPGA的角度作为EMIF接口的slave端进行设计。参考手册为KeyStone Architecture External Memory Interface (EMIF16) User Guide - May 2011

FPGA与DSP之间的EMIF接口调试

EMIF接口

DSP之外部设备连接接口之EMIF

DSP学习笔记----EMIF(外部存储器接口)

1. Overview

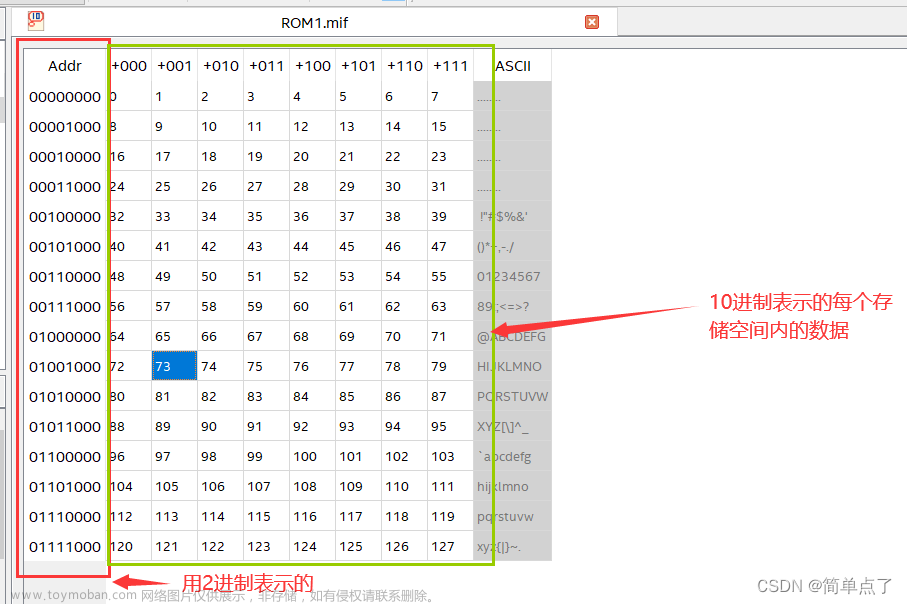

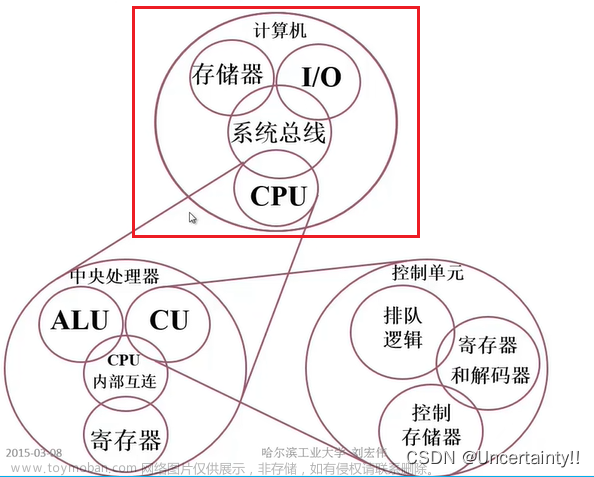

外部存储器接口(External Memory Interface, EMIF)主要用来同并行存储器连接,这些存储器包括SDRAM、SBSRAM、Flash、SRAM存储器等

还可以同外部并行设备进行连接,包括并行A/D、D/A转换器、具有异步并行接口的专用芯片,并可以通过EMIF同FPGA、CPLD等连接。

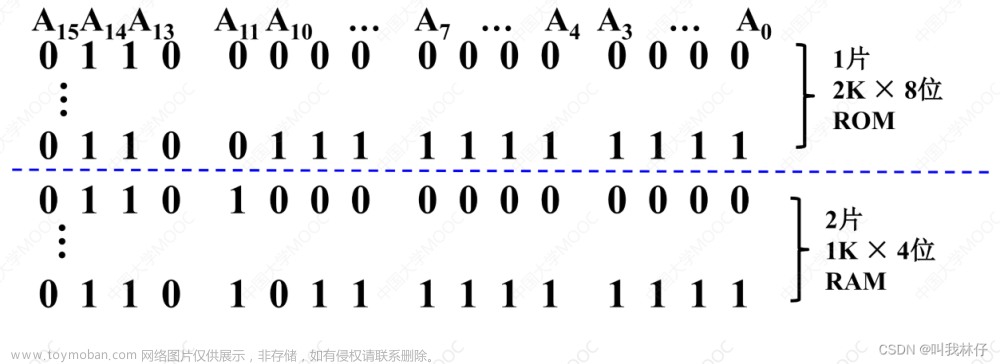

EMIF接口可根据不同的存储器类型使用不同的接口信号。对于FPGA而言,可看作是DSP的一种外部存储器,进行通信。

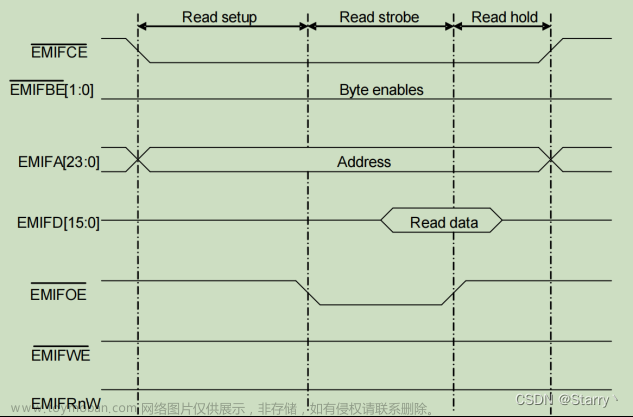

2. Timing Description

时序图如下,分为Setup、Strobe和Hold三个阶段。三个阶段的持续时间取决于Async 1 Config Register寄存器

2.1. Read Timing

读时序如下,EMIFD数据在HOLD阶段的第一个上升沿采样

2.2. Write Timing

3. EMIF Slave Design Spec

EMIF的Slave端的RTL逻辑设计。文章来源:https://www.toymoban.com/news/detail-816433.html

外部存储器接口(External Memory Interface, EMIF)RTL设计 - verilog文章来源地址https://www.toymoban.com/news/detail-816433.html

到了这里,关于外部存储器接口(External Memory Interface, EMIF)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[深入理解NAND Flash (原理篇)] Flash(闪存)存储器底层原理 | 闪存存储器重要参数](https://imgs.yssmx.com/Uploads/2024/02/735174-1.png)