讲完FPGA中的LUT6和FF后,接下来讲FPGA底层中进位链CARRY4,话不多说上干货,记重点,CARRY4本质用来实现FPGA运算中的加减法。

看完这篇文章,你能收获到:

1. 理解我们经常在FPGA使用的加法减法,在FPGA底层中是如何实现的?引出半加器、全加器的概念

2. 在第一步基础上,理解FPGA中CARRY4的结构及功能

一、半加器

举个例子,在二进制中,两个1bit数相加只有4种情况:

0+0=0(结果位)

0+1=1(结果位)

1+0=1(结果位)

1+1=10(进位+结果位)

答案非常明显:

结果位=两个输入数字的异或(^)。

进位=两各输入数字的相与(&)

假设两个加数为A+B,相加后当前位结果为S,产生进位用C表示,则

S=A^B

C=A&B

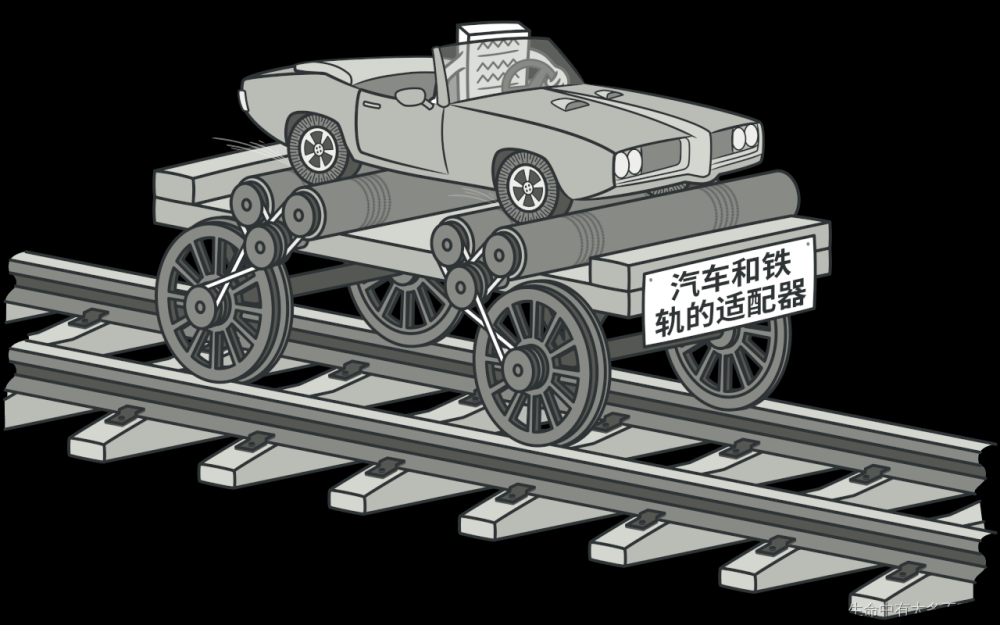

这个就是半加器的原理,半加器:两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。映射到电路就是一个异或门+一个与门。

半加器门电路结构

二、全加器

再举例子:两个2bit数相加(逻辑有点多,可以多看几次)

最右边为最低位

对于最低位:用上面所述的半加器可知,结果位S为0,进位C为1。

对于第二位:需要接受由低位产生的进位,才能计算当前结果位,结果位=1^1^1=1。

假设两个加数为A+B,相加后当前位结果为S,产生进位用Cout表示,输入的进位用CIN表示

对于第二位,我们得出:S2=A2^B2^CIN2=1^1^1=1。

Cout2=A2&B2 | A2^B2&CIN2(保证A2,B2,CIN2中有两个或两个以上的1)

对于第三位,我们得出:S3=A3^B3^CIN3=0^0^1=1。

Cout3=A3&B3 | A3^B3&CIN3 = 0。(产生进位的条件是A,B,CIN中有两个或两个以上的1)

由于Cout3=0,因此最终结果位{S3,S2,S1}=110。

在数电中,我们用全加器来实现上述中第二位,第三位的带进位的加法操作。

全加器的概念如下:

全加器:可以理解成半加器的升级版,除了半加器的功能外,再加上前一级传进来的进位信号。

假设两个加数为A+B,相加后当前位结果为S,是否产生进位用C表示,上一级进位输入用Cin表示

S=A^B^Cin

C=(A&B)|(Cin&(A^B))

那这里问题来了,是不是每次做多位加法计算时,最低位都要用半加器?

答案是否定的,因为从半加器和全加器区别就知道,全加器只是比半加器多了个来自低位进位的功能而已,我们只需要将全加器CIN置0,可将全加器当作半加器来用,再与全加器级联即可做成多位加法器。

那问题又来了,如果我是两个8bit数相加,两个16bit数相加呢?一个全加器够用吗?

这里需要通过级联全加器的方法,实现多bit数的相加。

三、进位链CARRY4

那FPGA内部,是不是也用全加器,实现加减法呢?我们看CARRY4结构(是不是很复杂,没关系,看我圈红部分)

CARRY4结构

红圈部分本质上理解成一个全加器,一个CARRY4由4个全加器组成。其中

CIN:上一级进位输入,当在最低位时。

CYINIT:置0表示加法,置1表示减法。

S0=A0^B0(两个加数做异或)。

O0=S0^CIN(全加器中的S)。

DI0=A或者B。

还有MUX逻辑,当S=0,输出位左侧输入,S=1,右侧输出。

再举个例子

两个7bit数相加

综合后原理图

我们得到如下结论(靠左CARRY4称为进位链1,靠右CARRY4称为进位链2):

一、进位链1的CO[3:0]连到进位链2的CI[3:0],两者级联产生更大位宽的进位链。(若相加减数位宽越大,级联CARRY4越多,一个CARRY4能处理4bit数的加减。)

二、我们看LUT2原语INIT为6可知道,LUT2作用就是做异或操作,因此,蓝线意思代表两个加数的低四位异或后连入进位链1的S[3:0],两个加数的高四位异或后连入进位链2的S[3:0]。

LUT2原语

三、进位链1 O[3:0]连到输出的低4位,进位链2的O[3:0]连到输出的高4位。文章来源:https://www.toymoban.com/news/detail-817574.html

这里注意下,进位链级联数越多,路径延迟就会越大,逻辑级数越高。所以在使用进位链时要综合考虑级联数与整个系统时钟的关系。特别在设计位宽较大计数器,最好选择用DSP替换。文章来源地址https://www.toymoban.com/news/detail-817574.html

到了这里,关于用大白话从底层理解FPGA——进位链CARRY4的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!