基于FPGA的数字频率计的设计与实现

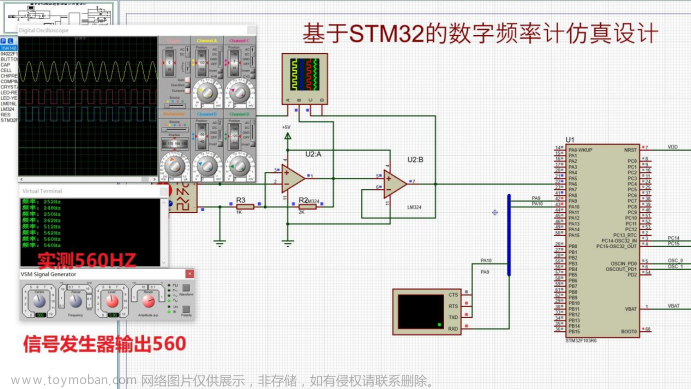

数字频率计是一种重要的电子测试仪器,它可以用来测量信号的频率和周期等参数,被广泛应用于科学研究、工程设计及生产制造等领域。本文将介绍一种基于FPGA的数字频率计的设计与实现方法,并给出相应的源代码。

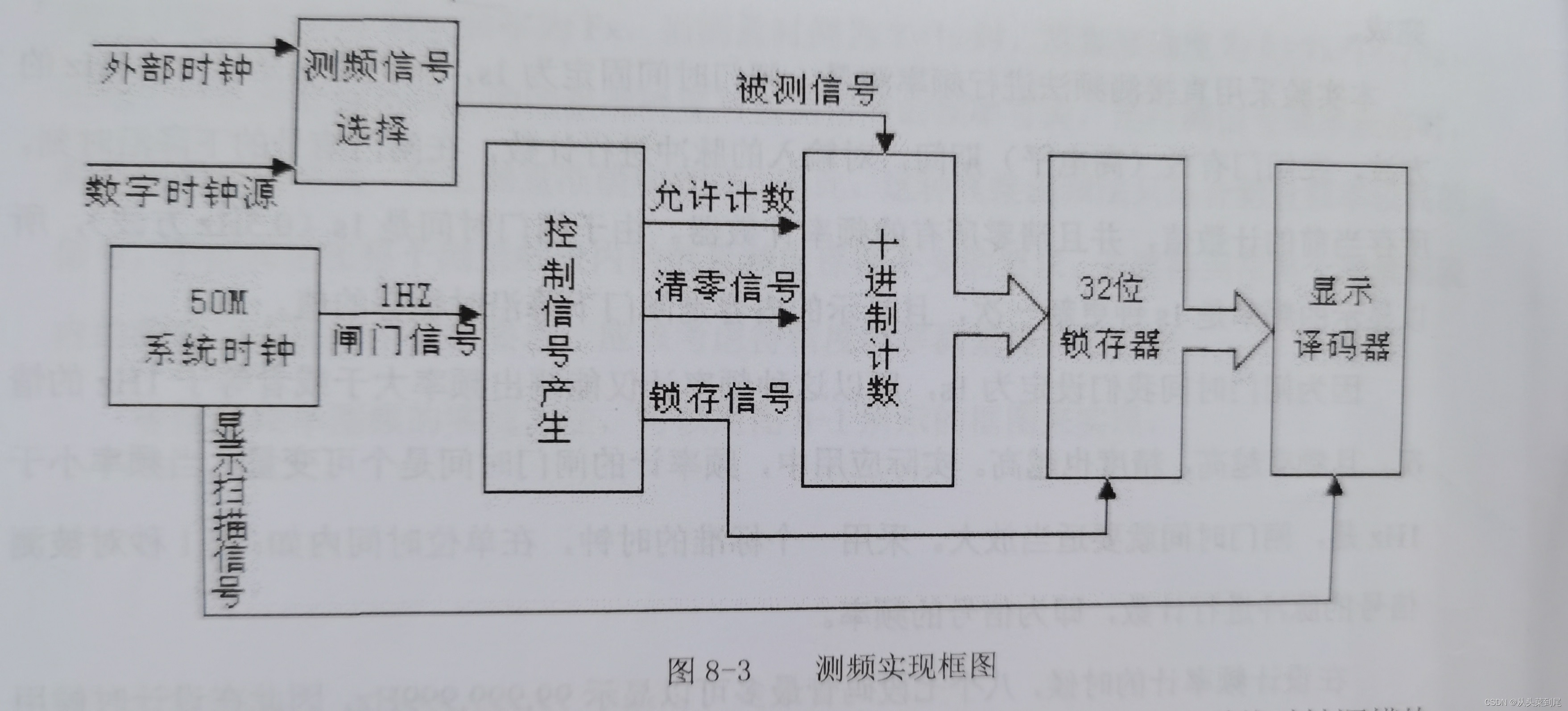

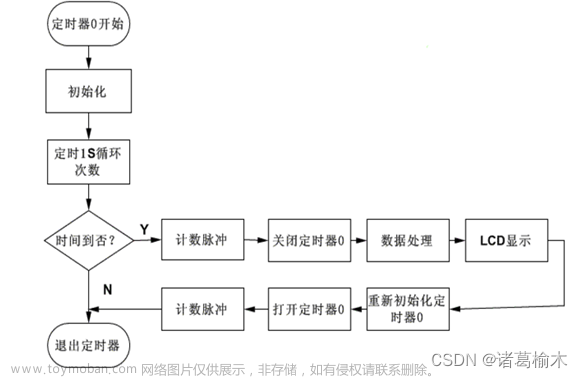

一、设计原理

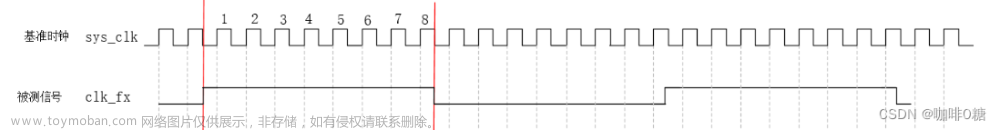

数字频率计的基本原理是利用计数器计算输入信号的脉冲个数,然后将计数值与时钟频率进行比较,得到输入信号的频率。为了提高精度,常常需要使用多级计数器进行加倍计数,最终得到较高的计数值,进而提高测量精度。

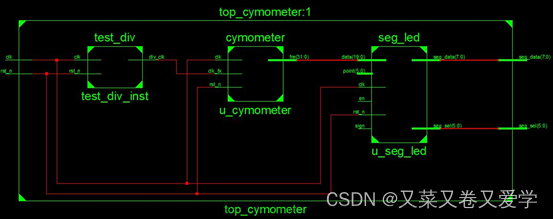

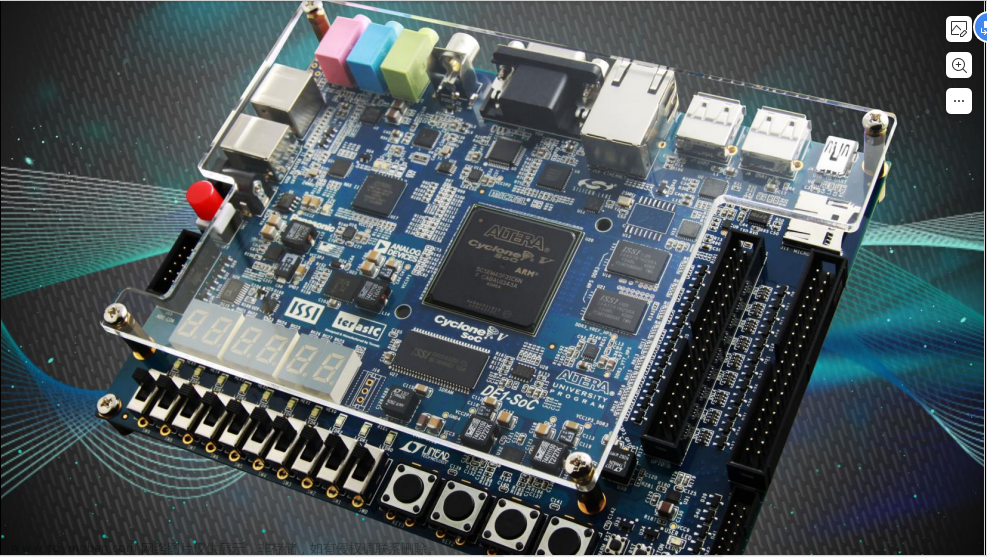

本设计采用VHDL语言实现,在FPGA芯片上构建一个由多级计数器组成的数字频率计,并通过LCD显示屏实时显示输入信号的频率。

二、电路结构与实现

本次设计所使用的FPGA芯片为EP4CE6E22C8N,其包含68个数字逻辑单元和59120个可编程逻辑单元,并具有良好的性能和稳定性,能够满足本设计的要求。

数字频率计的实现过程主要包括以下几个步骤:

- 信号输入模块

将输入信号通过一个接口模块输入到FPGA芯片中,该接口模块可以选择采用USB接口或者串口接口,本设计采用USB接口进行输入。

- 计数器模块

本次设计采用了三级计数器模块,包括16位计数器、24位计数器和32位计数器,分别用来进行1倍、256倍和65536倍的计数,最终得到较高的计数值,提高测量精度。文章来源:https://www.toymoban.com/news/detail-817622.html

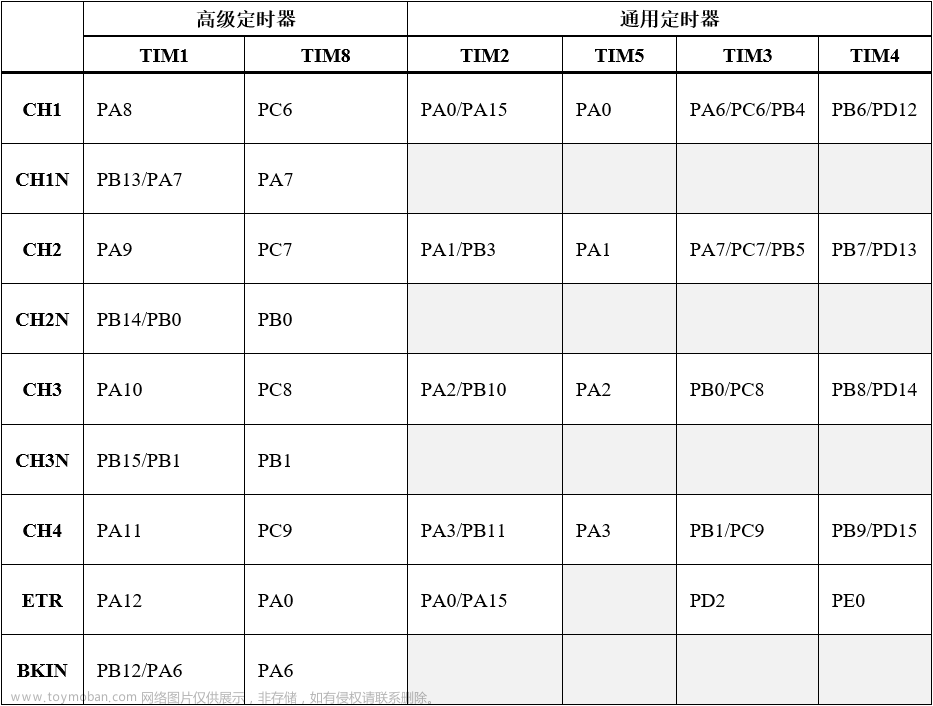

- 时钟模块

为了保证计数器模块的稳定工作,需要使用稳定的时钟信号,本次设计采用了50MHz的晶振作为时钟信号源,并使用PLL对其进行频率分频和倍频等操作,获得不同频率的时钟信号。文章来源地址https://www.toymoban.com/news/detail-817622.html

- 显示

到了这里,关于基于FPGA的数字频率计的设计与实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!