【FPGA中时序违例的处理方法】——详解

FPGA作为一种可编程逻辑器件,被广泛应用于数字电路设计和验证中。然而,在实际应用中,由于各种因素的干扰,可能会出现时序违例问题。时序违例是指由于时钟信号传输延迟等原因,导致数据信号无法按照预期的时序到达目标寄存器,从而引发错误。为了解决FPGA中的时序违例问题,我们可以采用以下方法:

-

消除时钟劣化:时钟信号经过长距离传输或布线潜在的“毒瘤”区域会出现劣化,导致时钟频率降低或者时钟抖动,进而导致FPGA的工作不稳定。为了消除时钟劣化,我们可以使用高质量的时钟信号源、减少时钟路径长度、减小电容负载等方法。

-

优化时序控制逻辑:时序控制逻辑包括时序校正、时钟分频、时序调节等,这些逻辑会对时序产生影响。因此,在设计时需要优化这些逻辑,使其更加合理和有效。

-

增加普通寄存器:增加普通寄存器是一种简单有效的方法,可以将数据更多地分配到寄存器中,减少时序路径长度。

-

采用流水线技术:流水线技术可以将大型模块分成若干个小模块,每个小模块只处理一部分数据,从而使整个系统的时钟频率提高,减少时序违例的发生。

-

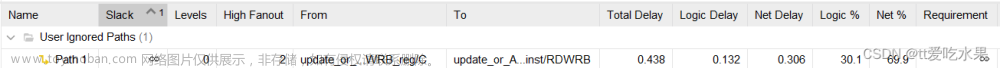

使用FPGA内置的时序优化工具:FPGA通常都会提供一些时序优化工具,例如Timing Analyzer、TimeQuest等,通过这些工具可以对设计进行时序分析和优化。文章来源:https://www.toymoban.com/news/detail-817794.html

总之,解决FPGA中的时序违例问题需要我们对FPGA的原理有深入的理解,同时也需要我们掌握一定的电路设计和FPGA编程技能。在实践中,我们可以根据具体情况采用以上不同的方法来解决时序违例问题。文章来源地址https://www.toymoban.com/news/detail-817794.html

到了这里,关于【FPGA中时序违例的处理方法】——详解的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!