静态时序分析原理

-

什么是STA

- 分析(计算)design是否满足timing约束的要求

- DFF(sequential cell—有clk的器件)setup/hold需求

- 复位/设置信号

- 信号脉冲宽度

- 门控时钟信号

- 计算design是否满足DRC的要求

- max_capacitance—节点电容

- max_transition—信号爬升时间

- max_fanout—负载能力有多少

- 分析(计算)design是否满足timing约束的要求

-

如上图所示,recovery的复位并不满足要求

-

为什么只定义了rest上升沿的时间需求,而并不讨论rest的下降沿的时间需求

- 因为rest其实可以看作一个单稳态过程,其本身并不会一直保持rest状态,而如果rest失效,这种状态反而可以持续性保持,不需要做出约束

- 因为rest其实可以看作一个单稳态过程,其本身并不会一直保持rest状态,而如果rest失效,这种状态反而可以持续性保持,不需要做出约束

-

pulse宽度太小导致电路开关反映不及时

-

clk其实也是为了保证功能的正确性,要设定建立和保持过程,保证不要有毛刺出现

-

时钟门控技术的解读

- Setup时间和Hold时间是时钟门控技术的两个关键参数。Setup时间是指在时钟信号沿上升之前,输入信号必须稳定的时间;而Hold时间是指在时钟信号沿上升后,输入信号必须保持稳定的时间。通过调整时钟门控技术中的这两个参数,可以确保电路在时钟信号采样之前稳定,并保持稳定直到时钟信号被采样,从而提高电路的可靠性和性能。

- Clock gating setup/hold是一种时钟门控技术,用于减少系统功耗和提高电路的性能。它的主要目的是确保数据在时钟信号边沿之前稳定,并保持稳定直到时钟信号被采样。在时钟门控技术中,时钟信号只在需要时才被传递到电路的特定部分。当时钟信号未传递到电路时,电路将进入低功耗模式,从而减少了功耗。时钟门控技术可以在保持电路的性能的同时,降低整个系统的功耗。

综合的基本流程介绍

- 根据RTL design和cell library,把RTL code映射到最基本的各类数字电路器件

- 根据STA timing constraint,尽量保证map后的gate level design满足timing constraint

- 尽量把design的面积功耗优化到最小

- 对DRC进行校正

- 尽量让gate level的布局布线最小

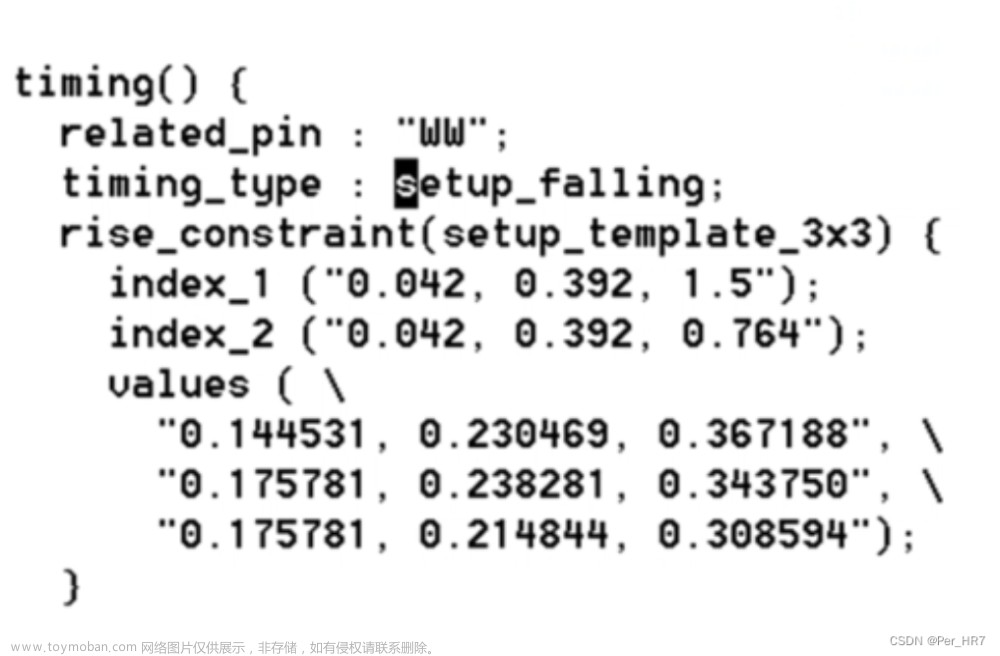

了解stander cell library

- 一般来说同种工艺库每种库都会提供slow/typical/fast三种cell(PVT)

- slow关注setup,fast关注hold

- 对于不同晶体管的导通电压也提供三种LVT/RVT/HVT(满足时钟频率和功耗之间的平衡关系)

- 为什么提供不同版本的library

- 为了满足更多的芯片功耗和速度的优化可能性

- 为什么要在做STA的同时进行DRC检查

- 因为stander cell library里面的timing数据是在一定{input_transition, output_loading}范围下仿真/测量得出的,超出此范围,timing数据就不准确了

- 因为stander cell library里面的timing数据是在一定{input_transition, output_loading}范围下仿真/测量得出的,超出此范围,timing数据就不准确了

clock相关的概念

- clock需要明确一点,clock由于受到工艺影响,存在不稳定的波动

- clock tree

- clk如果驱动多个DFF,存在一条clk输入到DFF端的clk存在不同的误差,通过clock tree可以实现对多个DFF设备进行同步时钟的提供

- clock skew

- 同一个时钟的同一个沿,到达不同DFF的时间差异

- 同一个时钟的同一个沿,到达不同DFF的时间差异

STA术语

- 对于STA分析中的哪些可以作为一个path的start or end呢

- start

- 输入的ports

- 时序器件的clock pins

- end

- 输出output ports

- 时序器件的data pins

- 时序器件的clock pins

- start

setup/hold check计算方法

- setup所定义的范围

- 对于前一个寄存器在clk0上升沿发出的数据,必须要在clk1上升沿被后一个寄存器看到

- 即在clk之内保证数据发送

- hold所定义的范围

- 对于前一个寄存器在clk0上升沿发出的数据,不能被后一个寄存器的clk0上升沿看到

- setup具体计算示意

- 思路

- 明确得到第一个寄存器到第二个寄存器之间的传输时间

- 明确clk0和clk1之间的时间

- 两者做出比较

- 可视化解读

- 思路

-

标注

- clk_latency表示clk前级输入的延迟

- clk_path_delay表示clk路径的延迟

- ck_to_q表示数据搬移的延迟

- logic_delay组合逻辑的延迟

- dff_setup在lib中根据参数查找的setup

- clk_uncertainty自定义可能的延迟

-

最终需要满足的条件

- data_arrival_time <= data_required time

- data_arrival_time <= data_required time

-

如何在setup不满足的情况下想办法进行调整

- 降低clk时钟频率

- ck_to_q和logic_delay可以通过PVT进行改变

-

hold check计算

- 注意是不能被后一个clk看到,因此,希望dataclk久一点更好

- 可视化解读

-

最终需要满足的条件

- data_arrival_time >= data_required time

- data_arrival_time >= data_required time

-

如何在hold不满足的情况下想办法进行调整

- ck_to_q和logic_delay可以通过PVT进行改变,进行变大

- 为什么不能通过clk频率改变进行解决?

- 因为本来就没有clk这一项

-

setup时钟沿

- 在end point时钟沿之前的第一个start point时钟沿

- 用两个时钟沿最近的地方做计算

- 之前:仅仅用waveform(工艺库中定义的上升下降时间)去比较,clock latency不考虑

- waveform其实就是人为理想的波形

-

hold时钟沿

- start point用setup check的时钟沿

- end pointer用setup check之前的一个时钟沿

-

实例分析

文章来源:https://www.toymoban.com/news/detail-818168.html

文章来源:https://www.toymoban.com/news/detail-818168.html -

总结原则文章来源地址https://www.toymoban.com/news/detail-818168.html

- setup找到最近的两个上升沿的间距时长

- hold在setup基础上,将后一个上升沿向前推一个周期,再进行计算

- 注意

- 这里的分析并没有加入latency,等于是在去掉latency之后进行分析

- 什么是latency—时钟的延迟信息包含clock tree delay

常用时序约束

- creat_clock

- creat_clock -name Name -period T -waveform {0, T*o.5} [get_port clk]

- 一般setup和hold要成对定义,保证基本上有一个clk的差异

- creat_clock -name Name -period T -waveform {0, T*o.5} [get_port clk]

到了这里,关于静态时序分析(STA)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!