基于PCIe(Peripheral Component Interconnect Express)总线连接CPU、独立GPU和NVMe SSD的系统架构。

在该架构中,PCIe Swicth支持GPU与SSD之间快速的点对点直接内存访问(peer-to-peer, p2p DMA)。通常情况下,外设设备间的数据传输需要通过CPU内存缓冲区作为中转站。例如,在将数据从SSD复制到GPU的过程中,CPU会先要求SSD将数据传入其本地缓冲区,再命令GPU将这些数据复制到自身的GPU内存缓冲区。

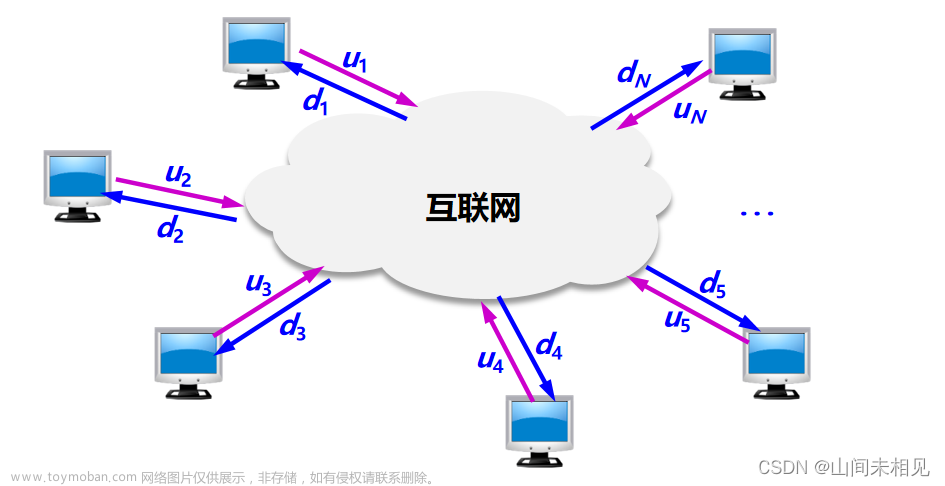

然而,通过启用p2p DMA功能,SSD可以直接将数据读写至或从GPU内存进行传输,无需经过CPU处理。这种机制如图所示,显著提升了数据传输效率。

在该系统中, PCIe BAR(Base Address Register): PCIe设备通过BAR将其控制寄存器和/或内部内存块暴露在总线上,以便由其他PCIe设备访问。BAR保存了设备寄存器和内存可以被访问的总线地址区域。

通过BAR暴露内部内存:设备可以选择通过BAR公开其内部内存,使得CPU或其他PCIe设备能够直接访问这部分内存。NVIDIA和AMD的GPU均支持此功能,分别通过GPUDirect RDMA和DirectGMA技术实现。

为了实现p2p DMA,GPU会在BAR上暴露一部分本地内存段。然后,SSD的DMA控制器就可以根据GPU BAR地址直接进行数据传输,而无需关心源或目标缓冲区的实际物理位置。因此,p2p DMA并不需要SSD提供特殊支持。文章来源:https://www.toymoban.com/news/detail-818562.html

映射GPU内存到进程地址空间:GPU通过在其PCIe总线上的设备BAR上暴露部分GPU内存,使其可供CPU访问。为了允许用户态应用程序访问这部分GPU内存,NVIDIA提供了gdrcopy工具,AMD则通过OpenCL扩展实现了将GPU内存映射到进程地址空间的功能。文章来源地址https://www.toymoban.com/news/detail-818562.html

到了这里,关于GPU与SSD间的P2P DMA访问机制的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!