一. 简介

哈喽,大家好,好久没有给大家写FPGA技术的文章,是不是已经忘记我是做FPGA的啦,O(∩_∩)O哈哈~。

这里将会给大家分享我学习到的第一个高速接口Aurora8B10B,有点复杂,但不是特别复杂,对于第一次接触到高速接口的朋友来说,难点在于细节的把控上,由于资料并不是那么多(也挺多的 ̄□ ̄||),很多新的概念,结构和名词,是第一次接触到,不能够很好的吸收,加上网上的教程不全面,很难有一篇文章对它的各个详细作全面的介绍,而且仿真都是基于官方例程来的,直接忽视了里面的细节。

本篇文章的目的就是教会大家Aurora8B10B 和 Xilinx提供的IP,并且基于自己的工程来进行仿真,不copy官方例程中的任何文件。

二. 从IP配置界面学习Aurora

本次使用的VIvado版本为2022.2,IP的版本为11.1,不同的版本可能会有细微的区别,打开IP的配置界面后,有三个界面需要我们进行配置,下面就依次来介绍这三个界面。

1. Core Options

主要配置物理层 和 链路层 这两个模块,其它模块在在初学的时候,可以忽略。

-

物理层:

- Line Width(Bytes): 线的位宽,也就是你发送每笔数据的位宽

- Line Rate(Gbps) : 线速率

- GT Refclk(Mhz): GT收发器的参考时钟,它有一个点需要注意,等下会提到

- INIT clk(Mhz):对Aurora核进行初始化,一般为50M就可以了

- DRP Clk(Mhz): 动态配置时钟,在例化IP后,可以通过DRP接口来对其进行配置,一般例化IP后,其属性就不会动了,所以用的不是那么多,和INIT clk保持一致就可以了。

这里需要注意的一点就是GT Refclk这个信号,由于Aurora这个IP是在GT收发器的基础上再次封装了相关的东西,所以对GT收发器不是很了解的话,有些信号使用细节上会存在问题。通过下图可以知道这个信号需要经过一个IBUFDS_GTE2来进行输入,没有注意的话,可能就会有意想不到的问题。

-

链路层

- Dataflow Mode: 配置模式,只发,只收,同时收和发

- Interface: 可以理解为用户数据是一帧一帧来的,还是以数据流的形式来的,接口上有无tkeep和tlask信号的区别

- Flow Control: 流控制,可以选择两大类UFC和NFC,或者无,UFC就在数据发送的过程中,需要发送一些紧急的数据过去,通过UFC接口就可以将紧急数据发送出去,NFC在同时收和发的模式下才可以使用,发送方发送的过快,而接收方接收的比较慢的话,就需要通过NFC接口告诉发送方发送慢一点。两者在用户发送信号的表现均为将s_axi_tx_tready信号拉低。

- Back Channel: 在只发或只收的模式下可以选择,同时收和发的模式下只能为Sidebands,这里没有进行详细的研究。

这一页的配置和选项的理解上应该就没有什么问题了。

2. GT Selections

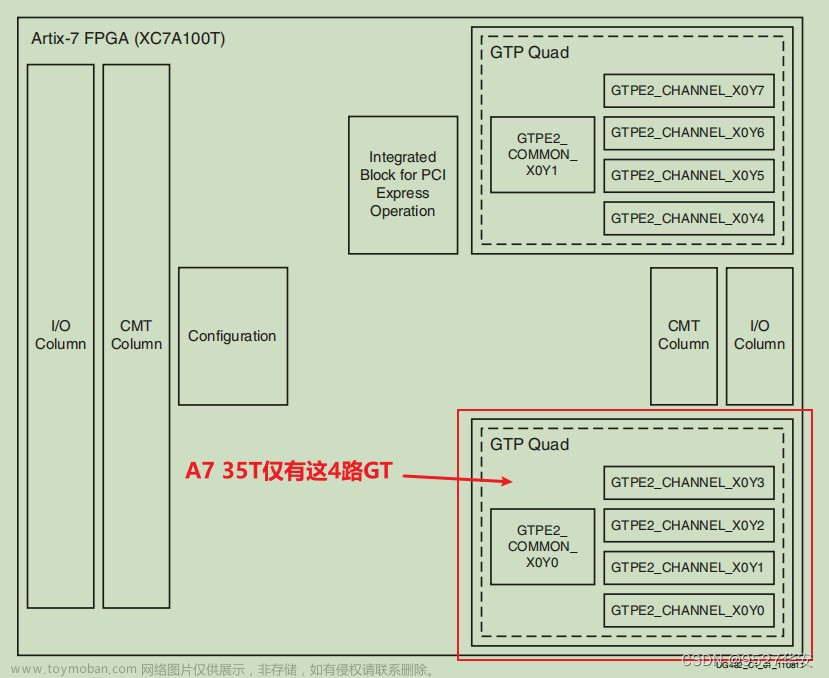

这里配置比较简单,主要是三个信息: 线数选择.GT收发器选择 和GT参考时钟选择。这里芯片我选择的是A7-100T,只有一个GT收发器,所以只需要选择Lanes数和Lanes与GT收发器通道的对应关系即可,参考时钟2是选择不了了,换到K7也是如此。

3. Shared Logic

这个界面就两个选项,共享逻辑是否包含在IP里面,这部分设计的知识也是GT收发器里面的,如果选择的是第一个选项包含在核里面,在生成IP的时候,会自动将GTPE2_COMMON这个原语包含在模块内,并且IP top模块会将其输出的gt时钟和其他相关信号在端口输出。如果选择的是第二个选项不包含在核里面,在生成IP的时候,就不会包含这个原语,那么gt相关的信号就需要外部进行输入。选择的时候可以观察一下IP端口信号的变动。

关于共享逻辑可以看下这幅图,共享逻辑的主要功能是将GTREFCLK0时钟通过QPLL后,生成QPLLCLK (QPLLOUTCLK)和QPLLREFCLK这两个时钟给GT收发器的Channel使用。

当然这里有点需要注意一下: GTP是没有QPLL和CPLL的,只有PLL0和PLL1,由于使用的是A7芯片,只有GTP,所以这里的细节需要注意一下。另外共享逻辑还可以选择外部输入的参考时钟,但在IP配置的只能选择GTREFCLK0。

为什么要叫它共享逻辑呢?怎样共享的呢?A7只有一个GT收发器,体现不了这一点。如果这里有两个GT收发器,第一个选择的是包含在核内,第二个选择的是不包含在核内,那么就可以向下面这样连接起来了,右边的Aurora里面的GT收发器使用的是左边的,而不是它自己的。

到这里,IP的配置界面以及相关的细节就给大家讲解清楚,有不对的地方,可以给我留言进行批评指正。

三.小结

本来想一篇文章写完的,但是太难了,太费时间了o(╥﹏╥)o,所以就到此结束啦。

本篇文章主要是通过Aurora8b10b IP创建界面,教大家如何进行配置,以及配置选项中涉及到的疑难点。文章来源:https://www.toymoban.com/news/detail-819147.html

下篇文章,以及下下篇中,将带领大家了解Aurora8b10b 在GT的基础上做了那些事情 和 仿真。

欢迎关注公众号 FPGA之旅(下方公众号)。

qq交流群: 649098696文章来源地址https://www.toymoban.com/news/detail-819147.html

到了这里,关于Aurora8B10B(一) 从IP配置界面学习Aurora的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!