0 工具准备

1.野火 stm32f407霸天虎开发板

2.LAN8720数据手册

3.STM32F4xx中文参考手册

1 以太网外设(ETH)

1.1 以太网外设(ETH)简介

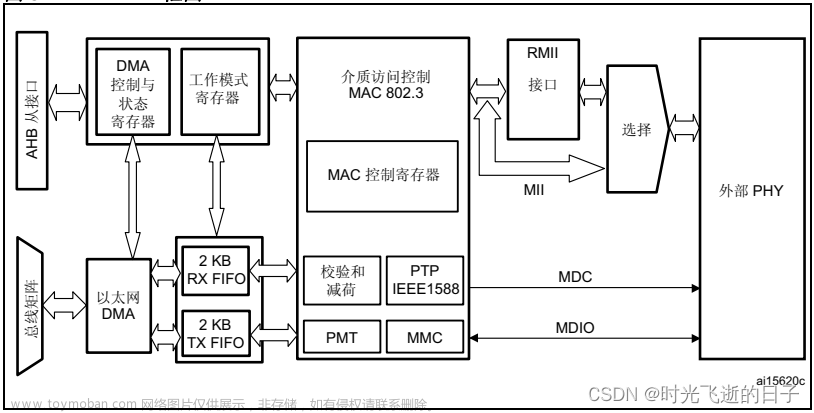

STM32F4系列MCU内部集成了一个以太网外设(ETH),可以通过介质独立接口(MII)或简化介质独立接口(RMII)和外部PHY(如LAN8720)相连实现MCU的联网功能。

STM32F4系列的以太网外设(ETH)框图如下:

1.2 MII、RMII、SMI接口介绍

以太网外设框图中包含了MII、RMII、SMI三种接口,它们的详细介绍如下:

1.2.1 介质独立接口:MII

介质独立接口 (MII) 定义了 10 Mbit/s 和 100 Mbit/s 的数据传输速率下 MAC 子层与 PHY 之间的互连。

MII_TX_CLK:连续时钟信号(由PHY提供)。该信号提供进行TX数据传输时的参考时序。标称频率为:速率为10Mbit/s时为2.5MHz;速率为100Mbit/s时为25MHz。

MII_RX_CLK:连续时钟信号(由PHY提供)。该信号提供进行RX数据传输时的参考时序。标称频率为:速率为10Mbit/s时为2.5MHz;速率为100Mbit/s时为25MHz。

MII_TX_EN:发送使能信号。该信号表示MAC当前正针对MII发送半字节。该信号必须与报头的前半字节进行同步(MII_TX_CLK),并在所有待发送的半字节均发送到MII

时必须保持同步。

MII_TXD[3:0]:数据发送信号。该信号是4个一组的数据信号,由MAC子层同步驱动,在MII_TX_EN信号有效时才为有效信号(有效数据)。MII_TXD[0]为最低有效位,MII_TXD[3]为最高有效位。禁止MII_TX_EN时,发送数据不会对PHY产生任何影响。

MII_CRS:载波侦听信号。当发送或接收介质处于非空闲状态时,由PHY使能该信号。发送和接收介质均处于空闲状态时,由PHY禁止该信号。PHY必须确保MII_CS信号在冲突条件下保持有效状态。该信号无需与TX和RX时钟保持同步。在全双工模式下,该信号没意义。

MII_COL:冲突检测信号。检测到介质上存在冲突后,PHY必须立即使能冲突检测信号,并且只要存在冲突条件,冲突检测信号必须保持有效状态。该信号无需与TX和RX时钟保持同步。在全双工模式下,该信号没意义。

MII_RXD[3:0]:数据接收信号。该信号是4个一组的数据信号,由PHY同步驱动,在MII_RX_DV信号有效时才为有效信号(有效数据)。MII_RXD[0]为最低有效位,MII_RXD[3]为最高有效位。当MII_RX_DV禁止、MII_RX_ER使能时,特定的MII_RXD[3:0]值用于传输来自PHY的特定信息(请参见表164)。

MII_RX_DV:接收数据有效信号。该信号表示PHY当前正针对MII接收已恢复并解码的半字节。该信号必须与恢复帧的头半字节进行同步(MII_RX_CLK),并且一直保持同

步到恢复帧的最后半字节。该信号必须在最后半字节随后的第一个时钟周期之前禁止。为了正确地接收帧,MII_RX_DV信号必须在时间范围上涵盖要接收的帧,其开始时间不得迟于SFD字段出现的时间。

MII_RX_ER:接收错误信号。该信号必须保持一个或多个周期(MII_RX_CLK),从而向MAC子层指示在帧的某处检测到错误。

1.2.2 精简介质独立接口:RMII

精简介质独立接口 (RMII) 规范降低了 10/100 Mbit/s 下微控制器以太网外设与外部 PHY 间的引脚数。根据 IEEE 802.3u 标准,MII 包括 16 个数据和控制信号的引脚。RMII 规范将引脚数减少为 7 个(引脚数减少 62.5%)。

RMII_TX_EN:发送使能信号。

RMII_TXD[1:0]:数据发送信号。该信号是2个一组的数据信号,由MAC子层同步驱动。

RMII_CRS:载波侦听信号。当发送或接收介质处于非空闲状态时,由PHY使能该信号。

RMII_RXD[1:0]:数据接收信号。该信号是2个一组的数据信号,由PHY同步驱动。

RMII_REF_CLK:由外部时钟源提供50MHz参考时钟,提供给 MAC 和外部以太网 PHY时钟必须是同一个,一般都是由PHY的PLL倍频到50MHz作为REF_CLK。

1.2.3 站管理接口:SMI

站管理接口 (SMI) 允许应用程序通过 2 线时钟和数据线访问任意 PHY 寄存器。该接口支持访问多达 32 个 PHY。

应用程序可以从 32 个 PHY 中选择一个 PHY,然后从任意 PHY 包含的 32 个寄存器中选择一个寄存器,发送控制数据或接收状态信息。任意给定时间内只能对一个 PHY 中的一个寄存器进行寻址。

MDC:周期性时钟,提供以最大频率 2.5 MHz 传输数据时的参考时序。MDC 的最短高电平时间和最短低电平时间必须均为 160 ns。MDC 的最小周期必须为 400 ns。在空闲状态下,SMI 管理接口将 MDC 时钟信号驱动为低电平。

MDIO:数据输入/输出比特流,用于通过 MDC 时钟信号向/从 PHY 设备同步传输状态信息。文章来源:https://www.toymoban.com/news/detail-819297.html

2 PHY(LAN8720)

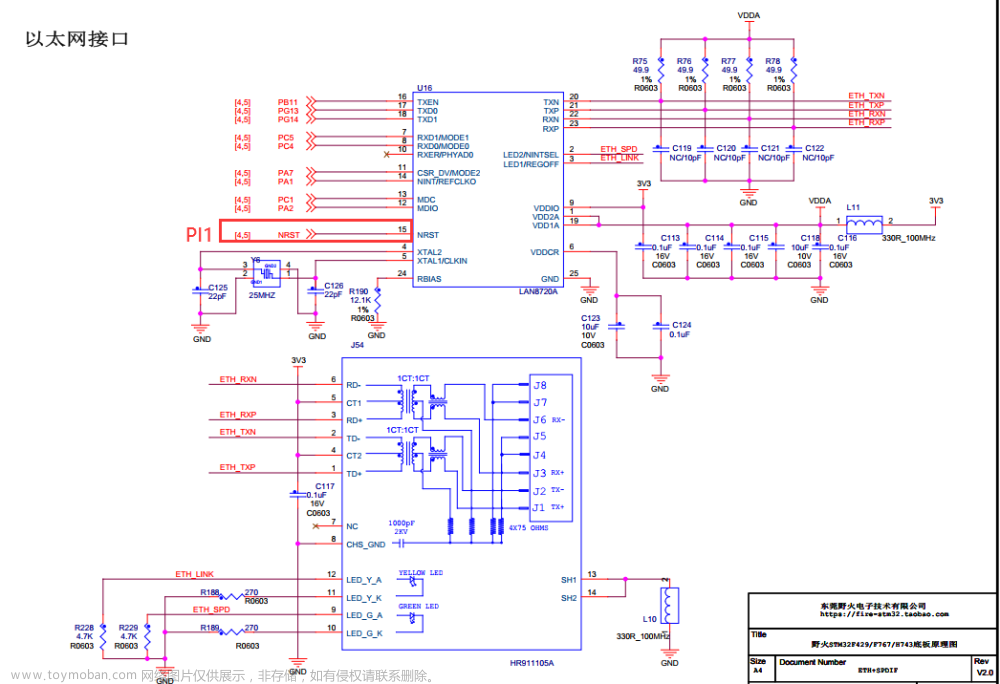

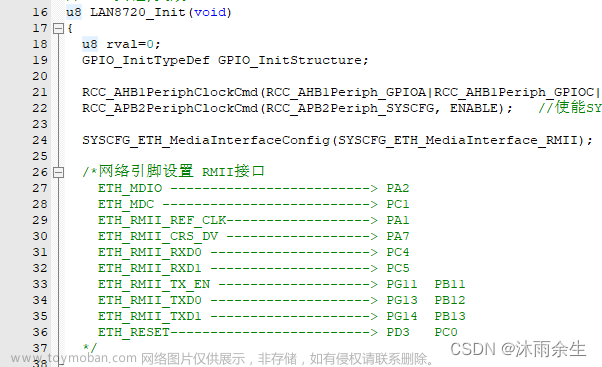

LAN8720A/LAN8720Ai是一款低功耗的10BASE-T/100BASE-TX(10Mbps/100Mbps)以太网物理层收发器。LAN8720仅支持RMII接口,系统框图如下:

LAN8720详细内部框图如下: LAN8720的部分引脚在上电时作为硬件配置引脚,例如PHYAD0和RXER等,后面硬件设计部分再详细介绍。文章来源地址https://www.toymoban.com/news/detail-819297.html

LAN8720的部分引脚在上电时作为硬件配置引脚,例如PHYAD0和RXER等,后面硬件设计部分再详细介绍。文章来源地址https://www.toymoban.com/news/detail-819297.html

到了这里,关于STM32的以太网外设+PHY(LAN8720)使用详解(1):ETH和PHY介绍的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!