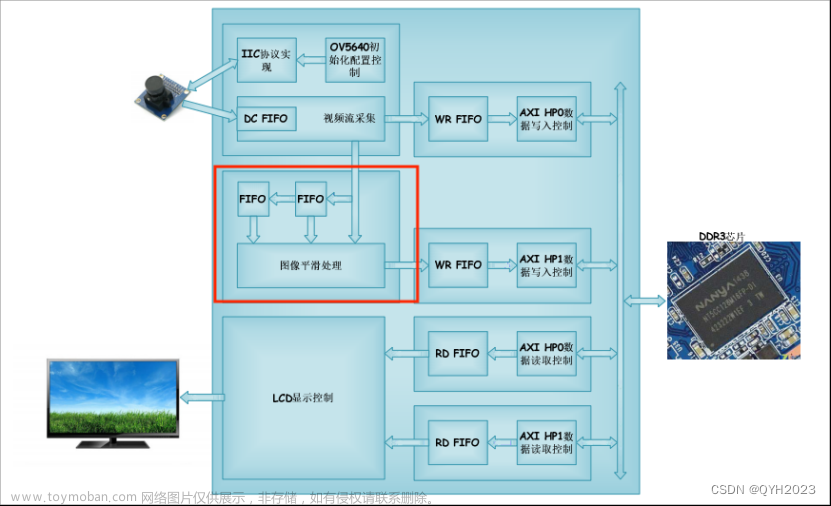

一,功能框图

ov5640摄像头视频通过ddr3缓存后,最后使用hdmi接口进行输出显示

二,摄像头硬件说明

2.1,像头硬件管脚

如下图所示,一共18个管脚

2.2,摄像头电源初始化时序

因这个ov5640摄像头是买的老摄像头,所以需要对Reset和PWDN的电源上电进行控制,控制时序如下图所示。

2.3,电源初始化程序

其中cmos_pwdn和cmos_rst_n为电源初始化管脚,初始化完成后,power_done会输出高电平

2.3,摄像头硬件实物

开发板摄像头硬件连接 三,摄像头初始化配置

三,摄像头初始化配置

摄像头初始化配置如下图所示,这里将摄像头的分辨率设置为720p输出显示,注意这里摄像头初始化配置是等摄像头电源配置完成后开始摄像头初始化配置,只有当power_done拉高后开始初始化配置。

摄像头720p配置文件

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/12/17 16:03:26

// Design Name:

// Module Name: lut_ov5640_rgb565_1280_720

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module lut_ov5640_rgb565_1280_720(

input[9:0] lut_index, //Look-up table address

output reg[31:0] lut_data //Device address (8bit I2C address), register address, register data

);

always@(*)

begin

case(lut_index)

10'd0: lut_data <= {8'h78 , 24'h310311};

10'd1: lut_data <= {8'h78 , 24'h300882};

10'd2: lut_data <= {8'h78 , 24'h300842};

10'd3: lut_data <= {8'h78 , 24'h310303};

10'd4: lut_data <= {8'h78 , 24'h3017ff};

10'd5: lut_data <= {8'h78 , 24'h3018ff};

10'd6: lut_data <= {8'h78 , 24'h30341A};

10'd7: lut_data <= {8'h78 , 24'h303713};

10'd8: lut_data <= {8'h78 , 24'h310801};

10'd9: lut_data <= {8'h78 , 24'h363036};

10'd10: lut_data <= {8'h78 , 24'h36310e};

10'd11: lut_data <= {8'h78 , 24'h3632e2};

10'd12: lut_data <= {8'h78 , 24'h363312};

10'd13: lut_data <= {8'h78 , 24'h3621e0};

10'd14: lut_data <= {8'h78 , 24'h3704a0};

10'd15: lut_data <= {8'h78 , 24'h37035a};

10'd16: lut_data <= {8'h78 , 24'h371578};

10'd17: lut_data <= {8'h78 , 24'h371701};

10'd18: lut_data <= {8'h78 , 24'h370b60};

10'd19: lut_data <= {8'h78 , 24'h37051a};

10'd20: lut_data <= {8'h78 , 24'h390502};

10'd21: lut_data <= {8'h78 , 24'h390610};

10'd22: lut_data <= {8'h78 , 24'h39010a};

10'd23: lut_data <= {8'h78 , 24'h373112};

10'd24: lut_data <= {8'h78 , 24'h360008};

10'd25: lut_data <= {8'h78 , 24'h360133};

10'd26: lut_data <= {8'h78 , 24'h302d60};

10'd27: lut_data <= {8'h78 , 24'h362052};

10'd28: lut_data <= {8'h78 , 24'h371b20};

10'd29: lut_data <= {8'h78 , 24'h471c50};

10'd30: lut_data <= {8'h78 , 24'h3a1343};

10'd31: lut_data <= {8'h78 , 24'h3a1800};

10'd32: lut_data <= {8'h78 , 24'h3a19f8};

10'd33: lut_data <= {8'h78 , 24'h363513};

10'd34: lut_data <= {8'h78 , 24'h363603};

10'd35: lut_data <= {8'h78 , 24'h363440};

10'd36: lut_data <= {8'h78 , 24'h362201};

10'd37: lut_data <= {8'h78 , 24'h3c0134};

10'd38: lut_data <= {8'h78 , 24'h3c0428};

10'd39: lut_data <= {8'h78 , 24'h3c0598};

10'd40: lut_data <= {8'h78 , 24'h3c0600};

10'd41: lut_data <= {8'h78 , 24'h3c0708};

10'd42: lut_data <= {8'h78 , 24'h3c0800};

10'd43: lut_data <= {8'h78 , 24'h3c091c};

10'd44: lut_data <= {8'h78 , 24'h3c0a9c};

10'd45: lut_data <= {8'h78 , 24'h3c0b40};

10'd46: lut_data <= {8'h78 , 24'h381000};

10'd47: lut_data <= {8'h78 , 24'h381110};

10'd48: lut_data <= {8'h78 , 24'h381200};

10'd49: lut_data <= {8'h78 , 24'h370864};

10'd50: lut_data <= {8'h78 , 24'h400102};

10'd51: lut_data <= {8'h78 , 24'h40051a};

10'd52: lut_data <= {8'h78 , 24'h300000};

10'd53: lut_data <= {8'h78 , 24'h3004ff};

10'd54: lut_data <= {8'h78 , 24'h300e58};

10'd55: lut_data <= {8'h78 , 24'h302e00};

10'd56: lut_data <= {8'h78 , 24'h430060};

10'd57: lut_data <= {8'h78 , 24'h501f01};

10'd58: lut_data <= {8'h78 , 24'h440e00};

10'd59: lut_data <= {8'h78 , 24'h5000a7};

10'd60: lut_data <= {8'h78 , 24'h3a0f30};

10'd61: lut_data <= {8'h78 , 24'h3a1028};

10'd62: lut_data <= {8'h78 , 24'h3a1b30};

10'd63: lut_data <= {8'h78 , 24'h3a1e26};

10'd64: lut_data <= {8'h78 , 24'h3a1160};

10'd65: lut_data <= {8'h78 , 24'h3a1f14};

10'd66: lut_data <= {8'h78 , 24'h580023};

10'd67: lut_data <= {8'h78 , 24'h580114};

10'd68: lut_data <= {8'h78 , 24'h58020f};

10'd69: lut_data <= {8'h78 , 24'h58030f};

10'd70: lut_data <= {8'h78 , 24'h580412};

10'd71: lut_data <= {8'h78 , 24'h580526};

10'd72: lut_data <= {8'h78 , 24'h58060c};

10'd73: lut_data <= {8'h78 , 24'h580708};

10'd74: lut_data <= {8'h78 , 24'h580805};

10'd75: lut_data <= {8'h78 , 24'h580905};

10'd76: lut_data <= {8'h78 , 24'h580a08};

10'd77: lut_data <= {8'h78 , 24'h580b0d};

10'd78: lut_data <= {8'h78 , 24'h580c08};

10'd79: lut_data <= {8'h78 , 24'h580d03};

10'd80: lut_data <= {8'h78 , 24'h580e00};

10'd81: lut_data <= {8'h78 , 24'h580f00};

10'd82: lut_data <= {8'h78 , 24'h581003};

10'd83: lut_data <= {8'h78 , 24'h581109};

10'd84: lut_data <= {8'h78 , 24'h581207};

10'd85: lut_data <= {8'h78 , 24'h581303};

10'd86: lut_data <= {8'h78 , 24'h581400};

10'd87: lut_data <= {8'h78 , 24'h581501};

10'd88: lut_data <= {8'h78 , 24'h581603};

10'd89: lut_data <= {8'h78 , 24'h581708};

10'd90: lut_data <= {8'h78 , 24'h58180d};

10'd91: lut_data <= {8'h78 , 24'h581908};

10'd92: lut_data <= {8'h78 , 24'h581a05};

10'd93: lut_data <= {8'h78 , 24'h581b06};

10'd94: lut_data <= {8'h78 , 24'h581c08};

10'd95: lut_data <= {8'h78 , 24'h581d0e};

10'd96: lut_data <= {8'h78 , 24'h581e29};

10'd97: lut_data <= {8'h78 , 24'h581f17};

10'd98: lut_data <= {8'h78 , 24'h582011};

10'd99: lut_data <= {8'h78 , 24'h582111};

10'd100: lut_data <= {8'h78 , 24'h582215};

10'd101: lut_data <= {8'h78 , 24'h582328};

10'd102: lut_data <= {8'h78 , 24'h582446};

10'd103: lut_data <= {8'h78 , 24'h582526};

10'd104: lut_data <= {8'h78 , 24'h582608};

10'd105: lut_data <= {8'h78 , 24'h582726};

10'd106: lut_data <= {8'h78 , 24'h582864};

10'd107: lut_data <= {8'h78 , 24'h582926};

10'd108: lut_data <= {8'h78 , 24'h582a24};

10'd109: lut_data <= {8'h78 , 24'h582b22};

10'd110: lut_data <= {8'h78 , 24'h582c24};

10'd111: lut_data <= {8'h78 , 24'h582d24};

10'd112: lut_data <= {8'h78 , 24'h582e06};

10'd113: lut_data <= {8'h78 , 24'h582f22};

10'd114: lut_data <= {8'h78 , 24'h583040};

10'd115: lut_data <= {8'h78 , 24'h583142};

10'd116: lut_data <= {8'h78 , 24'h583224};

10'd117: lut_data <= {8'h78 , 24'h583326};

10'd118: lut_data <= {8'h78 , 24'h583424};

10'd119: lut_data <= {8'h78 , 24'h583522};

10'd120: lut_data <= {8'h78 , 24'h583622};

10'd121: lut_data <= {8'h78 , 24'h583726};

10'd122: lut_data <= {8'h78 , 24'h583844};

10'd123: lut_data <= {8'h78 , 24'h583924};

10'd124: lut_data <= {8'h78 , 24'h583a26};

10'd125: lut_data <= {8'h78 , 24'h583b28};

10'd126: lut_data <= {8'h78 , 24'h583c42};

10'd127: lut_data <= {8'h78 , 24'h583dce};

10'd128: lut_data <= {8'h78 , 24'h5180ff};

10'd129: lut_data <= {8'h78 , 24'h5181f2};

10'd130: lut_data <= {8'h78 , 24'h518200};

10'd131: lut_data <= {8'h78 , 24'h518314};

10'd132: lut_data <= {8'h78 , 24'h518425};

10'd133: lut_data <= {8'h78 , 24'h518524};

10'd134: lut_data <= {8'h78 , 24'h518609};

10'd135: lut_data <= {8'h78 , 24'h518709};

10'd136: lut_data <= {8'h78 , 24'h518809};

10'd137: lut_data <= {8'h78 , 24'h518975};

10'd138: lut_data <= {8'h78 , 24'h518a54};

10'd139: lut_data <= {8'h78 , 24'h518be0};

10'd140: lut_data <= {8'h78 , 24'h518cb2};

10'd141: lut_data <= {8'h78 , 24'h518d42};

10'd142: lut_data <= {8'h78 , 24'h518e3d};

10'd143: lut_data <= {8'h78 , 24'h518f56};

10'd144: lut_data <= {8'h78 , 24'h519046};

10'd145: lut_data <= {8'h78 , 24'h5191f8};

10'd146: lut_data <= {8'h78 , 24'h519204};

10'd147: lut_data <= {8'h78 , 24'h519370};

10'd148: lut_data <= {8'h78 , 24'h5194f0};

10'd149: lut_data <= {8'h78 , 24'h5195f0};

10'd150: lut_data <= {8'h78 , 24'h519603};

10'd151: lut_data <= {8'h78 , 24'h519701};

10'd152: lut_data <= {8'h78 , 24'h519804};

10'd153: lut_data <= {8'h78 , 24'h519912};

10'd154: lut_data <= {8'h78 , 24'h519a04};

10'd155: lut_data <= {8'h78 , 24'h519b00};

10'd156: lut_data <= {8'h78 , 24'h519c06};

10'd157: lut_data <= {8'h78 , 24'h519d82};

10'd158: lut_data <= {8'h78 , 24'h519e38};

10'd159: lut_data <= {8'h78 , 24'h548001};

10'd160: lut_data <= {8'h78 , 24'h548108};

10'd161: lut_data <= {8'h78 , 24'h548214};

10'd162: lut_data <= {8'h78 , 24'h548328};

10'd163: lut_data <= {8'h78 , 24'h548451};

10'd164: lut_data <= {8'h78 , 24'h548565};

10'd165: lut_data <= {8'h78 , 24'h548671};

10'd166: lut_data <= {8'h78 , 24'h54877d};

10'd167: lut_data <= {8'h78 , 24'h548887};

10'd168: lut_data <= {8'h78 , 24'h548991};

10'd169: lut_data <= {8'h78 , 24'h548a9a};

10'd170: lut_data <= {8'h78 , 24'h548baa};

10'd171: lut_data <= {8'h78 , 24'h548cb8};

10'd172: lut_data <= {8'h78 , 24'h548dcd};

10'd173: lut_data <= {8'h78 , 24'h548edd};

10'd174: lut_data <= {8'h78 , 24'h548fea};

10'd175: lut_data <= {8'h78 , 24'h54901d};

10'd176: lut_data <= {8'h78 , 24'h53811e};

10'd177: lut_data <= {8'h78 , 24'h53825b};

10'd178: lut_data <= {8'h78 , 24'h538308};

10'd179: lut_data <= {8'h78 , 24'h53840a};

10'd180: lut_data <= {8'h78 , 24'h53857e};

10'd181: lut_data <= {8'h78 , 24'h538688};

10'd182: lut_data <= {8'h78 , 24'h53877c};

10'd183: lut_data <= {8'h78 , 24'h53886c};

10'd184: lut_data <= {8'h78 , 24'h538910};

10'd185: lut_data <= {8'h78 , 24'h538a01};

10'd186: lut_data <= {8'h78 , 24'h538b98};

10'd187: lut_data <= {8'h78 , 24'h558006};

10'd188: lut_data <= {8'h78 , 24'h558340};

10'd189: lut_data <= {8'h78 , 24'h558410};

10'd190: lut_data <= {8'h78 , 24'h558910};

10'd191: lut_data <= {8'h78 , 24'h558a00};

10'd192: lut_data <= {8'h78 , 24'h558bf8};

10'd193: lut_data <= {8'h78 , 24'h501d40};

10'd194: lut_data <= {8'h78 , 24'h530008};

10'd195: lut_data <= {8'h78 , 24'h530130};

10'd196: lut_data <= {8'h78 , 24'h530210};

10'd197: lut_data <= {8'h78 , 24'h530300};

10'd198: lut_data <= {8'h78 , 24'h530408};

10'd199: lut_data <= {8'h78 , 24'h530530};

10'd200: lut_data <= {8'h78 , 24'h530608};

10'd201: lut_data <= {8'h78 , 24'h530716};

10'd202: lut_data <= {8'h78 , 24'h530908};

10'd203: lut_data <= {8'h78 , 24'h530a30};

10'd204: lut_data <= {8'h78 , 24'h530b04};

10'd205: lut_data <= {8'h78 , 24'h530c06};

10'd206: lut_data <= {8'h78 , 24'h502500};

10'd207: lut_data <= {8'h78 , 24'h300802};

10'd208: lut_data <= {8'h78 , 24'h303511};

10'd209: lut_data <= {8'h78 , 24'h303646};

10'd210: lut_data <= {8'h78 , 24'h3c0708};

10'd211: lut_data <= {8'h78 , 24'h382041};

10'd212: lut_data <= {8'h78 , 24'h382100};

10'd213: lut_data <= {8'h78 , 24'h381431};

10'd214: lut_data <= {8'h78 , 24'h381531};

10'd215: lut_data <= {8'h78 , 24'h380000};

10'd216: lut_data <= {8'h78 , 24'h380100};

10'd217: lut_data <= {8'h78 , 24'h380200};

10'd218: lut_data <= {8'h78 , 24'h380304};

10'd219: lut_data <= {8'h78 , 24'h38040a};

10'd220: lut_data <= {8'h78 , 24'h38053f};

10'd221: lut_data <= {8'h78 , 24'h380607};

10'd222: lut_data <= {8'h78 , 24'h38079b};

10'd223: lut_data <= {8'h78 , 24'h380803};

10'd224: lut_data <= {8'h78 , 24'h380920};

10'd225: lut_data <= {8'h78 , 24'h380a02};

10'd226: lut_data <= {8'h78 , 24'h380b58};

10'd227: lut_data <= {8'h78 , 24'h380c07};

10'd228: lut_data <= {8'h78 , 24'h380d68};

10'd229: lut_data <= {8'h78 , 24'h380e03};

10'd230: lut_data <= {8'h78 , 24'h380fd8};

10'd231: lut_data <= {8'h78 , 24'h381306};

10'd232: lut_data <= {8'h78 , 24'h361800};

10'd233: lut_data <= {8'h78 , 24'h361229};

10'd234: lut_data <= {8'h78 , 24'h370952};

10'd235: lut_data <= {8'h78 , 24'h370c03};

10'd236: lut_data <= {8'h78 , 24'h3a0217};

10'd237: lut_data <= {8'h78 , 24'h3a0310};

10'd238: lut_data <= {8'h78 , 24'h3a1417};

10'd239: lut_data <= {8'h78 , 24'h3a1510};

10'd240: lut_data <= {8'h78 , 24'h400402};

10'd241: lut_data <= {8'h78 , 24'h30021c};

10'd242: lut_data <= {8'h78 , 24'h3006c3};

10'd243: lut_data <= {8'h78 , 24'h471303};

10'd244: lut_data <= {8'h78 , 24'h440704};

10'd245: lut_data <= {8'h78 , 24'h460b35};

10'd246: lut_data <= {8'h78 , 24'h460c22};

10'd247: lut_data <= {8'h78 , 24'h483722};

10'd248: lut_data <= {8'h78 , 24'h382402};

10'd249: lut_data <= {8'h78 , 24'h5001a3};

10'd250: lut_data <= {8'h78 , 24'h350300};

10'd251: lut_data <= {8'h78 , 24'h303521};

10'd252: lut_data <= {8'h78 , 24'h303669};

10'd253: lut_data <= {8'h78 , 24'h3c0707};

10'd254: lut_data <= {8'h78 , 24'h382047};

10'd255: lut_data <= {8'h78 , 24'h382100};

10'd256: lut_data <= {8'h78 , 24'h381431};

10'd257: lut_data <= {8'h78 , 24'h381531};

10'd258: lut_data <= {8'h78 , 24'h380000};

10'd259: lut_data <= {8'h78 , 24'h380100};

10'd260: lut_data <= {8'h78 , 24'h380200};

10'd261: lut_data <= {8'h78 , 24'h3803fa};

10'd262: lut_data <= {8'h78 , 24'h38040a};

10'd263: lut_data <= {8'h78 , 24'h38053f};

10'd264: lut_data <= {8'h78 , 24'h380606};

10'd265: lut_data <= {8'h78 , 24'h3807a9};

10'd266: lut_data <= {8'h78 , 24'h380805};

10'd267: lut_data <= {8'h78 , 24'h380900};

10'd268: lut_data <= {8'h78 , 24'h380a02};

10'd269: lut_data <= {8'h78 , 24'h380bd0};

10'd270: lut_data <= {8'h78 , 24'h380c07};

10'd271: lut_data <= {8'h78 , 24'h380d64};

10'd272: lut_data <= {8'h78 , 24'h380e02};

10'd273: lut_data <= {8'h78 , 24'h380fe4};

10'd274: lut_data <= {8'h78 , 24'h381304};

10'd275: lut_data <= {8'h78 , 24'h361800};

10'd276: lut_data <= {8'h78 , 24'h361229};

10'd277: lut_data <= {8'h78 , 24'h370952};

10'd278: lut_data <= {8'h78 , 24'h370c03};

10'd279: lut_data <= {8'h78 , 24'h3a0202};

10'd280: lut_data <= {8'h78 , 24'h3a03e0};

10'd281: lut_data <= {8'h78 , 24'h3a0800};

10'd282: lut_data <= {8'h78 , 24'h3a096f};

10'd283: lut_data <= {8'h78 , 24'h3a0a00};

10'd284: lut_data <= {8'h78 , 24'h3a0b5c};

10'd285: lut_data <= {8'h78 , 24'h3a0e06};

10'd286: lut_data <= {8'h78 , 24'h3a0d08};

10'd287: lut_data <= {8'h78 , 24'h3a1402};

10'd288: lut_data <= {8'h78 , 24'h3a15e0};

10'd289: lut_data <= {8'h78 , 24'h400402};

10'd290: lut_data <= {8'h78 , 24'h30021c};

10'd291: lut_data <= {8'h78 , 24'h3006c3};

10'd292: lut_data <= {8'h78 , 24'h471303};

10'd293: lut_data <= {8'h78 , 24'h440704};

10'd294: lut_data <= {8'h78 , 24'h460b37};

10'd295: lut_data <= {8'h78 , 24'h460c20};

10'd296: lut_data <= {8'h78 , 24'h483716};

10'd297: lut_data <= {8'h78 , 24'h382404};

10'd298: lut_data <= {8'h78 , 24'h5001a3};

10'd299: lut_data <= {8'h78 , 24'h350300};

10'd300: lut_data <= {8'h78 , 24'h301602};

10'd301: lut_data <= {8'h78 , 24'h3b070a};

//10'd251: lut_data <= {8'h78 , 24'h503d80};

//10'd252: lut_data <= {8'h78 , 24'h474101};

10'd302: lut_data <= {8'hff , 24'hffffff};

default:lut_data <= {8'h00,16'h0000,8'h00};

endcase

end

endmodule

四,摄像头分辨率设置

下面是摄像头可以设置的分辨率,我们这个摄像头设置的1280*720p这个分辨率

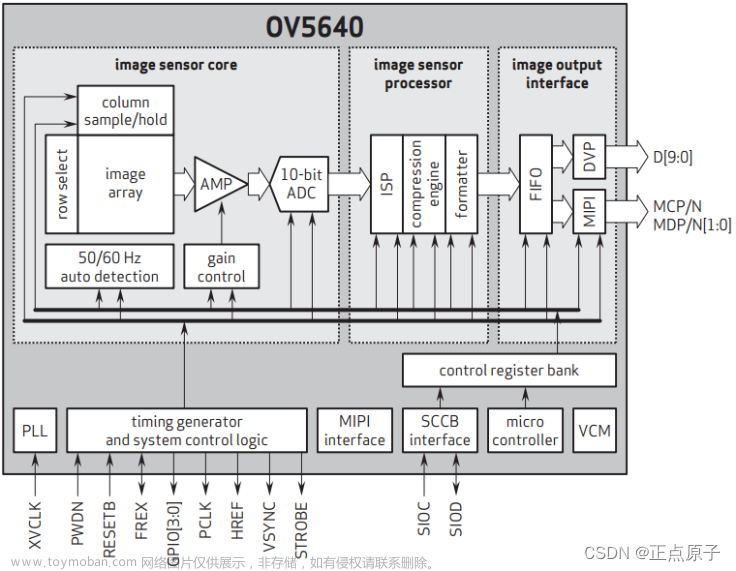

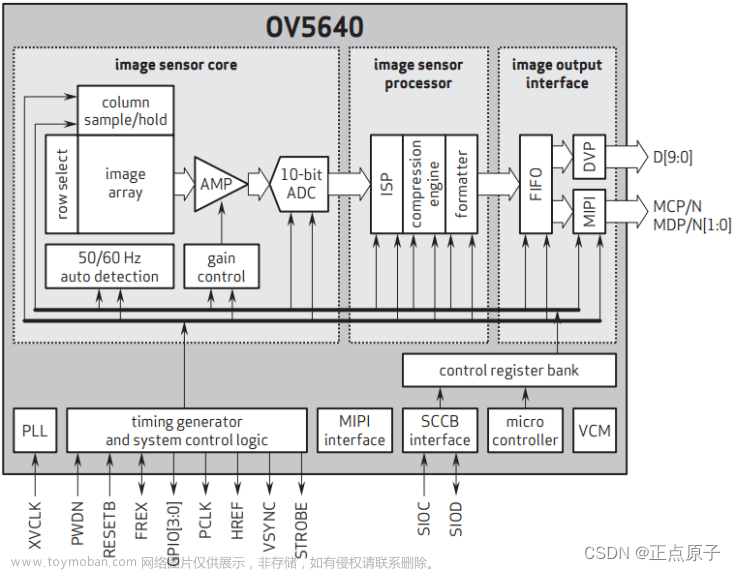

五,摄像头数据采集

我们这个工程设置的输出为RGB565格式,,可以看出如果抓取16位数据,刚好是两个8位数据合成,也就是两个D[2]~D[9]需要舍弃低两位D[0]和D[1],所以我们采集数据是由两个8位组合为一个十六位数据。

数据转换模块,将两个8位输入数据转为16位输出

六,DDR配置

ddr具体配置,请参考上一个章节AX7A200教程(8): HDMI输入和输出显示1080p视频,本章节不再做详细介绍。

七,HDMI输出配置

hdmi输出配置和摄像头配置采用同样的iic模块配置,只是配置文件有所不同

八,输出显示顶层模块和硬件连接

摄像头显示顶层

`timescale 1ps/1ps

module top

(

inout hdmi_scl,

inout hdmi_sda,

output hdmi_nreset_v10,//HDMI reset compatibility for version 1.0 and 1.1

output hdmi_nreset, //HDMI reset compatibility for version 1.0 and 1.1

inout cmos_scl, //cmos i2c clock

inout cmos_sda, //cmos i2c data

input cmos_vsync, //cmos vsync

input cmos_href, //cmos hsync refrence,data valid

input cmos_pclk, //cmos pxiel clock

input [7:0] cmos_db, //cmos data

output cmos_rst_n, //cmos reset

output cmos_pwdn,

output cmos_xclk,

output vout_clk,

output vout_hs,

output vout_vs,

output vout_de,

output[23:0] vout_data,

inout [31:0] ddr3_dq,

inout [3:0] ddr3_dqs_n,

inout [3:0] ddr3_dqs_p,

output [14:0] ddr3_addr,

output [2:0] ddr3_ba,

output ddr3_ras_n,

output ddr3_cas_n,

output ddr3_we_n,

output ddr3_reset_n,

output [0:0] ddr3_ck_p,

output [0:0] ddr3_ck_n,

output [0:0] ddr3_cke,

output [0:0] ddr3_cs_n,

output [3:0] ddr3_dm,

output [0:0] ddr3_odt,

//Differential system clocks

input sys_clk_p,

input sys_clk_n,

output[3:0] led,

input sys_rst

);

wire read_req;

wire read_req_ack;

wire read_en;

wire[31:0] read_data;

wire write_en;

wire[31:0] write_data;

wire write_req;

wire write_req_ack;

wire video_clk; //video pixel clock

wire hs;

wire vs;

wire de;

wire[9:0] lut_index;

wire[31:0] lut_data;

wire[9:0] cmos_lut_index;

wire[31:0] cmos_lut_data;

wire clk_100m;

wire clk_24m;

wire rst_n;

wire locked;

wire power_done;

wire[15:0] cmos_16bit_data;

wire cmos_16bit_wr;

wire[31:0] cmos_write_data;

wire sys_clk_w;

wire init_calib_complete;

wire start_en;

wire clk_out2;

assign vout_hs = hs;

assign vout_vs = vs;

assign vout_de = de;

assign vout_clk = video_clk;

assign rst_n = locked;

assign hdmi_nreset_v10 = locked;

assign hdmi_nreset = locked;

assign cmos_xclk = (power_done)? clk_24m:1'b0;

assign cmos_write_data = {8'd0,cmos_16bit_data[4:0],3'd0,cmos_16bit_data[10:5],2'd0,cmos_16bit_data[15:11],3'd0};

/*****************************************pll*******************************************/

IBUFDS sys_clk_ibufgds

(

.O (sys_clk_w),

.I (sys_clk_p),

.IB (sys_clk_n)

);

clk_wiz_0 instance_name

(

// Clock out ports

.clk_out1(clk_100m), // output clk_out1

.clk_out2(clk_out2), // output clk_out2

.clk_out3(video_clk), // output clk_out3

.clk_out4(clk_24m), // output clk_out4

// Status and control signals

.resetn(sys_rst), // input reset

.locked(locked), // output locked

// Clock in ports

.clk_in1(sys_clk_w)); // input clk_in1

/***********************************ov5640_power***************************************/

power_ctrl power_ctrl_inst(

// system signals

.i_clk (clk_100m ),// 100MHz

.rst_n (rst_n ),

.ov5640_pwdn (cmos_pwdn ),

.ov5640_rst_n (cmos_rst_n ),

.power_done (power_done )

);

/***********************************ov5640_config***************************************/

//I2C master controller

i2c_config i2c_config_m1(

.rst (~power_done ),

.clk (clk_100m ),

.clk_div_cnt (16'd200 ),

.i2c_addr_2byte (1'b1 ),

.lut_index (cmos_lut_index ),

.lut_dev_addr (cmos_lut_data[31:24] ),

.lut_reg_addr (cmos_lut_data[23:8] ),

.lut_reg_data (cmos_lut_data[7:0] ),

.error ( ),

.done ( ),

.i2c_scl (cmos_scl ),

.i2c_sda (cmos_sda )

);

//configure look-up table

lut_ov5640_rgb565_1280_720 lut_ov5640_m1(

.lut_index (cmos_lut_index ),

.lut_data (cmos_lut_data )

);

/***********************************hdmi_out_config***************************************/

//I2C master controller

i2c_config i2c_config_m0(

.rst (~rst_n ),

.clk (clk_100m ),

.clk_div_cnt (16'd500 ),

.i2c_addr_2byte (1'b0 ),

.lut_index (lut_index ),

.lut_dev_addr (lut_data[31:24] ),

.lut_reg_addr (lut_data[23:8] ),

.lut_reg_data (lut_data[7:0] ),

.error ( ),

.done ( ),

.i2c_scl (hdmi_scl ),

.i2c_sda (hdmi_sda )

);

//configure look-up table

lut_hdmi lut_hdmi_m0(

.lut_index (lut_index ),

.lut_data (lut_data )

);

/**********************************cmos_data****************************************************/

//CMOS sensor 8bit data is converted to 16bit data

cmos_8_16bit cmos_8_16bit_m0(

.rst (~rst_n ),

.pclk (cmos_pclk ),

.pdata_i (cmos_db ),

.de_i (cmos_href ),

.pdata_o (cmos_16bit_data ),

.hblank ( ),

.de_o (cmos_16bit_wr )

);

/***********************************hdmi_out_en***************************************/

vs_count vs_count_inst(

.clk(clk_100m),

.rst(init_calib_complete),

.vs_in(cmos_vsync),//cmos_vsync

.start_en(start_en)

);

/**************************************ddr*************************************/

wire read_fifo_empty;

wire read_valid;

ddr_test ddr_test_inst (

// Memory interface ports

.ddr3_addr (ddr3_addr), // output [13:0] ddr3_addr

.ddr3_ba (ddr3_ba), // output [2:0] ddr3_ba

.ddr3_cas_n (ddr3_cas_n), // output ddr3_cas_n

.ddr3_ck_n (ddr3_ck_n), // output [0:0] ddr3_ck_n

.ddr3_ck_p (ddr3_ck_p), // output [0:0] ddr3_ck_p

.ddr3_cke (ddr3_cke), // output [0:0] ddr3_cke

.ddr3_ras_n (ddr3_ras_n), // output ddr3_ras_n

.ddr3_reset_n (ddr3_reset_n), // output ddr3_reset_n

.ddr3_we_n (ddr3_we_n), // output ddr3_we_n

.ddr3_dq (ddr3_dq), // inout [31:0] ddr3_dq

.ddr3_dqs_n (ddr3_dqs_n), // inout [3:0] ddr3_dqs_n

.ddr3_dqs_p (ddr3_dqs_p), // inout [3:0] ddr3_dqs_p

.ddr3_cs_n (ddr3_cs_n), // output [0:0] ddr3_cs_n

.ddr3_dm (ddr3_dm), // output [3:0] ddr3_dm

.ddr3_odt (ddr3_odt), // output [0:0] ddr3_odt

.init_calib_complete (init_calib_complete),

// System Clock Ports

.sys_clk_i (clk_out2),

.sys_rst (rst_n), // input sys_rst

//fifo

.wr_clk (cmos_pclk),

.rd_clk (video_clk),

.write_fifo_wr_en (cmos_16bit_wr),

.write_fifo_din (cmos_write_data),

.read_fifo_rd_en (read_en),

.read_fifo_dout (read_data),

.read_fifo_empty (read_fifo_empty),

.read_valid (read_valid),

.ddr_rd_en (start_en),

.vin_vs (cmos_vsync),

.vout_vs (read_req),

.rd_reset (read_req_ack)

);

//video output timing generator and generate a frame read data request

video_timing_data video_timing_data_m0

(

.video_clk (video_clk ),

.rst (~read_valid ),

.read_req (read_req ),

.read_req_ack (read_req_ack ),

.read_en (read_en ),

.read_data (read_data ),

.hs (hs ),

.vs (vs ),

.de (de ),

.vout_data (vout_data )

);

ila_0 ila_0_name (

.clk(clk_out2), // input wire clk

.probe0(read_en), // input wire [0:0] probe0

.probe1(read_valid), // input wire [0:0] probe1

.probe2(start_en), // input wire [0:0] probe2

.probe3(read_req), // input wire [0:0] probe3

.probe4(read_data), // input wire [0:0] probe4

.probe5(vout_clk), // input wire [0:0] probe5

.probe6(vout_hs), // input wire [0:0] probe6

.probe7(vout_vs), // input wire [0:0] probe7

.probe8(vout_de), // input wire [0:0] probe8

.probe9(vout_data) // input wire [0:0] probe9

);

endmodule

vivado工程截图,可以看到有很多模块,这里不一一截图提供代码

抓取的hdmi输出管脚波形  摄像头输出显示硬件连接

摄像头输出显示硬件连接 文章来源:https://www.toymoban.com/news/detail-819462.html

文章来源:https://www.toymoban.com/news/detail-819462.html

九,摄像头输出显示效果

如若转载,请注明出处 文章来源地址https://www.toymoban.com/news/detail-819462.html

到了这里,关于AX7A200教程(9): ov5640摄像头输出显示720p视频的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!