注:扫码关注小青菜哥哥的weixin公众号,免费获得更多优质的核探测器与电子学资讯~

本篇将以德州仪器(TI)的高速ADC芯片——ads52j90为例,进行ADC的4线SPI配置时序介绍与分析。

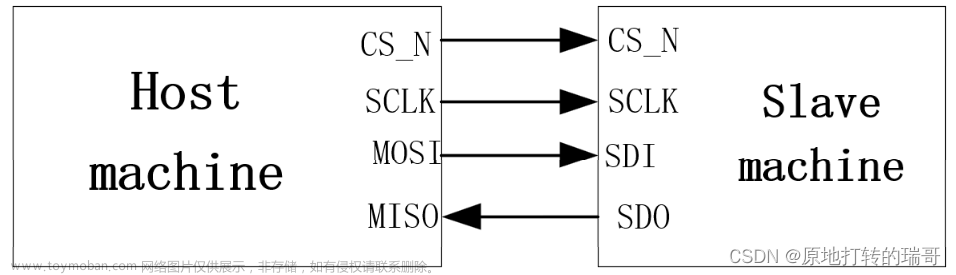

从ads52j90的数据手册我们不难发现,其SPI控制模块主要包含4根信号线,即SEN、SCLK、SDIN以及SDOUT。TI公司对其产品SPI配置信号的命名方式与通用的SPI信号命名方式不一样,但实际上SEN对应CSB、SDIN对应SDI、SDOUT对应SDO、SCLK不变。

1,SEN:控制ADC的SPI读写的使能信号;

2,SDIN:FPGA写入ADC的配置数据(寄存器地址和对应地址的数据);

3,SDOUT:ADC对应地址输出的配置寄存器数据;

4,SCLK:FPGA提供给ADC的SPI接口时钟。

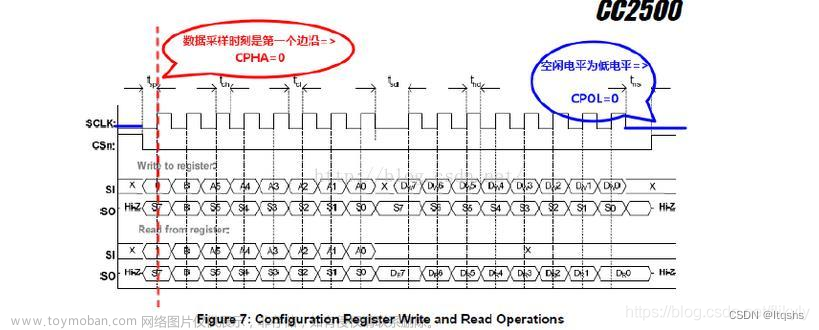

首先介绍该ADC的SPI的写功能,datasheet给出的时序图如图1所示:我们首先大致看一下写时序图,能够了解到对于SDIN来说,需要先写入A7~A0的8bit的地址,接下来写入该地址下的16bit的寄存器数值D15~D0,也就是说每进行一次写操作需要不间断的写入24bit 的数据。对于SEN来说,在进行写操作时,其一直保持低电平,写之前和写完后都保持高电平。对于SCLK来说,其上升沿每次采集每1bit SDIN数据的中心位置,共需要采集24次,才能完成这24bit SDIN数据的写入。

图1:SPI写时序图

上面三点就是我们初步看这个时序图所得到的结论。对于该ADC,按照这种方式进行写操作就不会有问题。实际上所有ADC的SPI写操作都有类似于上面介绍的共同准则,这里归纳如下:

- 无论SPI进行读还是写操作,SEN必须拉低,否则SPI不工作(既不读也不写),读、写完成之后SEN必须拉高;

- SDIN的数据每次在SCLK的上升沿写入SPI;

- SDIN的数据组成一定是先写入配置寄存器地址,再连续写入配置寄存器数值;

图2:SPI时序要求

另外,我们看到时序图上有许多时间参数,我们在写代码时不仅要遵守以上的共同准则,还要满足这些参数的时序关系,并保留一定的时间裕量。datasheet都提供了这些参数的大小,如图2所示。比如tSCLK的最小值是50ns,也就意味着SPI的时钟最高只能到20MHz。tSEN_SU 的最小值为8ns,就表示SEN下降沿至少提前第一个SCLK的上升沿时间8ns。tDSU 则表示SDIN的数据必须至少提前SCLK的上升沿5ns准备好,等等。只要遵守了相关的SPI准则以及datasheet里的SPI时序参数,SPI的写操作就不会有问题了。

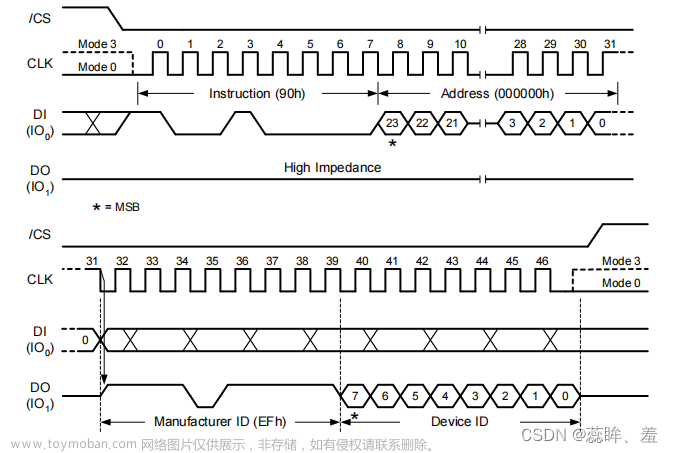

现在我们介绍该ADC的SPI读操作,如图3所示。读操作的主要目的是监测ADC内部寄存器状态,从而判断ADC的配置状态是否符合用户的需求。从图上我们可以看到,SPI的读操作可以分解为两个部分:第一个部分是先写入A7~A0 8bit的寄存器地址到SDIN,然后SDOUT输出对应地址的16bit的寄存器数值。

这里重点强调一下:理论上来说,在上升沿锁存写入的地址最后1bit后,在接下来的每次SCLK下降沿,SDOUT输出1bit寄存器值,直到16bit寄存器数值完全输出。但实际上每次SCLK下降沿输出的数据只有经过tOUT_DV (12ns ~28ns)后才稳定,后端FPGA才能正确接收。从图上我们不难发现,FPGA在SCLK的上升沿附近获取SDOUT的数据是非常合适的,在这个位置获取的数据最稳定。

图3:SPI读时序图

4线SPI的读写时序分析就到这里了,再次强调几个关键点:

关键点1:SEN在读写操作时,必须拉低。读写完成之后,必须拉高。

关键点2:SDIN的数据每次必须在SCLK的上升沿写入SPI。对应的数据格式一定是寄存器地址+要写入的寄存器数值。

关键点3:SOUT的数据总是在SCLK的下降沿输出,因此选择FPGA在SCLK的上升沿获取SDOUT数据最稳定。

关键点4:一定要满足datasheet给出的SPI的时序参数,并在代码实现时要留有适当的时序裕量。文章来源:https://www.toymoban.com/news/detail-821984.html

今天的博文就到这里了,有问题请在小青菜哥哥的公众号留言,谢谢!文章来源地址https://www.toymoban.com/news/detail-821984.html

到了这里,关于FPGA配置高速ADC篇(2)_4线SPI配置时序分析的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!