注:扫码关注小青菜哥哥的weixin公众号,免费获得更多优质的核探测器与电子学资讯~

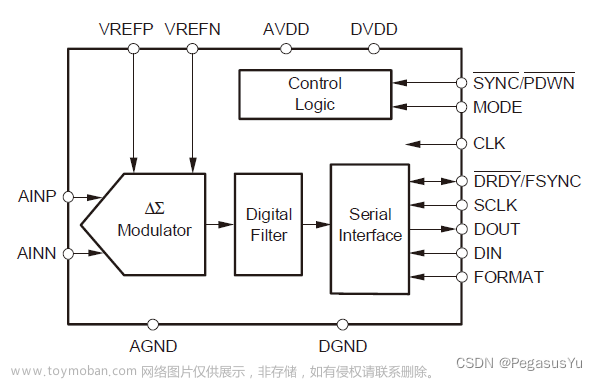

本篇小青菜哥哥继续以ADI公司的16通道高速ADC—AD9249为实例,向大家演示FPGA是如何通过SPI接口向该ADC读写寄存器配置数据的。如下图所示为AD9249的功能框图,其为16通道、65MSPS、14bit精度的多通道高速ADC,且其SPI接口只为三线模式:

该ADC的SPI配置完全可以用上篇介绍的AD9639的配置方式完成。但本篇实现的方式由于采用的是kintex7系列的FPGA,且操作软件为vivado,因此小青菜哥哥在verilog代码实现上简化了很多,更容易让大家理解!

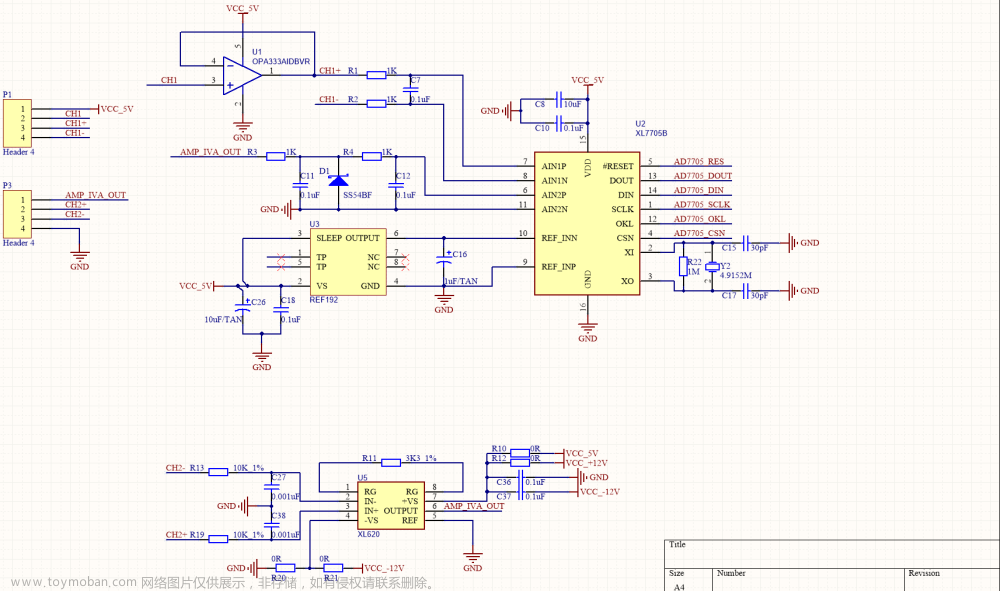

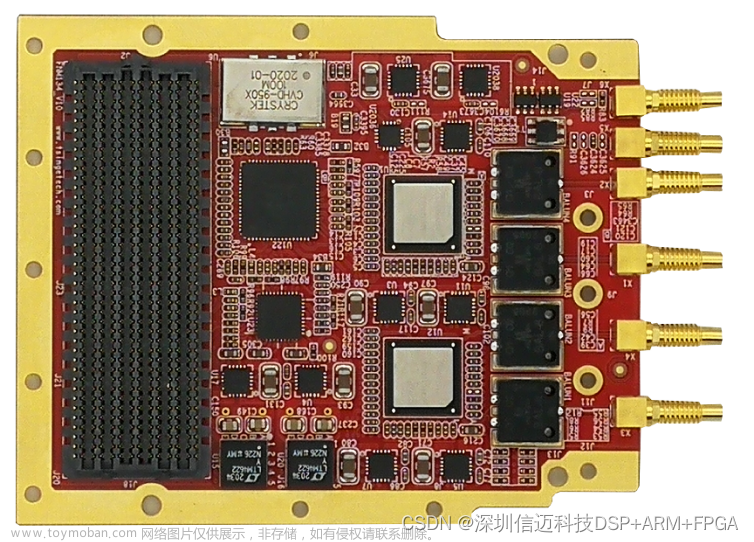

如下图所示为小青菜哥哥设计的80通道的FPGA数据采集系统,采用5片AD9249+kintex7 FPGA+网络+光纤传输的方式,本篇的SPI读写将以其中的一片ADC芯片为例,代码为verilog,vivado版本为2017.4。

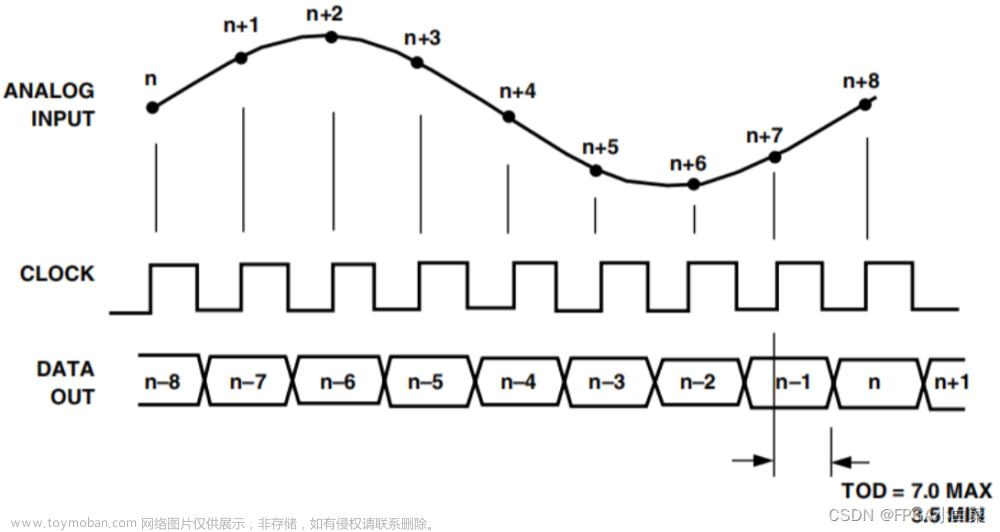

该款ADC和ADI公司其他ADC的SPI配置方式相同,其数据传输的结构如下图所示:

每次事件传输24bit数据,MSB为读/写控制位,接下来2bit为一次传输数据的大小,一般写0即可,A12-A0为地址位,D7-D0为数据位。

当FPGA向ADC读写配置数据时,就需要完成上图的时序功能,每配置一个寄存器,就执行上图的逻辑功能一次,如果是配置多个寄存器,则反复执行上述逻辑即可。

本次的3线配置逻辑的顶层逻辑接口如下图所示:

这里需要注意的是,配置接口中多了一个Tri_en信号,该信号即为三态口控制信号,三态口的定义如下图所示:

本例程同样实现了3个寄存器的写和读,如下图所示:

当然,配置个数可以任意改动,只要改变Wr_n这个写参数和Rd_n读参数个数即可。RdData1~3为存储读到的3个寄存器的值,方便ILA逻辑分析仪观察。

具体的3线SPI读写过程,咱们在上一篇的AD9639已经说过了,本篇再次介绍ADI的AD9249配置,代码实现上的主要区别在于哪呢?就是在循环读写上!

如下如所示,上边为ise14.7实现的方式,下边为vivado实现的方式,可以看到,同样写入3个寄存器数据,显然vivado实现起来更加方便,便于扩展,改变n值即可。小青菜哥哥一直不明白为何右边的这种数组循环写法不能在ise14.7上运行,按理说verilog2001标准,ise和vivado都支持才对,如果有读者知道原因,请告诉小青菜哥哥一声~

同样的,在读寄存器数据阶段,循环代码也可以简化,简化前后如下图所示:

最后,在移位取数阶段,同样可以简化,简化前后如下图所示:

这样3线SPI的配置过程完成后。用上面介绍的代码在vivado2017.4上运行,并下载到电路板上,咱们观察的ILA逻辑分析仪吧!

如下图所示为分别读写3个寄存器的时序图,可以看到最终咱们读到的寄存器值分别为8’h92、8’h04、8’h42,与预期值完全一致,配置成功!

咱们再看看逻辑实现的写过程的具体时序图吧,下图所示为写WrtieReg2的实际时序,写入的数据为8’h04:

咱们再看读该寄存器(RdData3)的时序图,如下图所示:可以看到读到的数据为8’h42,和WrtieReg3写入的数据一致,OK!在vivado中,这里可以加入sdin,正如上篇所说,sdin和sdout其实都是SDIO信号,从时序图可以看出来:

AD9249的3线SPI实际操作就这样完成了,本篇的说明比较少,小青菜哥哥主要是想向大家演示,前两篇ise14.7平台实现的AD9639配置的代码,在vivado平台下其实可以更加简化,使用起来更加方便。

至于为什么同一段代码在vivado下可行,ise却不行,小青菜哥哥估计vivado支持的verilog标准更高一些吧,能够支持二维数组例化,毕竟对于二维数组操作来说,多年前的verilog是不支持例化的。

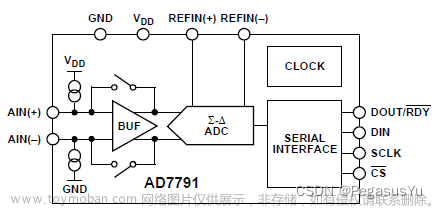

从下一篇开始,小青菜哥哥将以德州仪器(TI)的ADC芯片为例,介绍其FPGA的SPI配置方式~文章来源:https://www.toymoban.com/news/detail-822539.html

今天的博文就到这里了,有问题请在小青菜哥哥的公众号留言,谢谢!文章来源地址https://www.toymoban.com/news/detail-822539.html

到了这里,关于FPGA配置高速ADC篇(8)_AD9249三线SPI配置实战的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!