软件:vivado 2020.2

参考文献:文档xilinx官网pg057-fifo-generator文档下载链接官网https://docs.xilinx.com/v/u/en-US/pg057-fifo-generatorhttps://docs.xilinx.com/v/u/en-US/pg057-fifo-generatorhttps://docs.xilinx.com/v/u/en-US/pg057-fifo-generator

原官网免费文档已被上传为付费文档,笔者上传的免费文档未过审核。

一、FIFO的基本思想

first-in first-out (FIFO),即先入先出。fifo可以当做一个进出互不影响的储存器,当然,储存器是有容量的,一直进,储存器满了,自然无法再进;同样,一直出也是一个道理。为了方便理解 ,我们把fifo比作快递中转站,那么所要传递的数据就是一个个快递。对于fifo来说,写通道就是往中转站里存快递;读通道就是从中转站里取快递。

当上家(主机)想要往中转站(fifo)里存快递(写数据)时,先发出一个信号(wr_en)告诉中转站,它想要存快递,而中转站(fifo)也要告诉上家是否满了(满信号);同样中转站也要告诉下家(从机)它是否还有库存(空信号),下家(从机)发送ready信号告诉中转站(fifo),它准备好接收信号。fifo的深度就是其容量。

同步fifo即主从机使用同一clk。异步fifo即用不同clk。

二、不同接口的fifo(Native Axi stream)

2.1 Native 接口fifo

2.1.1 Native接口主要信号及其功能

写数据通道:

wr_clk. 写时钟

wr_en 写使能信号,告诉fifo进行写数据使能;

full 满信号,告诉写模块,fifo已满;

almost_full 将满信号,比full提前一个时钟拉高,提示fifo将满;

prog_full 标记信号,当fifo中数据达到prog_full,此信号拉高;

din 写数据,写模块往fifo里写东西时,将din写入fifo

读数据通道:同理,不过多赘述。

2.1.2 Native 接口读写数据的发生时序

写数据:wr_en拉高时,写入数据,但是full信号拉高(即fifo满)写数据暂停。

读数据:rd_en拉高时,读取数据,但是empty信号拉高(fifo空)读数据暂停。

换而言之,wr_en && ~full时,写入数据;rd_en && ~empty时,读取数据。

2.1.3 Native 接口fifo算法以及具体verilog代码

native 接口 FIFO Generator 13.2 verilog 代码

2.1.4 standard fifo 与fwft fifo输出时序逻辑分析

[vivado fifo] 如何理解standard fifo 和fwft fifo的输出时序问题

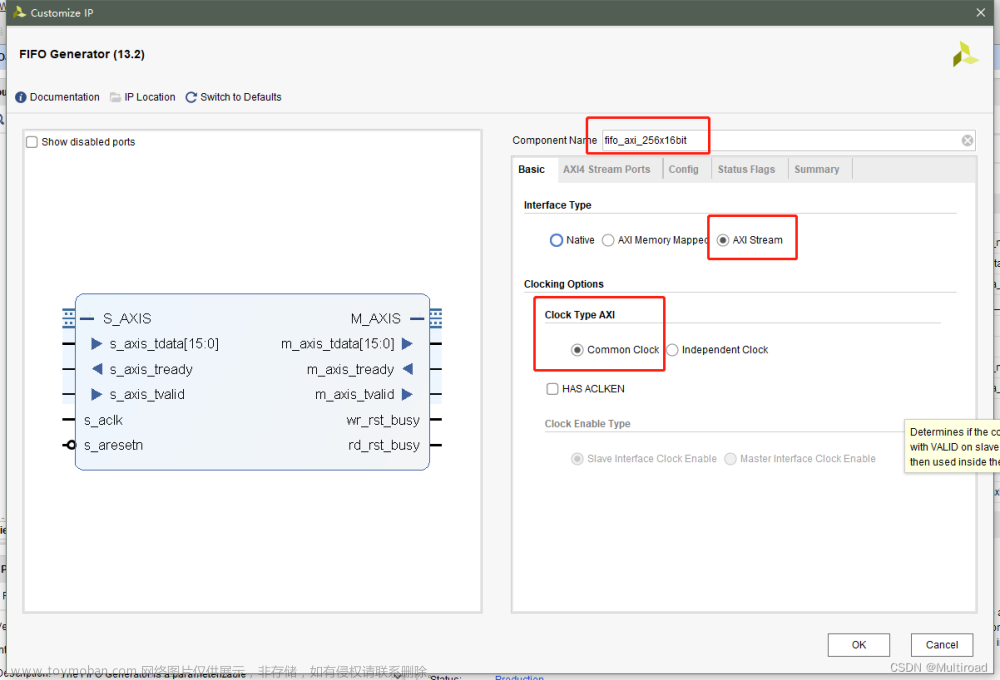

2.2AXI Stream接口FIFO

2.1.1 axis接口fifo主要信号及其功能

axis接口是axi三种常见类型之一,axi stream。先挖个坑,以后有时间可能会系统介绍axif,axil和axis。回归正题axis接口与native接口类似,不过有写些接口的名称发生变化。

valid -- rd_en--~empty : valid是输出有效信号,其拉高时,数据有效。与rd_en信号含义略有不同但是功能相同,都是想写数据时拉高;同样fifo想往从机里写数据,也要告诉从机fifo内还有数据即~empty拉高。

ready --~full --rd_en : ready是输入准备信号,其拉高说明从机准备好接收数据。fifo准备好接收数据的前提是内部还有空间即~full拉高;而从机的rd_en就是告诉fifo其准备好接收信号。

与native interface不同的是axi interface满足数据传输时,传输的数据不止有data信号。

data : 传输的数据

strobe: 掩码。掩码的第n位为1,则data第nbyte数据正常输出。为0,则第n byte数据全为0。

last信号:一次传输完成后,拉高一个时钟。

user:用户自定义信号。

id:用于标识传输id。

2.2.2 输出时序逻辑与axi的握手机制

axis接口数据传输时采用的握手机制是一种非常经典的valid-ready握手机制(就用它俩握手,笔者也不知道有没有官方名字)。其特征为

1.数据发送方输出valid告诉对方数据有效; 数据接收方输出ready,告诉对方准备接收

2.当且仅当,valid && ready == 1时发生数据传输。

思考:1.主机 从机 valid ready 它们之间有什么联系?

没有联系,valid是由发送方输出,ready由接收方发出。通常是主机向从机发送数据,所以valid有主机发出比较常见。但是对于全双工、半双工这些一定会有从机发送数据的情况,此时valid就是由从机发出。

2. valid和ready同时拉高时,才输出。那么,没传完一个拉低了呢?

指有二者同时拉高时输出,任和其他情况都不发生数据传输。一次传输要求二者全程拉高,如果中断,数据传输中止,等待下次握手,接着传。

2.2.3 axis接口fifo代码

暂时不想写,代码都在内网机,所有代码全是我用平板手打的太麻烦了。等以后吧。不会的,联系我也行。(๑ت๑)文章来源:https://www.toymoban.com/news/detail-822919.html

文章来源地址https://www.toymoban.com/news/detail-822919.html

到了这里,关于FPGA FIFO基本介绍(FIFO Geneerator(13.2))的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!