芯片原厂必学课程 - 第十篇章 - 01 基于 ARM SoC 的视频传输系统设计

10-01-01 引言

新芯设计:专注,积累,探索,挑战

引言

对于《基于 SoC 的卷积神经网络车牌识别系统设计》这个极具竞争的项目而言,其主要是通过 CPU 软核 IP 在纯 FPGA 平台上构建一个 AI SoC 卷积神经网络车牌识别系统,其中,缩放、填充层、卷积层、ReLU、池化层、全连接层 IP 都是 Verilog 设计的,同时集成了各种高性能的 IP,这是最具挑战性的 AI SoC 芯片设计项目,集成了 Python 卷积神经网络代码、Verilog 卷积神经网络硬件设计、ARM SoC 设计、ARM 与 FPGA 的交叉编译流程等等。这就对于想要入门数字 IC 设计的学员的学习能力要求较高,同时还需要投入非常多的一个学习时间,最终导致了学员学习较为吃力且较难吸收

于是《基于 SoC 的卷积神经网络车牌识别系统设计》划分成了《基于 ARM SoC 的视频传输系统设计》和《基于 AI IP 的卷积神经网络车牌识别设计》

虽然最近忙于流片工作和量产项目,依旧投入了大量的时间于《基于 ARM SoC 的视频传输系统设计》的设计推进,目前已经是完全最新的设计,主要的成果如下所示,主要包括了系统架构、顶层集成和内存映射,资源占比和功耗统计,时序约束和引脚约束,编程载入和信号观测,软件代码、内核信息和内核识别,调试模式和串口打印以及上板记录

NOTES:本文来自《芯片原厂必学课程 - 第十篇章 - 基于 ARM SoC 的视频传输系统设计》技术专栏

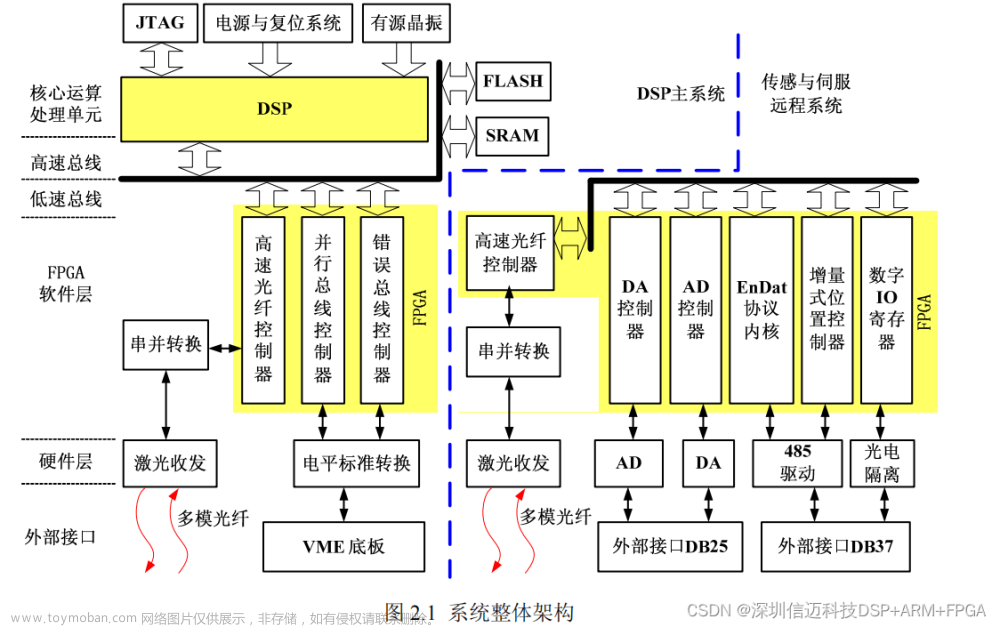

🌏 一、系统架构、顶层集成和内存映射

✅ 这是关于系统架构_详细版、系统架构_简化版、顶层集成和内存映射的成果:

//《基于 ARM SoC 的视频传输系统设计》的顶层端口:

module arm_video_soc_top

(

//CLOCK && RESET

input wire sys_clk_p ,

input wire sys_clk_n ,

input wire sys_rst_n ,

//OV5640 && IIC

input wire cmos_pclk_i ,

input wire cmos_href_i ,

input wire cmos_vsync_i ,

input wire [7:0] cmos_data_i ,

output wire cmos_xclk_o ,

output wire cmos_rstn_o ,

inout wire cmos_i2c_scl ,

inout wire cmos_i2c_sda ,

//VGA

output wire vga_dclk_o ,

output wire vga_hsync_o ,

output wire vga_vsync_o ,

output wire vga_de_o ,

output wire [23:0] vga_data_o ,

//GPIO

inout wire GPIO_KEY_IN ,

inout wire GPIO_LED_OUT ,

//UART

input wire UART_rxd ,

output wire UART_txd ,

//SWD

input wire SWD_TCK ,

inout wire SWD_TMS ,

//FLASH

inout wire QSPI_FLASH_D0 ,

inout wire QSPI_FLASH_D1 ,

inout wire QSPI_FLASH_D2 ,

inout wire QSPI_FLASH_D3 ,

inout wire QSPI_FLASH_SCK ,

inout wire QSPI_FLASH_SS ,

//DDR3

output wire [14:0] DDR3_addr ,

output wire [2:0] DDR3_ba ,

output wire DDR3_cas_n ,

output wire [0:0] DDR3_ck_n ,

output wire [0:0] DDR3_ck_p ,

output wire [0:0] DDR3_cke ,

output wire [0:0] DDR3_cs_n ,

output wire [3:0] DDR3_dm ,

inout wire [31:0] DDR3_dq ,

inout wire [3:0] DDR3_dqs_n ,

inout wire [3:0] DDR3_dqs_p ,

output wire [0:0] DDR3_odt ,

output wire DDR3_ras_n ,

output wire DDR3_reset_n ,

output wire DDR3_we_n ,

output wire init_calib_complete

);

🌏 二、资源占比和功耗统计

✅ 这是关于资源占比和功耗统计的数据:

🌏 三、时序约束和引脚约束

✅ 这是关于时序约束和引脚约束的成果:

🌏 四、编程载入和信号观测

✅ 这是关于编程载入和信号观测的成果:

🌏 五、软件代码、内核信息和内核识别

✅ 这是关于软件代码、内核信息和内核识别的成果:

🌏 六、调试模式和串口打印

✅ 这是关于调试模式和串口打印的成果:

🌏 七、上板记录

✅ 这是关于开发板及其外设和开发板视频传输系统的上板记录成果:

文章来源:https://www.toymoban.com/news/detail-822989.html

文章来源:https://www.toymoban.com/news/detail-822989.html

文章来源地址https://www.toymoban.com/news/detail-822989.html

文章来源地址https://www.toymoban.com/news/detail-822989.html

到了这里,关于基于 ARM SoC 的视频传输系统设计(10-01-01)引言的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!