亚军老师的这本书《AMD FPGA设计优化宝典》,他主要讲了两个东西:

第一个东西是代码的良好风格;

第二个是设计收敛等的本质。

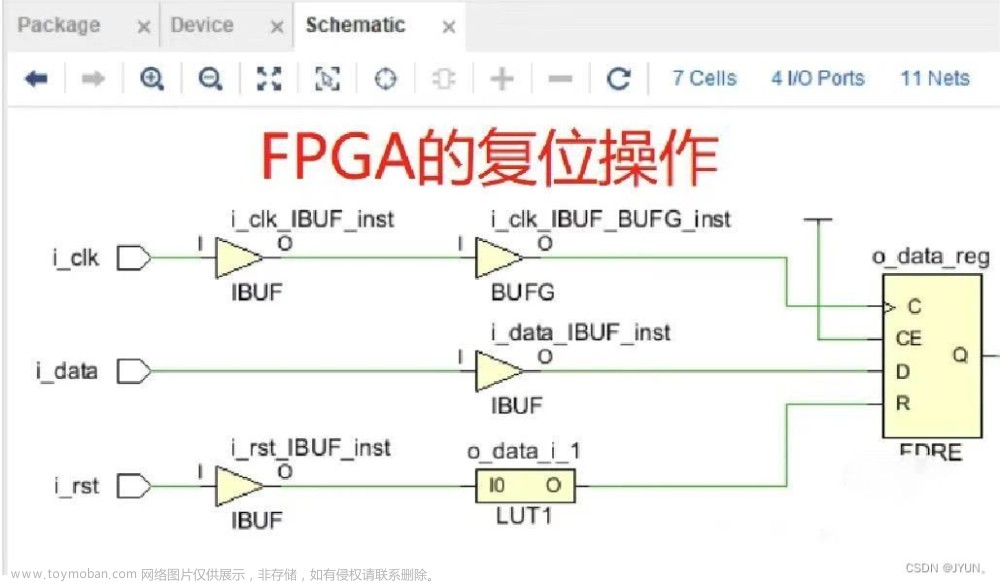

这个书的结构是一个总论,加上另外的9个优化,包含的有:时钟网络、组合逻辑、触发器、移位寄存器、存储器、乘加运算单元、状态机、扇出、布线拥塞。大部头的书看起来比较痛苦,我简化的方式,选择触发器一章入手,这个平时有点了解,也觉得看完会用上的概率大一些。这章是书的第4章,全局复位方面的内容,接前面的我的文章:

全局复位

P197

电路板上的按压开关复位信号,做全局复位,带来的影响是什么?

这种全局复位信号,频率比较低,如果用作FPGA内部的同步复位,那这个信号本身扇出就会很大,再由于频率较低导致的建立时间变小了,容易让不同级的寄存器的复位不在同一个时钟内激活、时序不收敛。

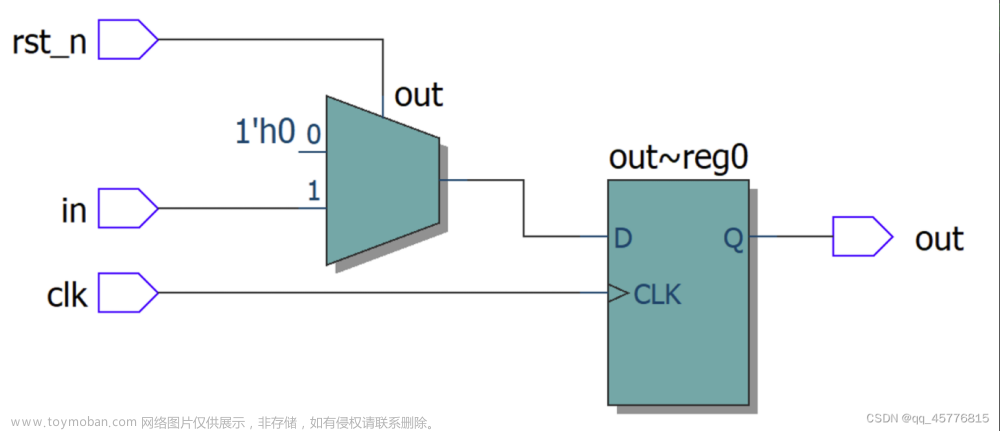

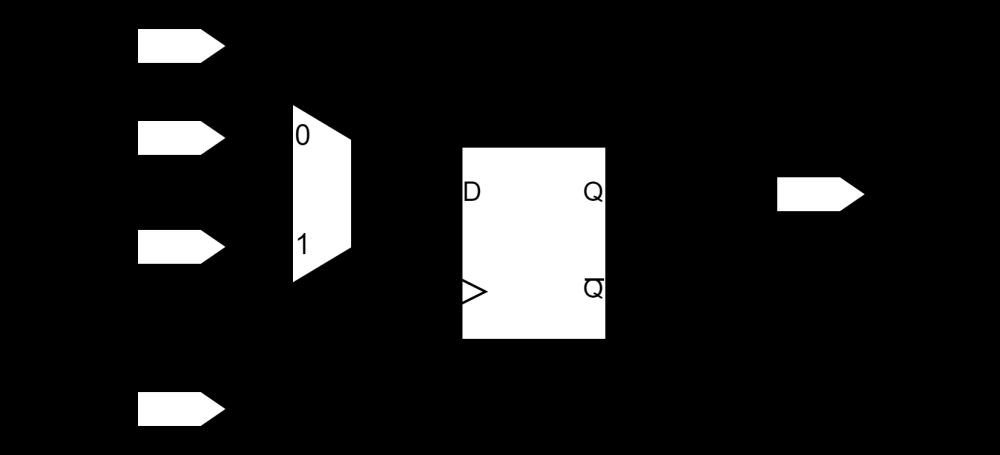

在流水线寄存器处理数据中,问题可能不大,不同级的寄存器的复位不在同一个时钟内激活,但老数据可以被新数据冲掉,若干时钟周期后,流水线就正常运转了。

但如果这是一条流水线寄存器用作控制路径,无法在同一个时钟周期内激活各个寄存器的复位,会导致信号错误,功能就不对了。

补充信息 名词解释:

1 扇入、扇出系数:

扇入系数是指门电路允许的输入端数目。

扇出系数是指一个门的输出端所驱动同类型门的个数。扇出系数体现了门电路的负载能力。

2 高扇出

高扇出指的是一个逻辑单元驱动的逻辑单元过多。常见于寄存器驱动过多的组合逻辑单元。至于驱动多少逻辑单元算过多,需要根据工艺,后端实现情况以及芯片本身类型来决定。一般来说如果驱动逻辑大于10K以上,算是比较多的了。

高扇出问题,通常是指用一个节点驱动多个下级逻辑器件,此问题会严重影响FPGA布线的稳定性,设计的时候要多加注意,此时采用的是复制寄存器策略。

举个例子:CLK为系统时钟,M为1MHz方波信号,由于M信号驱动的模块较多,所以M的扇出较多,为了减少扇出,用系统时钟采样,将M信号驱动7个D触发器,然后将7个D触发器的输出端分给7个模块,这样每个复制点(DUP0~DUP6)平均扇出变为原来的1/7,M的信号扇出变为7,这样就减少了每个信号的扇出,优化了逻辑,也提高了设计的整体性能。简而言之,就是将一路信号用D触发器和CLK将其分成两路信号,或者是更多路的信号,再让这些信号来驱动下面的各个模块。

高扇出有哪些危害?(从ASIC设计的角度讲的)

危害1:驱动能力下降,时序紧张

扇出过高也就是也就意味了负载电容过大,电路原理基础中,负载电容越大,充放电速度越慢,电平跳变所需要的时间增加,即驱动能力下降,时序更加紧张。面对高扇出的情况,后端工具通常会通过插入buffer增加驱动能力,然后插入buff又会增加延时,造成时序紧张。

危害2:不利于布局布线,会增加走线延时

高扇出的情况通常意味着负载end_point分布在block的各个位置。而驱动的start_point需要放置在相对应的中心位置,这就意味到start_point到end_points的走线延时较大,一旦时序紧张,后端工具需要花费很多时间去优化,往往结果还不理想。文章来源:https://www.toymoban.com/news/detail-825181.html

在遇到信号高扇出时三种思路,对于普通信号可采用①寄存器复制或者②设置max_fanout属性优化;而对于复位信号,可③加入BUFG优化。 文章来源地址https://www.toymoban.com/news/detail-825181.html

文章来源地址https://www.toymoban.com/news/detail-825181.html

到了这里,关于AMD FPGA设计优化宝典笔记(5)低频全局复位与高扇出的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!